高速先生成員--黃剛

看到這篇文章的題目,我相信大家心里都呈現(xiàn)出了這么一個場景:高速信號線在L20層,我只要把L19和L21層都鋪上完整的地平面,這不就滿足了高速信號線不能參考電源平面這條規(guī)則了嗎?這難道很難做到嗎?PCB的設(shè)計和疊層圖都給你截出來了,只要疊層夠,這一點都不難啊!

是的,高速信號線不能參考電源平面這一條規(guī)則是很容易滿足的,但是大家再認(rèn)真看看我們的題目是怎么說的?是“高速信號不能參考電源網(wǎng)絡(luò)”。難道這兩句話有區(qū)別嗎?當(dāng)然有,你們細(xì)細(xì)品味下,高速信號線不能參考電源平面其實指的只是高速鏈路中的差分線本身不能參考電源平面層,這是大多數(shù)工程師的理解。但是高速先生想說的是高速信號鏈路不僅僅只有走線,還有其他結(jié)構(gòu)!

沒錯,高速先生想給大家說的是過孔結(jié)構(gòu)!還是那句話,不讓走線參考電源平面,在層數(shù)充裕的情況下一般都能做到。但是高速信號的過孔完全不參考電源過孔,這個就真的不容易了。大家又會說了,那我的高速信號過孔旁邊都打地過孔,遠(yuǎn)離電源孔就好啦,不是也很容易做到嗎,你確定所有的地方都能做到嗎?

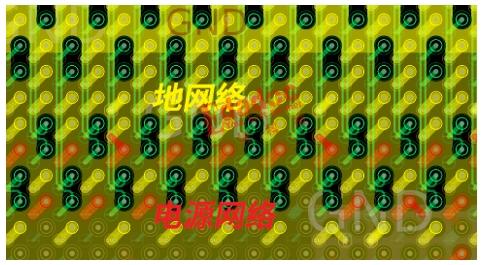

沒錯,例如在BGA的地方,真的就不是你說了算了!在一些大型的BGA,高速線的對數(shù)會比較多,從BGA的外圈一直延伸到BGA的內(nèi)圈,然后內(nèi)圈都存在著幾種包括core電源在內(nèi)的網(wǎng)絡(luò),也就是說,內(nèi)圈的高速信號pin旁邊極有可能存在著電源pin,那么有pin就有扇出,因此高速信號和電源的過孔基本上就無可避免的挨在一起了。

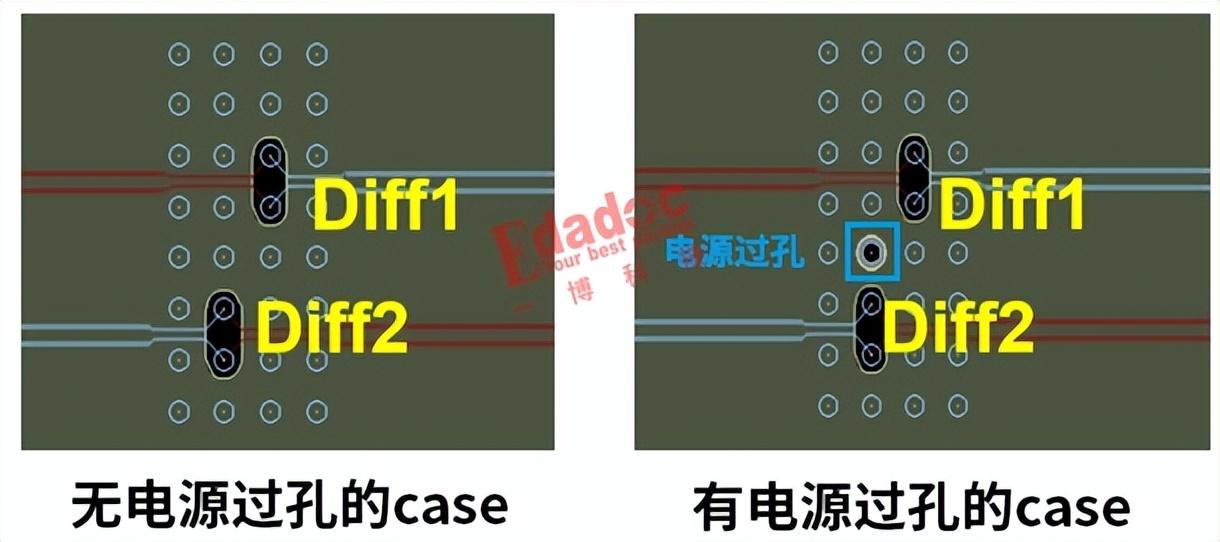

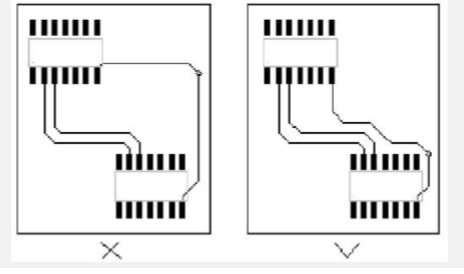

高速先生從來都不是只拋出問題的主,既然無法避開,只能接受,嘗試分析這種情況下到底對高速信號有什么影響。于是二話不說,高速先生就做了一些簡單但是能很好說明問題的測試板,去分析高速信號孔旁邊有電源孔對無源的影響。我們設(shè)計的測試DUT如下所示:

簡單的模擬一個1mm的BGA小陣列,上面各有兩對高速信號通過過孔連接,兩個case的區(qū)別為全是地過孔和有一個電源過孔在這個BGA小陣列里面。

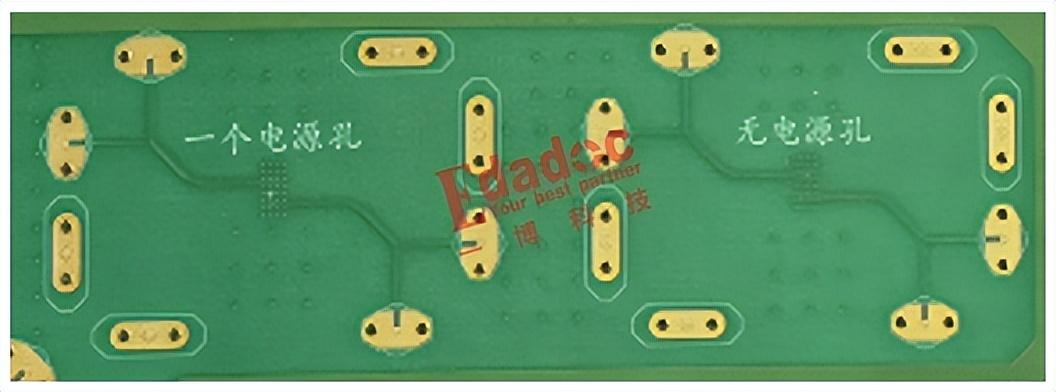

做出來的實物板就是這個樣子了!

那我們通過網(wǎng)絡(luò)分析儀進(jìn)行測試,看看兩種case下的無源性能的差異。

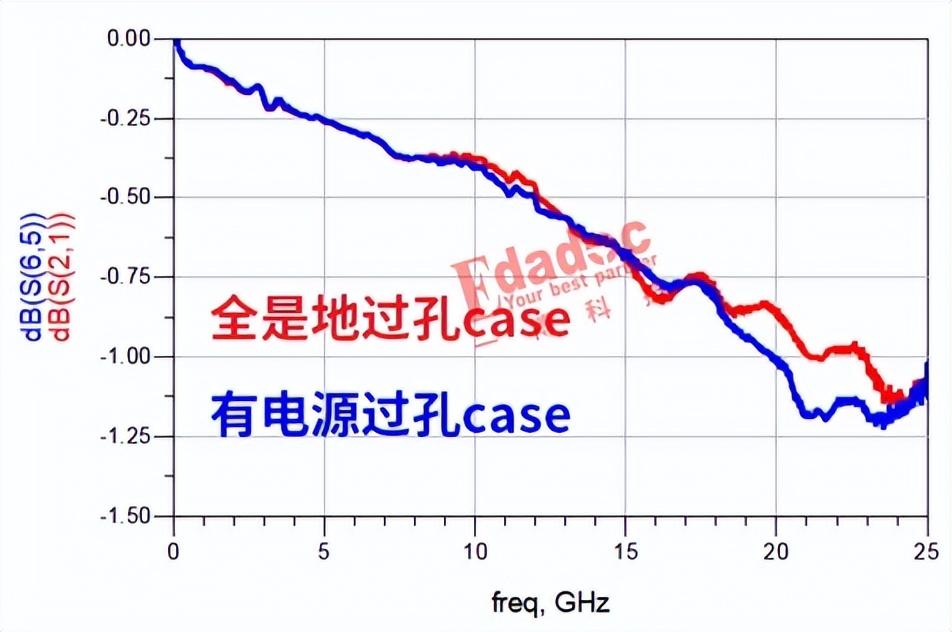

首先我們來看看DIFF1,也就是靠上的那一對,這一對相對DIFF2來說,地過孔保護(hù)得更好一點,我們來看看這一對的插入損耗的對比。

可以看到,DIFF1這對走線在兩種case下的差異其實不大,也就是到了比較高頻的時候(15GHz)才有一些差異,整體性能都是沒問題的。

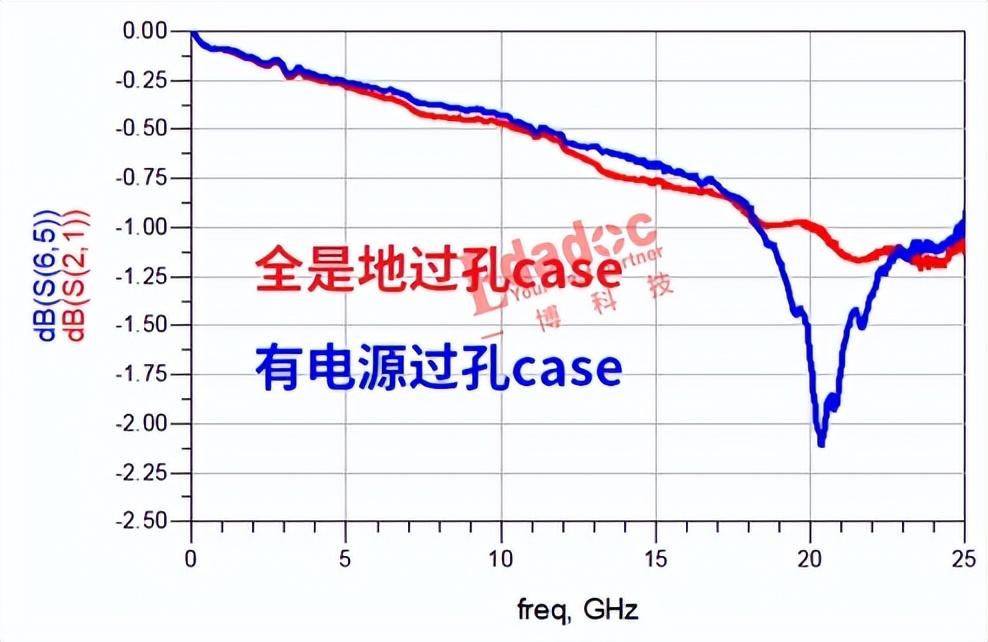

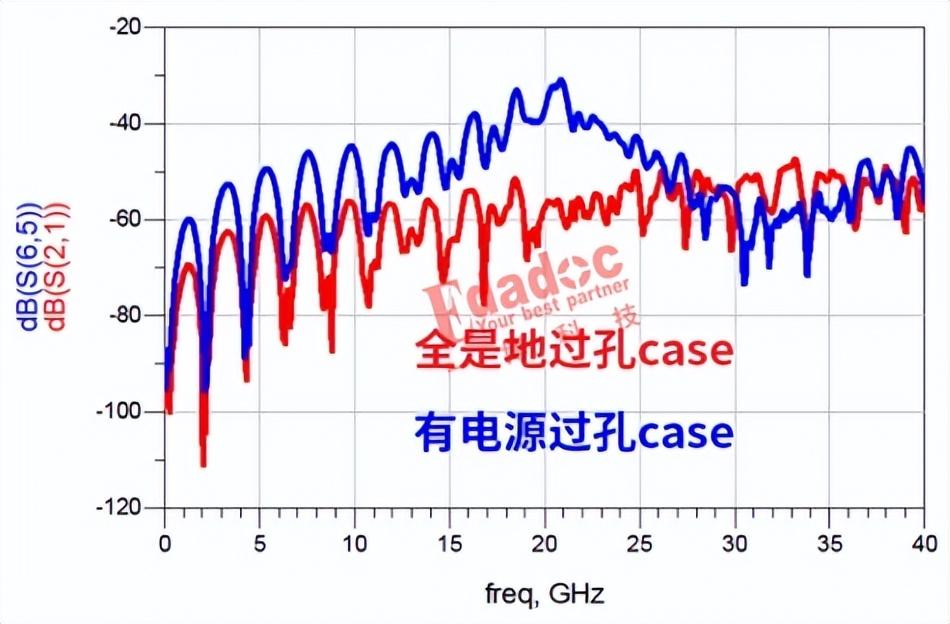

那重點來了,我們來看看被地過孔保護(hù)的沒那么好的DIFF2,尤其是有電源過孔在旁邊的這對信號,到底性能的差異是怎么樣的呢?結(jié)果如下所示:

全是地過孔下的DIFF2當(dāng)然沒問題了,但是能看到,有電源過孔在旁邊之后,這對DIFF2在20GHz有一些比較嚴(yán)重的諧振點,對信號質(zhì)量來說當(dāng)然是一種傷害了。也說明了DIFF2這對信號的的確確都參考到了這個電源過孔,性能隨之被影響到。

其實被影響到的不僅僅是信號質(zhì)量本身,我們來看看兩種case下DIFF1和2之間的串?dāng)_,也能夠發(fā)現(xiàn)明顯的差異。能看到在插損被影響到的這個頻段,串?dāng)_的惡化也是非常的嚴(yán)重,基本上串?dāng)_的量級差超過了20db。

最后再總結(jié)下本文的核心內(nèi)容哈,這篇文章其實主要是讓大家了解下除了PCB走線參考電源平面的影響巨大之外,在比較高的頻段下,高速過孔旁邊要是有電源過孔的話,同樣也會有影響。只不過頻段都去到了15GHz之后,沒做到這個頻率的產(chǎn)品的朋友們,也不用太過擔(dān)心。不過話又說回來,這個頻段其實也有很多產(chǎn)品涉及到了,因此根據(jù)具體設(shè)計的不同,也會給大家的產(chǎn)品帶來一定的風(fēng)險。雖然看起來在BGA區(qū)域,高速信號pin和電源pin挨著的事實無法改變,但是并不意味著我們就完全沒有改善的方法。相信只要大家發(fā)現(xiàn)了問題,也就一定會想出辦法去解決的哈!

問題來了:

面對BGA里面電源pin相鄰的現(xiàn)實,大家能想到什么方法來改善它對高速信號的影響呢?

審核編輯 黃宇

-

電源

+關(guān)注

關(guān)注

184文章

17585瀏覽量

249488 -

pcb

+關(guān)注

關(guān)注

4317文章

23006瀏覽量

396275 -

信號線

+關(guān)注

關(guān)注

2文章

168瀏覽量

21422 -

高速信號

+關(guān)注

關(guān)注

1文章

222瀏覽量

17676

發(fā)布評論請先 登錄

相關(guān)推薦

一文解析LISN人工電源網(wǎng)絡(luò)

高速電路電源分配網(wǎng)絡(luò)的時域分析與設(shè)計

高速電路電源分配網(wǎng)絡(luò)設(shè)計與電源完整性分析

非常實用的PCB布局布線規(guī)則,畫出美而高性能的板子

高速pcb布線規(guī)則有哪些

沒開玩笑!高速信號不能參考電源網(wǎng)絡(luò)這條規(guī)則,其實很難做到

降低RF電路寄生信號的八個設(shè)計規(guī)則

高速PCB信號走線的九大規(guī)則分別是什么?

PCB布線12條規(guī)則

高速PCB信號走線的九大規(guī)則

移軸相機(jī)對焦規(guī)則概述

高速電路板設(shè)計的十條規(guī)則

沒開玩笑!高速信號不能參考電源網(wǎng)絡(luò)這條規(guī)則,其實很難做到

沒開玩笑!高速信號不能參考電源網(wǎng)絡(luò)這條規(guī)則,其實很難做到

評論