作者介紹

在上期文章中我們介紹了ADC靜態參數測試的“測試適用性”和“硬件準備”,今天將為您介紹測試的“軟件配置”以及“開始測試和查看結果”的內容。

閱讀完本文,您將深入了解德思特ATX測試系統的強大功能和簡便操作,確保您的ADC性能測試既準確又高效。

一、軟件配置

軟件配置分為上位機與下位機兩個部分。下位機軟件已經預裝在德思特ATX測試系統的嵌入式計算機內,確保了即開即用的便利性。用戶僅需連接電源線和網線,按下開機按鈕,系統便會自動執行程序的啟動、硬件上電自檢和初始化過程。

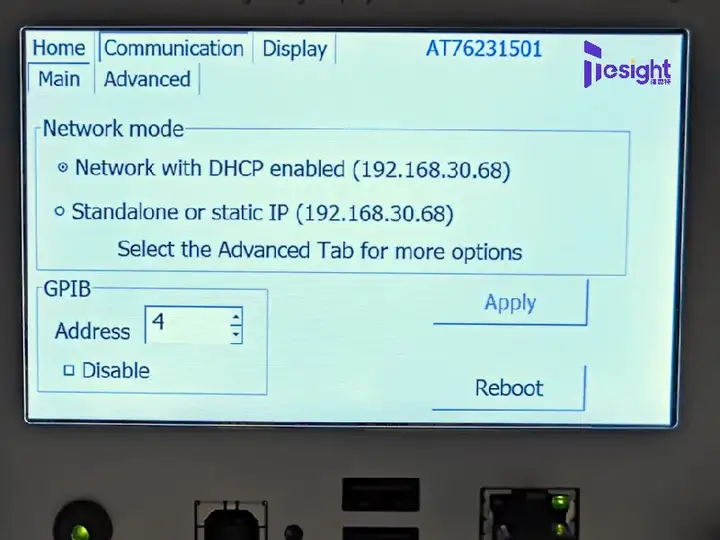

對于下位機軟件的配置,通常情況下,我們只需通過觸控屏調整網絡設置參數。最快捷的方式是啟用DHCP,讓系統自動獲取IP地址,用戶只需記錄下分配到的IP地址即可。如果需要更穩定的網絡環境,也可以手動設置一個固定的IP地址。

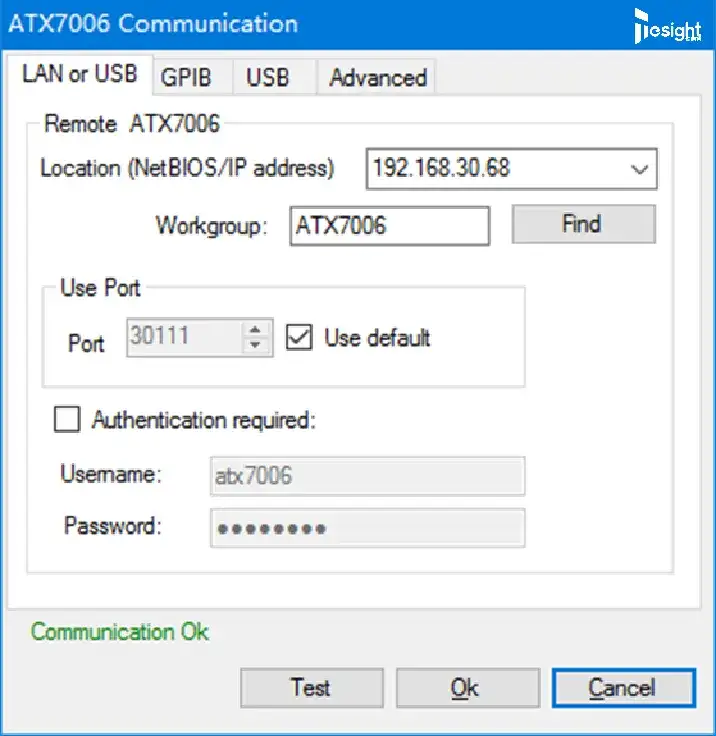

至于上位機軟件——ATView7006,也會作為標準交付內容之一提供給用戶,無需額外進行訂購。我們只需要找一臺裝有Windows系統的電腦,通過交付內容中配套的資料光盤進行安裝即可,如果電腦缺少光驅,也可以聯系德思特獲取數字版安裝包和其他資料。安裝后,我們進入軟件,在通訊配置面板中填入剛才確認到的IP地址,點擊“Ok”按鈕,即可完成與下位機的連接。

1.新建項目

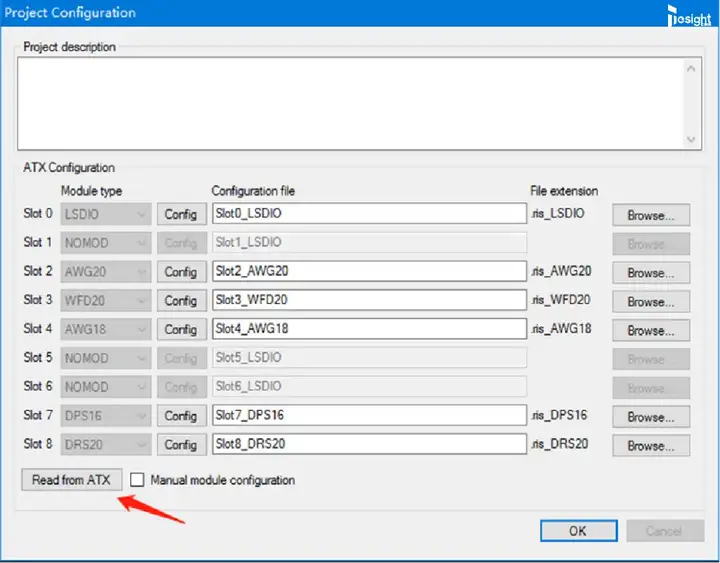

連上設備,我們就可以在軟件中執行新建項目。在創建好相關項目文件后,軟件會自動彈窗讓我們配置下位機有什么硬件模塊,一般情況下,我們并不需要手動配置,只需要點擊“Read from ATX”按鈕,上位機便會跟下位機進行通訊,自動獲取相關硬件信息。

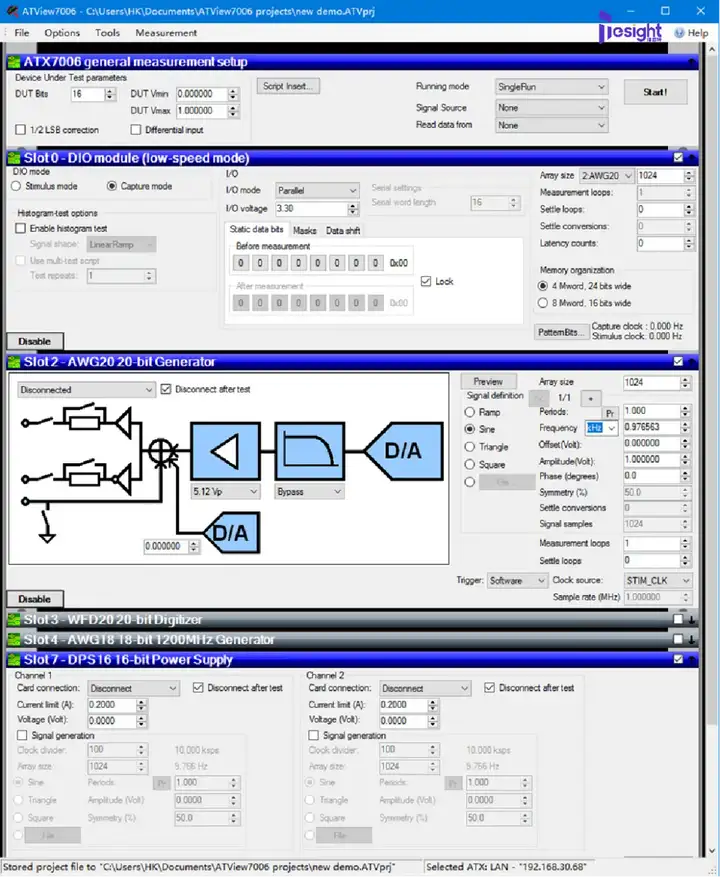

按“OK”按鈕后,軟件主界面便會自動增加每個硬件模塊對應的控制面板。我們也可以通過手動取消勾選的方式,來禁用部分在本次測試中不需要用到的硬件模塊。比如下圖中的WFD20數字化儀模塊(用于DAC測試)以及AWG18模塊(用于其它UUT的另一個AWG)的相關控制面板就已經被筆者禁用并折疊了。

2.測試概覽設置

完成項目文件的創建后,我們首先需要確認待測ADC的輸入情況,并告訴軟件我們打算用哪個模塊作為主要的信號輸出輸入模塊,來開展這次測試。

前文已經提到,我們作為示例的AD7671分辨率為16位,采用單端輸入,并且當前選用的輸入量程檔位對應的電壓是-5 ~ +5 V。因此我們將相關信息填入,如下圖所示。

其中值得一提的是,我們提供了一個1/2 LSB校正的選項,該選項適用于那些第一個LSB設計寬度只有其他LSB一半的ADC或DAC使用,開啟后會自動改變理想轉換曲線,并根據這種情況修正各種線性、非線性誤差的計算。經過我們核實,AD7671并不屬于這種情況,因此我們沒有實際勾選該選項。

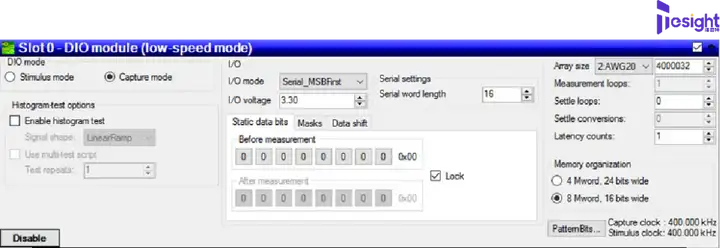

3.DIO模塊設置

我們按前面給出的軟件設置界面從上往下順序看,第二個設置板塊就是DIO模塊。在ADC測試中,DIO模塊扮演著關鍵角色:對外,它負責與ADC的通信,提供必要的時鐘信號、采集觸發信號、狀態配置等,并接收轉換后的數字碼;對內,它作為時序指揮中心,控制任意波形發生器(AWG)的更新時機。德思特ATX測試系統正是利用了DIO模塊的這些功能,精確滿足了斜坡測試對設備間時序協調的嚴格需求。

首先,我們確認我們的UUT通訊方式和電平,這些信息我們可以從AD7671的官方數據手冊中獲取。這里我們按手冊的要求,設置3.3V的IO電壓、MSB串行通訊的IO模式,以及16bit的字長。

在I/O大類下,我們還提供了3個設置選項卡:分別是Static data bits、Masks和Data shift。其中Static data bits用來控制8個靜態數字輸出口;Masks用于設置位掩碼,可以將某些指定位忽略或者置反,這對于某些具有特殊輸出規則的情況會派上用場;Data shift則是對測試結果按位左移或右移,主要適用于在最高位或最低位有無效位輸出的UUT。

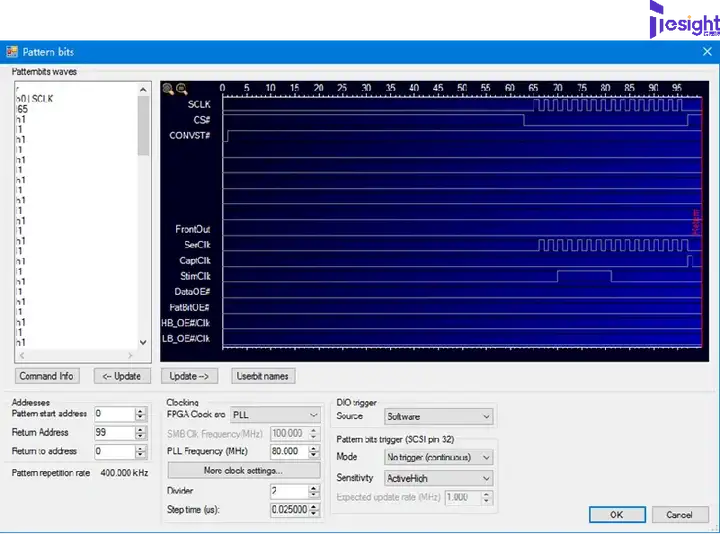

接下來是DIO模塊設置的重頭戲——時序設置部分。我們只需要點擊右下角的“Pattern Bits…”按鈕即可打開一個新的時序設置面板窗口。在這里,可以通過手動調節窗口內的時序圖,控制DIO模塊對內對外的各個信息。在本示例當中,這些信號包括了提供給ADC的SCLK時鐘信號、CS#使能信號以及CONVST#轉換開始信號;也包括了采集側的串行位移信號SerClk、采集鎖存信號CaptClk、AWG輸出時鐘信號SimClk。此外,我們還能通過調節PLL頻率以及分頻系數決定時序圖中每一格對應的時間長度。

其中,輸出到ADC的信號波形和PLL時鐘參數,可以由UUT數據手冊中關于時序部分的要求決定;而對內的各種觸發信號,則需要依據所選用AWG模塊對應的手冊說明內容決定。由于篇幅限制,此處不展開說明,相關手冊可向德思特索取。

有部分細心的讀者可能發現了:控制AWG刷新的StimClk信號時序位置晚于控制ADC開始轉換的CONVST#信號,這樣不會導致ADC本次轉換得到的是AWG的上一個輸出值對應的結果嗎?關于這個問題,我們實際上可以通過設置DIO模塊參數的“Latency counts”來解決,該參數設為1即表示,DIO需要提前多獲取一個周期的數據并將其丟棄,從第二個周期開始的數據才采用,并且后續軟件處理中,采回的數據會自動對應回AWG第一個周期的電壓。這個功能也適用于一些具有流水級或其他原因導致輸出具有周期延遲的ADC。

還有讀者可能會疑惑,StimClk信號是處于串行讀出階段的,這樣不會有相互沖突嗎?實際上這個也是一個優化的小技巧,根據UUT數據手冊的描述,ADC轉換實際上只在CONVST#信號到達之后的一段時間內進行,在其之后的串行數據讀出階段到下一次CONVST#信號到來之前,輸入電壓改變實際上并不會有任何影響,因此把StimClk信號放在串行讀出階段,可以顯著縮短整個時序周期的長度,從而提升最高測試采樣率和測試效率。

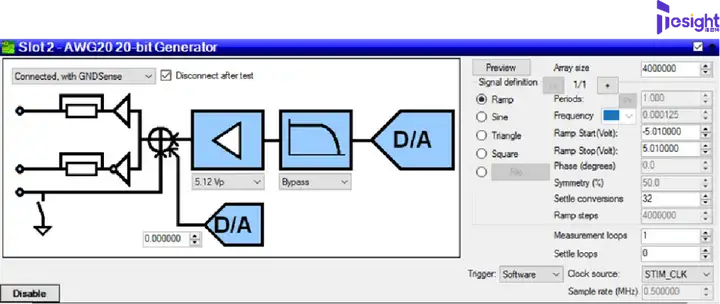

4.AWG設置

AWG部分的配置允許用戶定義測試激勵信號的具體形式和參數,并提供了調整信號前端處理工作參數的選項。配置界面的左半部分采用了簡化的原理圖形式,直觀展示了AWG的結構,這不僅幫助用戶理解其硬件功能,還清晰地指示了各個參數的實際影響,有效降低了用戶的學習門檻。

在這次示例當中,我們首先把左上角的連接方式,選為“Connected, with GND Sense”,從原理圖中的線路閉合情況就可以看出,該選項短路了50Ω輸出負載電阻,并且在反饋回路中,斷開了與輸出近端地的連接。換句話說,這種配置適用于UUT輸入電阻為高阻的情況,同時,將GND反饋線延伸至待測芯片附近,能夠更有效地針對實際的浮地問題進行補償反饋,從而提高測試的精度。這些配置確保了測試環境與UUT的實際工作條件相匹配,增強了測試結果的可信度。

此外,我們還可以從原理圖得知,AWG內部有兩個DAC:主DAC負責波形的產生,信號隨后會通過一個濾波器和一個調整幅值的放大器;而次DAC主要負責生成高精度的DC偏置信號,這兩種信號會相加到輸出信號當中。由于我們待測芯片的量程是-5 ~ +5 V,因此偏置DAC輸出值保持為0即可。關于放大器的設置,選項中的5.12 Vp指的是峰-峰值的一半,這意味著其輸出的最高電壓距離直流基線最多可以高出5.12 V,配合0V的DC偏置,實際可以產生-5.12 V到+5.12 V電壓。

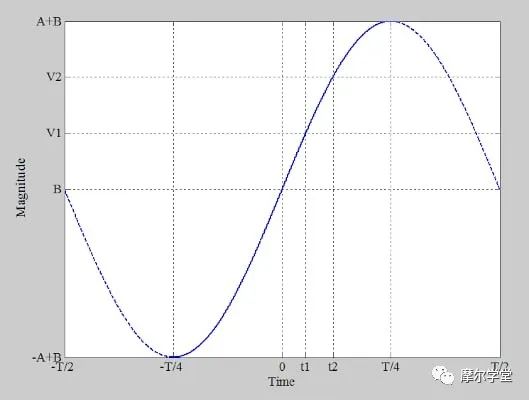

在配置面板的右側區域,我們可以找到一組專門用于描述信號波形的關鍵參數。正如我們往期文章所討論的,進行斜坡測試時,我們必須考慮到實際待測芯片的轉換范圍可能與標稱范圍存在細微差異。為了解決這個問題,我們設置的斜坡信號起始電壓應該稍低于待測芯片的最低標稱轉換電壓,而斜坡信號的終止電壓則應稍高于其最高標稱轉換電壓。基于這一考慮,我們將斜坡的起始電壓設定為-5.01 V,終止電壓設定為+5.01 V。這樣的參數配置使得對UUT實際轉換范圍偏差的測量成為可能,同時也能適應更多實際測量場景。

值得一提的是,在設計信號前端放大器時,我們選擇5.12Vp作為其中一個檔位,而不是直接采用常見的5Vp范圍值,正是出于同樣的考量。我們的設計目標之一便是在盡可能不影響輸出精度的前提下,允許波形的幅值略微超出標準ADC的轉換范圍,從而提供更大的靈活性和更高的測量精度。

此外,在配置面板的波形參數設置區域頂部,我們貼心地提供了一個預覽功能按鈕。用戶只需輕輕一點,即可快速查看預計輸出的波形圖樣。這一功能極大地幫助用戶確認幅值、周期等關鍵參數是否正確設置,從而有效預防由于配置失誤導致的UUT損壞。

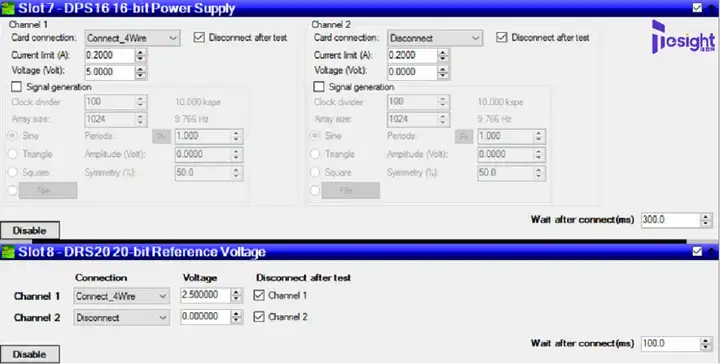

5.電源設置

電源部分的設置相對簡單。在本次示例中,DPS16模塊為UUT提供5 V供電,而同時DRS20模塊則負責輸出2.5 V參考電源,在操作上,用戶只需將這兩個電壓值分別輸入到對應模塊的輸出電壓設置欄即可。為了實現更高的電壓輸出精度,我們使用了4線制連接方式。如果條件允許,我們也強烈建議用戶同樣采用這種連接方式,以確保測試結果的準確性。

二、開始測試和查看結果

在設置好上述各種參數后,別忘了保存項目文件,這樣下次只需要導入本次的項目文件,即可快速完成配置,而無需重復以上步驟。完成配置后點擊最上方“ATX7006 general measurement setup”面板中的“Start !”按鈕即可開始自動化測試和分析流程。待到測試和分析過程結束,相關結果就會以彈窗形式呈現給用戶。

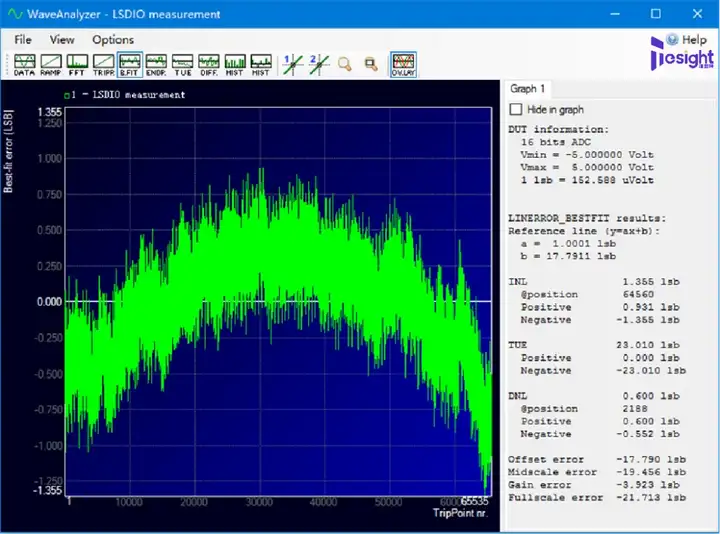

用戶可以點擊彈窗工具欄中的各個不同視圖按鈕,就可以輕松切換并獲取多種分析結果,比如點擊“B.FIT”視圖按鈕即可獲得最佳擬合直線下的INL、TUE、DNL等參數。從結果中,我們可以直接讀出該UUT測得INL為1.355 LSB,該數據符合官方數據手冊中標稱的±2.5 LSB Max (±0.0038% of Full Scale)。

同時還可以利用放大鏡、光標等內置工具,觀察數據圖的細節部分,從而進行更加深入的研究和問題定位。此外,不論是結果圖、計算結果還是原始采集數據,該軟件都提供了相應的導出功能,允許用戶工程師利用這些數據進行其他運算和處理分析工作。

總結

通過本文的介紹,我們深入了解了德思特ATX測試系統以及斜坡測試方法在ADC靜態參數測試中的應用。這一流程在顯著簡化傳統測試步驟的同時,確保了測試結果的精確性和可靠性。使用德思特ATX測試系統,工程師們可以輕松地完成從硬件準備到軟件配置的全過程,無需擔心儀器間的聯動問題,也無需進行復雜的編程和調試工作。

斜坡測試方法以其高效性和直觀性,被認為是獲取UUT靜態參數的理想選擇。通過德思特ATX測試系統的高度自動化和集成化,工程師可以快速地配置和執行測試,在直接獲取關鍵數據結果之余,也允許用戶導出數據進行額外處理。這種測試方法不僅提高了測試效率,還降低了人為錯誤的可能性,從而提高了整體測試質量。

總體而言,德思特ATX測試系統結合斜坡測試方法,為ADC靜態參數測試提供了一種高效、精確且用戶友好的解決方案。這種一體化的測試裝備和創新的測試流程,無疑將幫助工程師們更加專注于產品設計開發的核心環節,加快產品上市時間,同時確保產品的高質量和性能。對于想要深入了解德思特ATX測試系統或相關的ADC測試方法,以及尋求更多相關資料和技術支持的讀者,我們誠摯邀請您聯系德思特。我們的專業團隊將為您提供詳細的產品信息、個性化的咨詢以及全方位的技術支持,確保您能夠充分利用我們的解決方案,提升您的測試效率和產品質量。

審核編輯 黃宇

-

dac

+關注

關注

43文章

2215瀏覽量

190240

發布評論請先 登錄

相關推薦

高速 ADC/DAC 測試原理及測試方法

以helloworld程序為例,講一下如何編譯和測試qt程序?

泰克電源全流程測試解決方案的應用分析

ADC靜態測試全流程:以斜坡測試為例(二)

ADC靜態測試全流程:以斜坡測試為例(二)

評論