從理論上講,碳化硅 (SiC) 技術比硅 (Si) 具有優勢,這使得它看起來可以作為電力電子中現有 MOSFET 的直接替代品。這在一定程度上是正確的,但只要關注該技術與硅的不同之處,以及如何優化電路技術(例如軟開關),超越硅的實際應用,就可以從 SiC 中獲得更多收益。

與硅相比,SiC 的帶隙更寬,因此擊穿電壓和電子遷移率更高,從而降低了導通電阻。與硅相比,SiC 的開關速度也更快,從而提高了效率,并能夠設計出體積更小的電力電子系統。SiC 的熱導率也明顯高于硅,因此可以設計出在更高溫度下運行的電力電子設備,而不會犧牲性能或可靠性。

基于傳統硅超結MOSFET的電路只需考慮簡單的軟開關技術,但高典型工作頻率意味著SiC需要仔細分析何時和何處出現損耗。從而,該分析可以導致新穎解決方案,避免了傳統MOSFET電路設計固有的損耗。

例如,SiC等寬禁帶技術的一個關鍵優勢是能夠為給定通態電阻保證更高的擊穿電壓。這允許使用比體硅器件所需更薄的漂移層,從而比所需厚的層的體硅器件具有更低的電阻。同時,晶體格子的組成提供了更高的載流子遷移率。結果是更高的導電性。

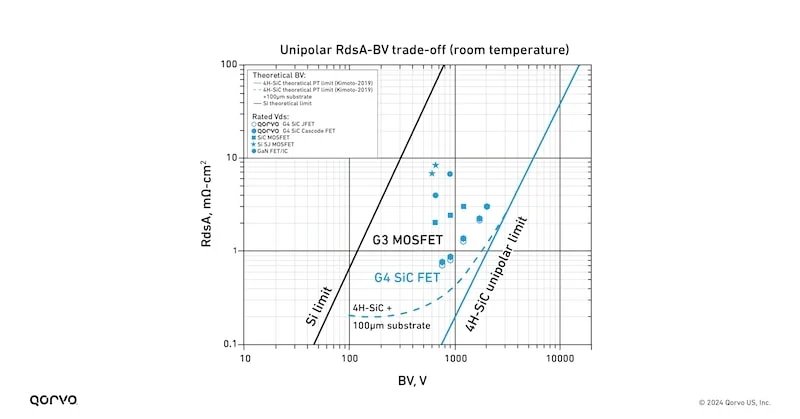

圖1

圖1結型場效應晶體管(JFET)是最好的選擇來最小化漏源電阻。在MOSFET中,載流子必須通過p基(p井)區域的表面通過MOS界面處的電阻性反轉通道進入n型漂移區域。然而,在JFET中,沒有這樣的反轉通道。通過使用高體多數載流子遷移率,JFET接近于通態電阻的理論限制,相比擊穿電壓而言。Qorvo的SiC JFET器件允許與MOSFET設計相比,具有更大的擊穿電壓安全裕度和約一半的通態電阻的晶體管設計。

傳統上,僅使用耗盡型JFET會帶來電路設計挑戰。作為一個常開設備,它需要負電壓完全關閉。然而,SiC MOSFET具有低閾值電壓,因此在真實電路中,負門電壓并不少見。應用負電壓可以防止在溫度極端時發生意外開啟,因為閾值電壓可能低于名義水平。

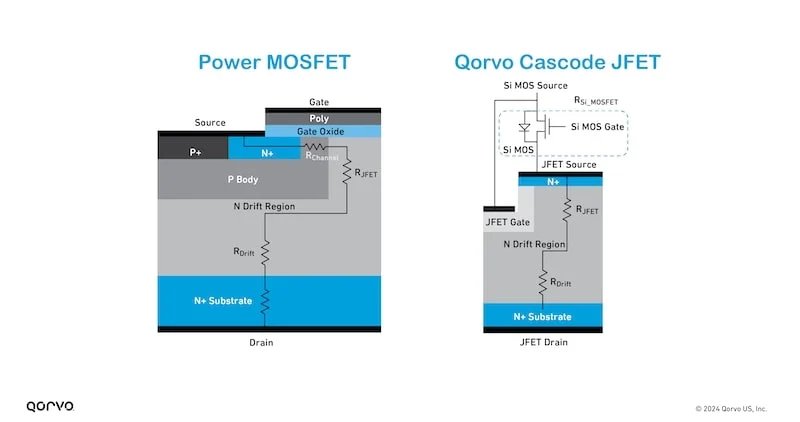

Qorvo的解決方案將SiC JFET與低壓硅MOSFET結合在串聯結構中,其中SiC JFET的柵源電壓是Si MOSFET漏源電壓的反向。該串聯結構如圖2所示。在串聯配置中,外部柵驅動器控制低壓Si MOSFET漏源電壓,間接驅動高壓SiC JFET。這種串聯配置為習慣于使用硅超結MOSFET的工程師提供了熟悉的控制方式。MOSFET的較低工作電壓對該設備對的整體通態電阻的貢獻不到10%。為了方便集成,Qorvo以單個封裝提供此配置。

圖2

圖2串聯結構通過Si低壓MOSFET控制開關,將控制邏輯與高壓JFET分離。這種分離提供了優化柵控電壓范圍和柵電荷以實現低壓Si MOSFET的機會,同時不損害SiC JFET的全部性能優勢。

與傳統SiC MOSFET通常需要高達18V的柵電壓來完全激活器件并獲得低通態電阻的全部優勢相比,串聯架構允許更低的最大柵控電壓,并且無需負電壓用于關斷狀態。電壓范圍的縮小減少了柵電荷約50%(從18V / -4V到10V / 0V),在輕負載下,特別是對于軟開關應用,減少了開關過程中的損耗。

采用JFET結構的SiC轉換器大大縮小了芯片尺寸。Qorvo的器件與硅超結器件相比,具有近十倍的芯片面積減小,但具有相同的功率處理能力。SiC的熱導率和優越性能抵消了由于芯片尺寸顯著減小而帶來的熱阻增加。通過使用銀浸滲來增加散熱片連接的熱導率,與傳統焊料相比,提供了6倍的熱導率改進,以抵消進一步增加的熱阻。

將串聯結構應用于SiC JFET進一步改善了效率,通過減小影響硅超結器件和SiC MOSFET的雜散電容提高了密度。較低的雜散電容使開關頻率高于硅器件甚至SiC MOSFET實際可行的范圍。

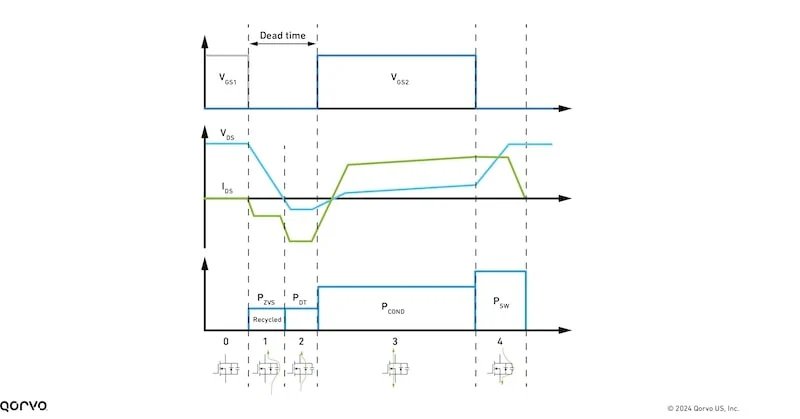

圖3

圖3這些優勢在軟開關電路結構中最為明顯。盡管使用硅器件的軟開關技術解決了開啟和關閉階段的一些明顯損耗來源,但最新一代SiC晶體管的快速開關能力解決了通常被忽視的更微妙問題。

許多基于硅器件的電路采用零電壓開關(ZVS)。它的主要目的是在電流開始自由通過晶體管通道之前,減少漏源電壓(IDS)和漏源電壓(VDS)之間的電壓,以消除開啟開關損耗。輸出電容(即漏源電容和柵與漏之間的電容之和)通常在上一個周期中關閉設備時完全充電到直流鏈路總線電壓,并在下一個ZVS開啟事件期間重新用于負載以避免損耗。

傳統Si器件使用ZVS開啟可能導致開關周期中的死時間長達300ns,這是由于硅器件的高輸出電容。對于500kHz(2μs周期)的開關頻率,開啟和關閉轉換期間的300ns死時間占占空比的30%。

與Si MOSFET相比,SiC JFET具有更低的輸出電容,清除時間較短,特別是在漏源電壓偏差較低的情況下,Si MOSFET的輸出電容會顯著增加。硅超結器件在低漏源電壓偏差下的CV曲線具有較強的非線性,這導致半橋拓撲中在總線電壓和0V附近的高壓過渡時間。這縮短了ZVS所需的死時間,可以用于更高頻率的操作或更多功率傳遞到負載。

由于較長的電壓過渡時間和相對較高的關斷開關損耗,使用Si器件設計的ZVS電路的開關頻率限制在150kHz以下。借助Qorvo SiC FET的快速開關能力,開關頻率邊界被推動到500kHz以上。與開啟開關損耗類似,如果盡量減小關斷期間電流下降和漏源電壓上升之間的重疊,效率將得到改善。

但是,隨著開關速度的增加,電磁干擾變得更具挑戰性。設計師必須在設計階段盡早地,通過小心減少PCB上的有意義的電流換位環的寄生參數,充分利用SiC的快速開關能力。但是,在考慮到安全要求(例如間隙放電等)時,優化的空間有限。一旦電路設計完成,有兩種常見的方法可以進一步微調關斷漏源電壓尖峰和諧振。

一種方法是使用高柵電阻(Rg)來減慢器件開關速度。一種更有效且高效的方法是使用嗡嗡聲電路,如圖4所示,其中使用低柵電阻。換句話說,使用小的柵電阻來允許SiC器件快速開關,并使用嗡嗡聲RC來控制VDS峰值和諧振。器件嗡嗡聲電容Cs提供VDS峰值過沖控制,而Cd通過靠近快速開關半橋來最小化功率回路寄生電感。Rs和Rd為VDS諧振提供阻尼。

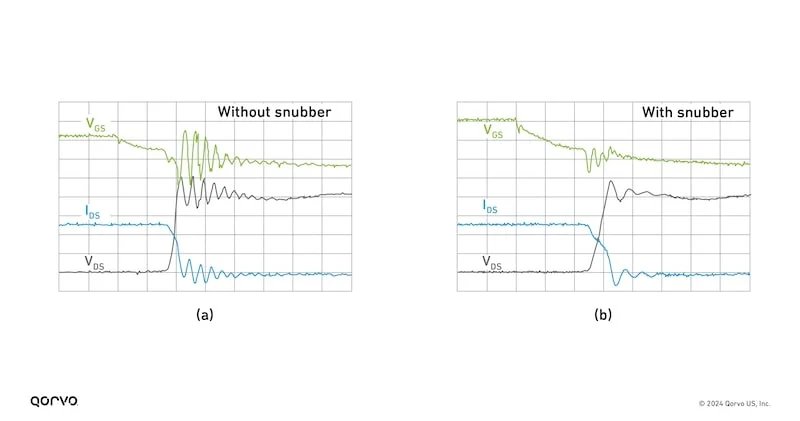

圖4

圖4一個常見的誤解是使用嗡嗡聲電路效率低下。對于半橋拓撲結構(通常用于LLC或PSFB等ZVS應用),與使用高柵電阻相比,使用嗡嗡聲電路的效率要高得多,因為額外的漏源電容在開啟階段不會產生任何開啟損耗。在關斷dv/dt階段,自由輪設備的位移電流將進一步減少已主動關斷的設備的關斷電流,從而減少電壓和電流的重疊,從而大大減少關斷損耗(Eoff)。位移電流水平由方程I = C*dv/dt確定。C是等效輸出電容,包括器件輸出電容(Coss)和并聯在器件漏源之間的額外嗡嗡聲電容Cs。

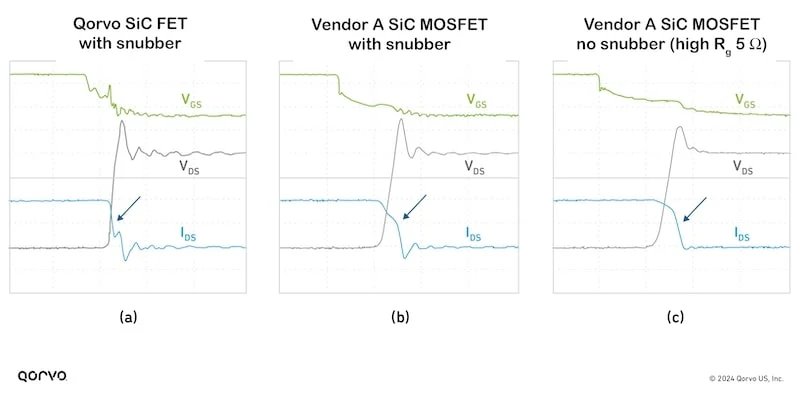

圖5

圖5具有額外嗡嗡聲電容的漏源和高dv/dt(即低柵電阻)時,位移電流將更高。這樣,留給活動關斷設備與VDS重疊的電流就更少,從而減少關斷開關損耗。這種方法允許我們在不犧牲太多器件開關速度的情況下控制VDS的諧振和峰值,而如果我們使用高Rg解決方案,可能更多地使用設備開關速度。圖5顯示了帶有和不帶嗡嗡聲電路的雙脈沖測試關斷波形,直觀地顯示了使用低柵電阻的嗡嗡聲電路可以大大減少電壓和電流的重疊,從而減少了關斷開關損耗。

使用嗡嗡聲電路的節省強調了在使用SiC時利用軟開關電路結構來最大化效率的重要性。在硬開關設計中,嗡嗡聲電路的好處較小,因為在開關周期中從關斷周期中存儲在Cs中的能量通常作為熱量浪費在下一個開啟周期中的器件通道中。然而,即使在使用嗡嗡聲電路時存在開啟損耗的懲罰,總體開關損耗(即開啟和關斷開關損耗的總和)仍遠低于僅使用高柵電阻在滿負荷(即設備額定電流)下的情況。

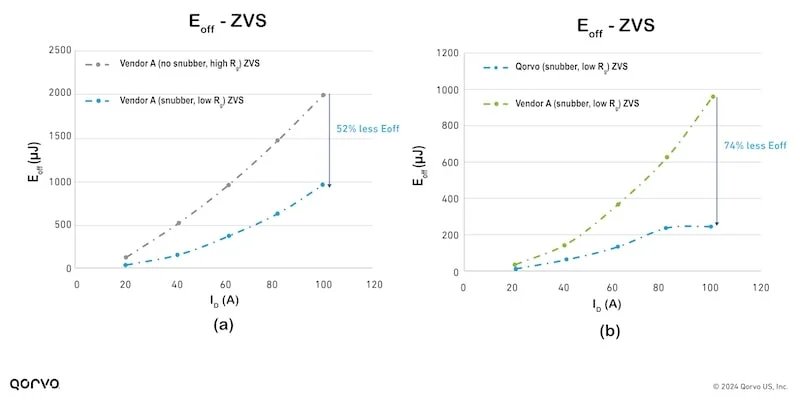

圖6

圖6參考圖5中用800V總線電壓和100A負載電流進行的雙脈沖測試的波形,圖6總結的分析顯示,添加嗡嗡聲電路可以使來自A供應商的SiC MOSFET模塊的損耗減少50%。

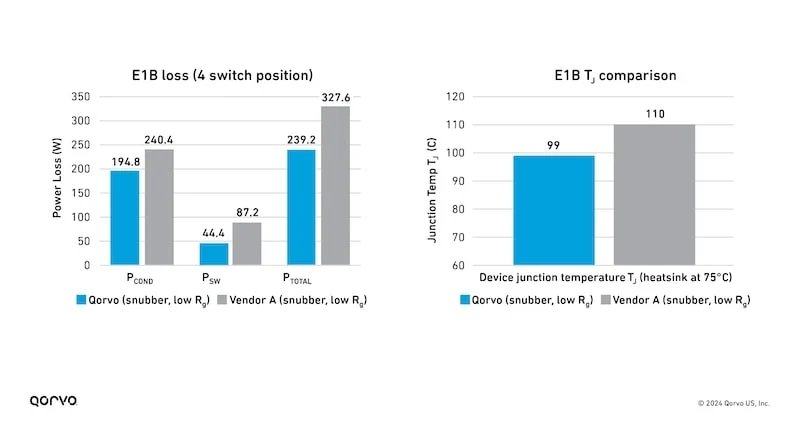

使用Qorvo的基于JFET的器件與嗡嗡聲電路相結合,可以額外減少74%的關斷開關損耗。這使得可能將開關速率提高三倍,并減小外部被動元件的尺寸。引用50 kW PSFB(相移全橋)的仿真,關斷開關損耗減少74%還有助于降低10%的結溫(圖7)。最終,更好的熱性能導致更小的散熱器和冷卻結構,兩者合起來可減小轉換器體積。

圖7

圖7盡管SiC在功率電子設計中相對于硅具有固有優勢,但重新評估設備選擇和電路拓撲以獲得最佳性能。結合嗡嗡聲電路和Qorvo SiC串聯JFET配置的內在低漏源電阻,快速開關能力可以大大提高ZVS軟開關應用的效率和功率密度。

-

電阻

+關注

關注

86文章

5467瀏覽量

171654 -

MOSFET

+關注

關注

144文章

7088瀏覽量

212713 -

SiC

+關注

關注

29文章

2760瀏覽量

62451 -

碳化硅

+關注

關注

25文章

2692瀏覽量

48881

發布評論請先 登錄

相關推薦

用碳化硅(SiC)重新思考軟開關效率

用碳化硅(SiC)重新思考軟開關效率

評論