導語:

據統計,靜電放電(Electro-Static Discharge, ESD)造成的芯片失效占到集成電路產品失效總數的38%。完好的全芯片ESD防護設計,一方面取決于滿足ESD設計窗口要求的優質ESD器件結構,另一方面全芯片ESD防護網絡的考量也格外重要。

正文:

靜電放電造成的CMOS IC損壞已是眾所周知的芯片可靠性問題之一。隨著工藝水平的不斷進步,先進的工藝制程嚴重降低了深亞微米CMOS IC的靜電防護能力,給ESD器件結構的設計帶來了更大的挑戰。因此,設計滿足ESD窗口的優質ESD器件成為重要的研發方向之一。然而,全芯片ESD防護網絡的設計也格外重要。

一般而言,為加強ESD防護能力,大多數IC會在輸入PAD、輸出PAD和電源PAD周邊做上ESD防護電路。但有時即使在輸入、輸出和電源軌上已有適當的ESD防護器件或電路,IC內部電路仍然會因ESD測試而發現異常損傷問題,而保護內核電路的ESD器件卻沒有損壞。因此,全芯片ESD防護設計必須要注意全芯片防護網絡架構的設計,才能夠真正避免內部電路發生異常損傷。下面列舉IO測試和Pin to Pin兩種測試下的內部電路異常損壞情形和具體解決辦法。

1、IO腳的測試

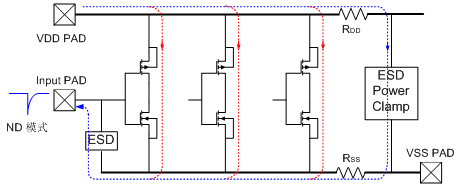

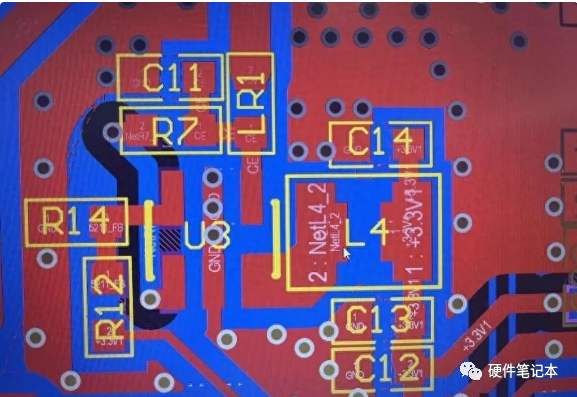

如圖1所示,在ND模式下,輸入PAD有一負脈沖,VDD PAD接地。因VSS浮接,原本落在輸入PAD與VDD線之間的ESD負電壓,轉變成落在VDD與VSS電源線之間,該ESD電壓應該經ESD Power clamp和Input PAD的ESD旁路泄放。但是,若IC內的VDD與VSS電源線散布極長,該ND模式的ESD電壓會經由VDD與VSS電源線而進入IC的內部電路中(紅色路徑),導致IC內部電路的ESD損傷。

圖1 IO腳的測試

圖1所示情形說明了電源線過長時,雜散電阻/電容會降低ESD箝位電路的防護效果。因此,解決辦法是除了在VDD和VSS PAD放置ESD power clamp以外,在電源線間適當的地方加入VDD與VSS的ESD power clamp電路,能夠協助大幅提升輸入/輸出腳的ESD耐壓能力。

2、Pin to Pin的測試

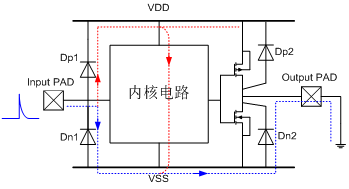

如圖2所示,一個正ESD電壓加到IC的某一輸入腳,IC的另一輸出腳相對接地。此時該ESD脈沖應該利用輸入腳上的ESD防護二極管Dn1雪崩擊穿來旁通ESD電流到浮接的VSS電源線上,再經由輸出腳NMOS的寄生二極管Dn2流出IC到地。但是,在Dn1雪崩擊穿前,該ESD電流會先經由輸入腳的二極管Dp1對浮接的VDD電源線充電,而浮接的VSS也會因輸出腳接地而被Dn2偏置在接近地的電壓準位。這樣,該ESD脈沖會轉變成落在VDD與VSS電源線間的ESD過壓。因此,ESD電流會隨著VDD與VSS電源線而進入IC的內部電路(紅色路徑),造成IC內部損傷。

圖2 Pin to Pin的測試

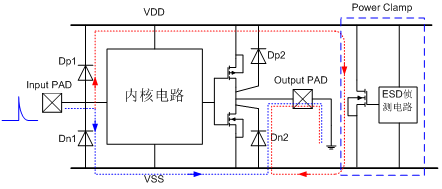

如圖2所示的情形說明了,出現在IC的輸入腳或輸出腳上的ESD電壓可以轉變落在VDD和VSS之間,因此,要能夠有效地保護到整顆IC不受ESD損壞,必須在IC的VDD與VSS電源線間做一有效的ESD防護電路。一般而言,VDD與VSS電源線之間會放置大尺寸的GGNMOS元件,但是,即使有該NMOS元件當做ESD防護元件來旁通ESD放電電流,IC的內部電路依然會出現ESD損傷的問題。其原因是IC的內部電路通常使用最小間距,因而內部電路元件因具有最小尺寸會先于電源線間的GGNMOS擊穿導通,因此,GGNMOS元件不能夠有效地來保護IC的內部電路。解決辦法是使用ESD偵測電路,使VDD到VSS間的NMOS具有更低的導通電壓,如圖3所示。

圖3 ESD網絡改進后的Pin to Pin測試

-

芯片

+關注

關注

450文章

49636瀏覽量

417144 -

ESD

+關注

關注

48文章

1977瀏覽量

172229 -

靜電放電

+關注

關注

3文章

275瀏覽量

44546

發布評論請先 登錄

相關推薦

網絡播放器端口防護

電路級靜電防護設計技巧與ESD防護方法

【轉】電路級靜電防護設計技巧與ESD防護方法

電路級靜電防護設計技巧與ESD防護方法

探索ESD防護器件的原理及選用

USB3.0接口的ESD防護設計

如何進行ESD防護?

ESD防護的PCB設計準則

IPv6防火墻設計系統 構建全方位的安全防護網絡

全芯片ESD防護網絡

全芯片ESD防護網絡

評論