導語:

柵極接地NMOS是一種廣泛應用的片上ESD器件結構,為達到特定ESD防護等級,一般會采用多叉指版圖形式來減小器件占用的芯片面積。但是,多叉指柵極接地NMOS在ESD應力作用下,各個叉指難于做到均勻開啟,無法達到預期ESD防護等級。本文從版圖、器件結構、觸發技術等角度介紹一些改善多叉指MOSFET靜電防護器件電流泄放均勻性提升器件靜電防護魯棒性的技巧。

正文:

據文獻報道,大面積叉指狀靜電箝制器件靜電防護能力的提高并不與器件面積大小或器件叉指數目成正比。其根本原因是各個寄生三極管BJT的非均勻觸發引發LDMOS器件中的電流聚集效應,導致了器件未能充分發揮防護潛能而過早失效。現有的改善多叉指MOSFET靜電防護器件電流泄放均勻性的技巧包括版圖布局、器件優化和增加觸發電路等。

1、版圖布局技巧

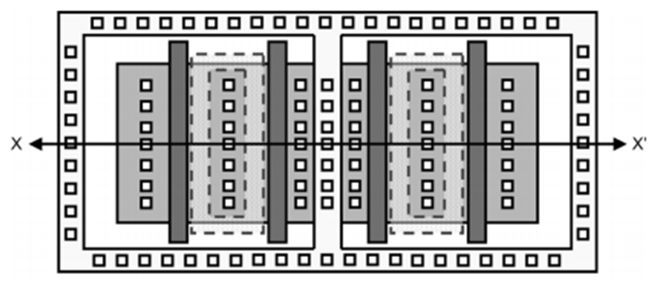

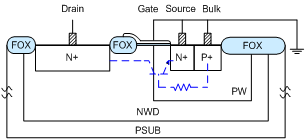

在傳統多叉指LDNMOS器件的布局上,造成非均勻開啟環境的主要原因來自寄生BJT基極電阻的差別。如圖1所示為版圖布局的改進,緊貼每一個NMOS管的源極插入一個P+型擴散區,可以使得多叉指NMOS器件中的每個橫向NPN BJT的寄生電阻幾乎接近相同。由于各個叉指具有幾乎相同的基極電阻,其橫向寄生NPN BJT可以幾乎同時被觸發開啟。但是需要注意的是,各個源區由于P+擴散區的植入,布局的尺寸會有所增加;此外,如果各個叉指的襯底電阻因此而變得太小,那么所有寄生橫向NPN BJT難以迅速開啟保護內部電路器件的薄柵氧化層。

(a)布局的頂視圖

(b) X-X’方向截面圖

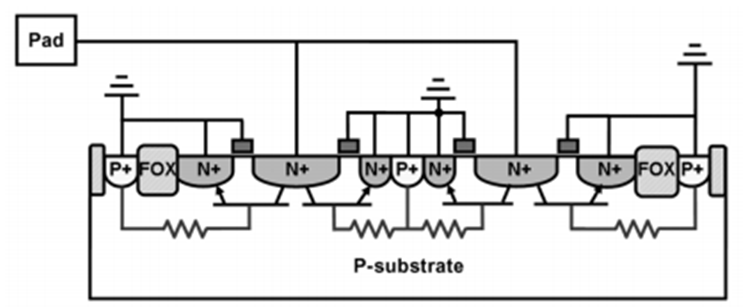

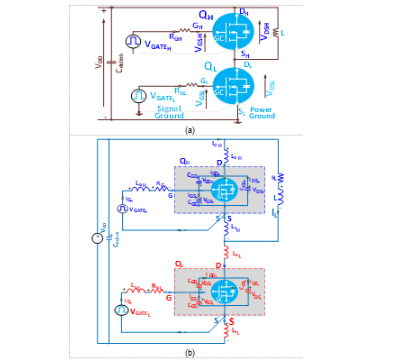

2、柵極耦合技術

圖2為一種采用柵極耦合技術的靜電防護電路。通過不斷調試電容和電阻的大小,在高ESD應力下,可以將一個合適的電壓耦合到NMOS和PMOS的柵極,從而降低NMOS和PMOS的開啟電壓,大尺寸多叉指NMOS器件的非均勻開啟問題可以通過柵極耦合技術得到克服。

然而對于NMOS和PMOS,如果耦合到柵極的偏置電壓較高,會引起更多的溝道電流和較高的電場,使薄柵氧化層易于被破壞。所以,其ESD防護的魯棒性會迅速減低。柵極耦合ESD防護電路必須仔細設計和優化,以防止ESD防護級別會因為柵極過驅動而下降。

圖2 利用柵極耦合技術的ESD防護電路

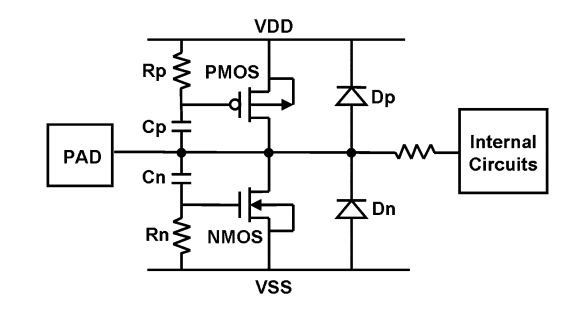

3、襯底觸發技術

圖3是采用襯底觸發技術的ESD防護電路,同樣通過調整電阻和電容,可以為橫向寄生NPN BJT提供一個合適的襯底觸發電壓,降低NMOS管的觸發電壓,從而提升NMOS管的開啟均勻性。

與柵極耦合的設計相比,襯底觸發技術直接有效地提高了寄生BJT管的基極電壓,因此,可有效防止溝道電流的產生和柵氧化層的過壓問題。所以,襯底觸發技術能持續提高ESD防護器件的ESD魯棒性,而不像柵極耦合技術那樣,在柵極過驅動的情況下出現魯棒性降低。當然,該技術需要額外的版圖面積來實現電容、電阻構成的觸發電路。

圖3 利用襯底觸發技術的ESD防護電路

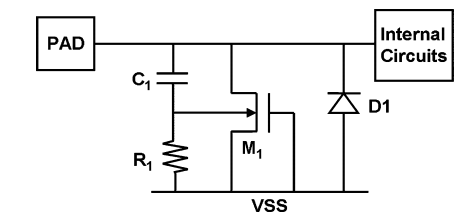

4、多米諾型觸發技術

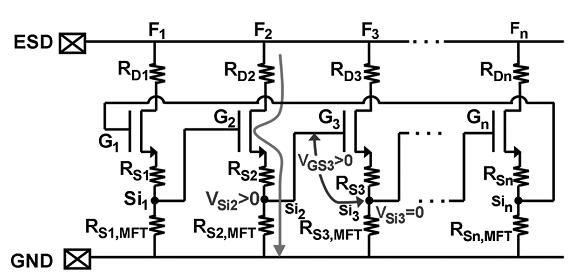

如圖4所示為多米諾型多叉指器件觸發技術。圖中是漏極/源極的鎮流電阻。每個叉指NMOS管中的電阻用來給相鄰叉指的柵極提供偏置電壓。多米諾型結構中任意一個叉指被觸發后,其它叉指會像多米諾骨牌一樣,依次開啟。假設F2指最先開啟,那么,最開始的ESD電流將流過電阻,形成,抬高F3柵極的電壓。因此,根據柵極耦合效應,F3中內在的寄生BJT能夠被觸發從而導通。以此類推,依照相同的原理,源極的信號不斷向下傳遞,使下一個管子觸發。最終多指器件呈現整體性導通狀態,從而高效泄放ESD電流。此電路中電阻若設計得當,可達到預期效果,但其布局實現較為復雜。

圖4 多米諾型多叉指器件的等效電路圖

5、襯底自觸發技術

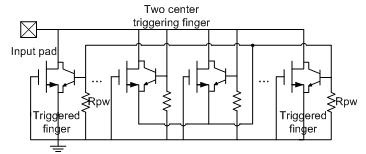

如圖5所示為襯底自觸發技術ESD防護電路的等效電路圖。此改進的多叉指器件結構中間兩個管子與兩邊的其它管子結構不完全相同,它利用中間兩個叉指先行開啟提供的電流作為襯底觸發電流來啟動其它叉指。除了中間叉指的源極與其它叉指寄生BJT的基極相接、而不是傳統接地以外,中間兩個叉指的尺寸大小、基本結構與傳統的對稱多指柵極接地MOS布局基本相同。

圖5 襯底自觸發ESD防護電路的等效電路圖

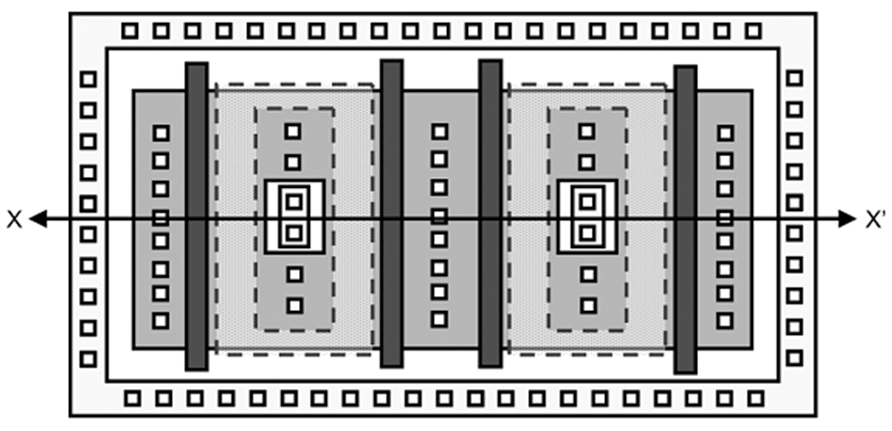

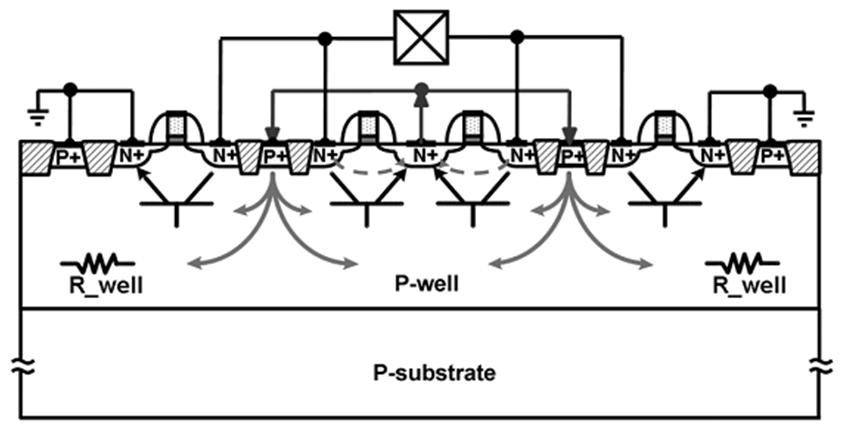

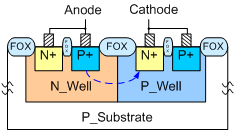

圖6(a)(b)分別為采用襯底自觸發技術的柵極接地NMOS結構版圖和X-X’方向的剖面圖,此技術通過在各個叉指的漏極插入P+擴散區作為被觸發襯底的節點。中間叉指的源極與這些被觸發襯底節點相連接。在布局上,由于漏極區域一般要比源極區域大一些,插入P+擴散區并不會增加整個布局尺寸。

柵極接地NMOS結構襯底自觸發技術,(a)版圖布局

柵極接地NMOS結構襯底自觸發技術 (b)X-X’方向剖面圖

-

三極管

+關注

關注

142文章

3548瀏覽量

120491 -

MOSFET

+關注

關注

142文章

6836瀏覽量

211324 -

靜電防護

+關注

關注

11文章

173瀏覽量

47306

發布評論請先 登錄

相關推薦

影響電路魯棒性的設計因素思考

魯棒性和穩定性的區別

雪崩下SiC MOSFET應用技術的魯棒性評估

多叉指MOSFET器件靜電防護魯棒性提升技巧

多叉指MOSFET器件靜電防護魯棒性提升技巧

評論