歡迎再次來到我們的技術專欄——模擬芯視界。在上一期中,我們討論了使用理想二極管控制器進行 ORing 和電源多路復用的概念和優勢、不同類型和架構,以及在汽車系統中使用理想二極管控制器實現 ORing 和電源多路復用的挑戰和解決方案。

本次為大家帶來的是《適用于隔離式 ADC 信號鏈解決方案的低 EMI 設計》。該文章將解釋 EMI(特別是輻射發射)的來源,并介紹了一些盡可能減少模擬信號鏈的 EMI 的技術,包括詳細的布局示例和測量結果。

引言

如今人們使用的電子設備數量龐大,而這些設備的體積卻在不斷縮小,這使得電磁干擾 (EMI) 成為電路設計人員面臨的一大難題。用于通信、計算和自動化的電路需要近距離工作。產品還必須符合政府的電磁兼容性 (EMC) 規定。幾乎每個國家/地區都對在其境內銷售的電子產品的 EMC 做出了規定。在美國,聯邦通信委員會 (FCC) 監管所有商業(非軍事)電磁輻射源,并在美國國家標準協會 (ANSI) 的標準 C63.4 等標準中定義了輻射和傳導 EMI 測試程序。歐盟 (EU) 國家對電子設備的電磁輻射和抗擾度都有規定;電磁兼容性指令基本上規定,設備必須符合統一的 EMC 標準,并進行相應的測試和標記。

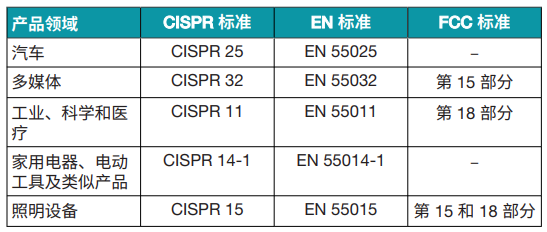

與各類設備相關的 EMC 標準有很多。例如,國際電工委員會 (IEC) 61000 標準涵蓋大多數商用產品的抗擾度要求,而國際無線電干擾特別委員會 (CISPR) 32 標準則規定傳導和輻射發射的限制。 表 1 列出了相關產品領域的 CISPR、歐洲規范和 FCC 標準。美國和歐盟以外的許多其他國家/地區要么規定要符合 FCC 或歐盟的 EMC 要求,要么有它們自己的要求。美國和歐洲以外國家/地區的法規通常與 FCC 或歐盟的要求類似。

表1: 輻射和傳導發射的主要產品標準摘要

在考慮特定類型的設備(例如智能電表)時,對低 EMI 的需求變得更加明顯。智能電表是未來能源分配的重要組成部分。它們向電力公司和終端用戶提供實時用電數據,幫助人們監測能源使用情況,并且無需上門抄表。大多數智能電表通過無線通信 連接,如無線 M-Bus 或 ZigBee,或者連接到蜂窩電話網絡(GSM、LTE cat NB1 - NB2、2G/3G/5G)。如圖 1 所示,智能電表包含一個射頻 (RF) 發射器電路,通常與電能計量電路板位于同一外殼內。必須盡可能減少計量電路的輻射發射,以免干擾射頻通信,射頻通信的工作頻率為 800MHz、900MHz、1,800MHz、 2,100MHz 或 2,700MHz 等。計量電路還需要具有抗電磁易感性(能夠承受無線通信產生電磁能量),以避免因射頻噪聲注入靈敏的能量計量前端而產生的計費誤差。

本文解釋了 EMI(特別是輻射發射)的來源,并介紹了一些盡可能減少模擬信號鏈的 EMI 的技術,包括詳細的布局示例和測量結果。

圖1:支持射頻的智能電表

EMI 和輻射發射來源

EMC 是指在存在 EMI 的情況下,電氣系統在其預定環境中正常運行的能力,以及不成為超出相關標準規定限制的電磁環境干擾源的能力。

EMI 可以是輻射干擾,也可以是傳導干擾。輻射干擾以無線電波的形式傳播,也稱為射頻干擾。傳導干擾來自傳輸信號和電力的電纜中電流產生的磁場。

本文重點關注如何盡可能減少輻射干擾。在印刷電路板 (PCB) 上或安裝在 PCB 上的集成電路 (IC) 內部,輻射發射的一些主要來源包括:

開關信號,如時鐘信號,在數字信號轉換過程中電壓電平會快速發生變化。這是因為信號中含有高頻成分。開關和時鐘信號對于 IC 內部和 IC 之間各種元件的同步運行至關重要。

開關穩壓器和其他元件,它們會導致電源線上的電流消耗快速變化。

輸入/輸出緩沖器,尤其是與 USB、HDMI 或以太網等高速接口相關的緩沖器,因為它們需要處理高速信號轉換。

在頻率高于基波信號時,IC 內部電路中的非線性行為產生的諧波。

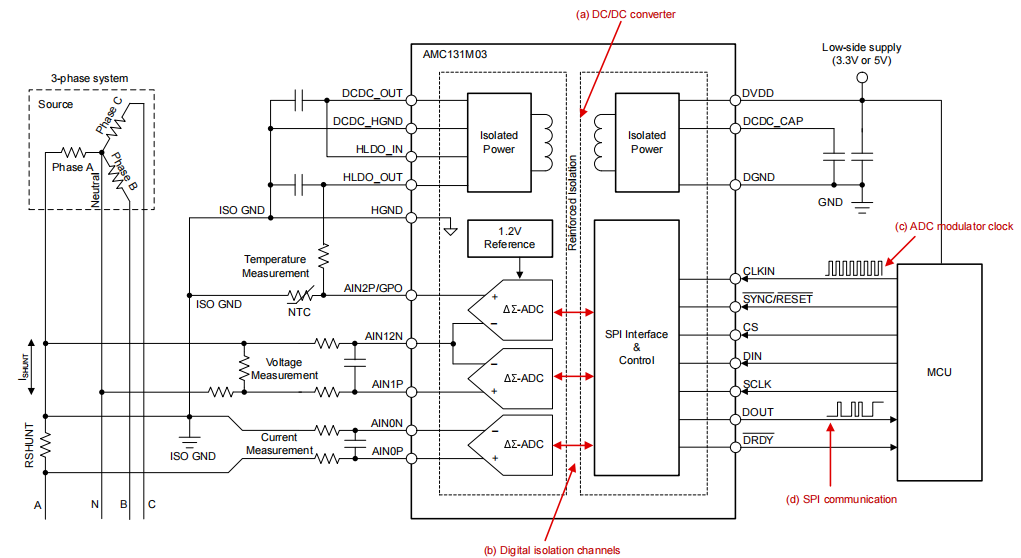

圖 2 展示了德州儀器的 AMC131M03 電隔離模數轉換器 (ADC) 及其內部架構和印刷電路板上的連接所產生的主要輻射源。ADC 用于三相電能計量應用,圖 2 顯示了單相(相 A)的電路。信號鏈的設計目的是提取電壓和電流測量值,用于能源監測。ADC 通道 0 通過分流電阻器測量相電流,通道 1 通過電阻分壓器測量相電壓 。對輻射影響最大的是內部開關直流/直流轉換器(圖 1 中的 a),它在高壓側產生隔離電源。第二大輻射發射源是數字隔離(圖 2 中的 b),因為它是通過堆疊電容屏障使用高頻開/關鍵控傳輸實現的。此外,時鐘信號也會在很寬的頻率范圍內產生輻射,例如 ADC 調制器時鐘 CLKIN(圖 2 中的 c),以及 ADC 和微控制器之間的數字通信接口(圖 2 中的 d)。

圖 2: 帶有隔離式 ADC 的模擬信號鏈和輻射發射源

更大限度減少 EMI 的技術

有幾種常見的 PCB 設計技術可以更大限度地減少 EMI :

正確接地:這是減少輻射發射的有效方法之一。小心地接地可避免可能充當天線的接地環路。使用接地平面還有助于減少環路面積,并為信號提供返回路徑,從而降低產生 EMI 的可能性。但在其他情況下,接地平面會在敏感節點上形成天線,并增加輻射發射(參閱圖 5 中的具體示例)。

元件放置:放置元件時應盡可能減少信號線的長度,尤其是高速信號。將數字和模擬元件分開,以避免干擾。

直而短的布線:以直線方式進行高速布線并盡可能縮短布線,可以更大限度地減少潛在 EMI。此外,還要注意避免在布線中形成直角,因為直角會導致反射和信號損失。

使用去耦電容器:去耦電容器可為高頻噪聲提供一條短的接地返回路徑。將去耦電容器放置在盡可能靠近 IC 電源引腳的位置。

受控阻抗:控制信號布線的阻抗將與信號源和負載的阻抗相匹配,有助于防止可能導致輻射發射的信號反射。

屏蔽:有時,在 PCB 的某些區域使用金屬屏蔽層或屏蔽材料可以防止輻射發射。

使用濾波器:濾波器可以阻擋引起輻射發射的某些頻率,在電源電路中特別有用。

層堆疊:在多層 PCB 中,應注意各層的排列方式,以盡可能減少 EMI。通常來說,交替使用電源層和接地層是一種很好的做法,因為這有助于減少環路面積,并為信號提供返回路徑。頂層和底層接地層可作為內部信號層(如產生輻射發射的時鐘)的屏蔽場。

避免時鐘諧波:時鐘信號會產生諧波,從而干擾電路的其他部分。展頻技術有助于分散這些諧波,減少其影響。

EMI 仿真:輻射發射仿真工具有助于在 PCB 設計階段預測和更大限度地減少 EMI。

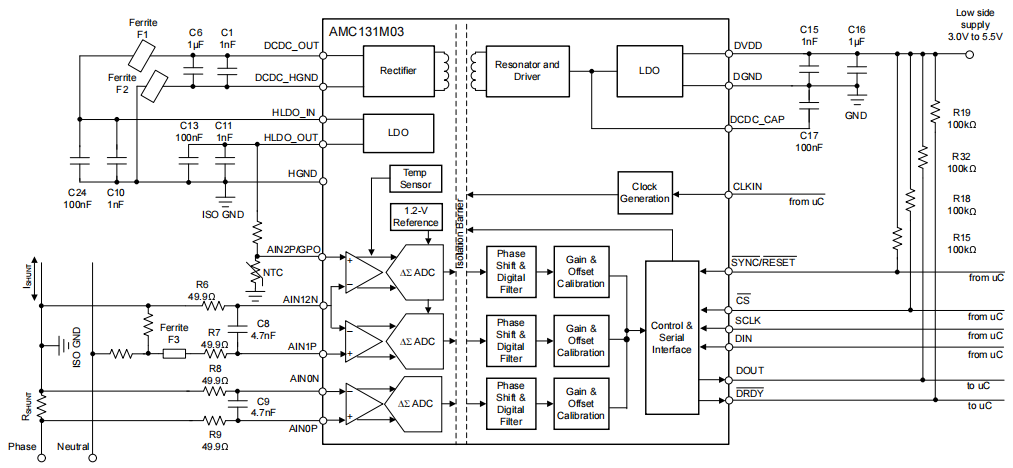

圖 3 是圖 2 中介紹的模擬信號鏈的詳細示意圖。

圖 3: 圖 2 中模擬信號鏈的詳細示意圖

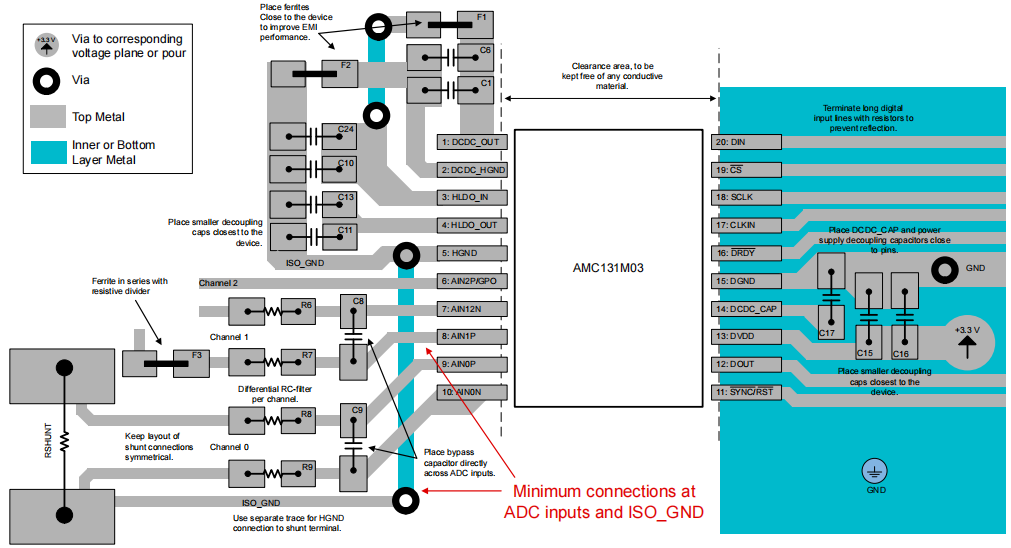

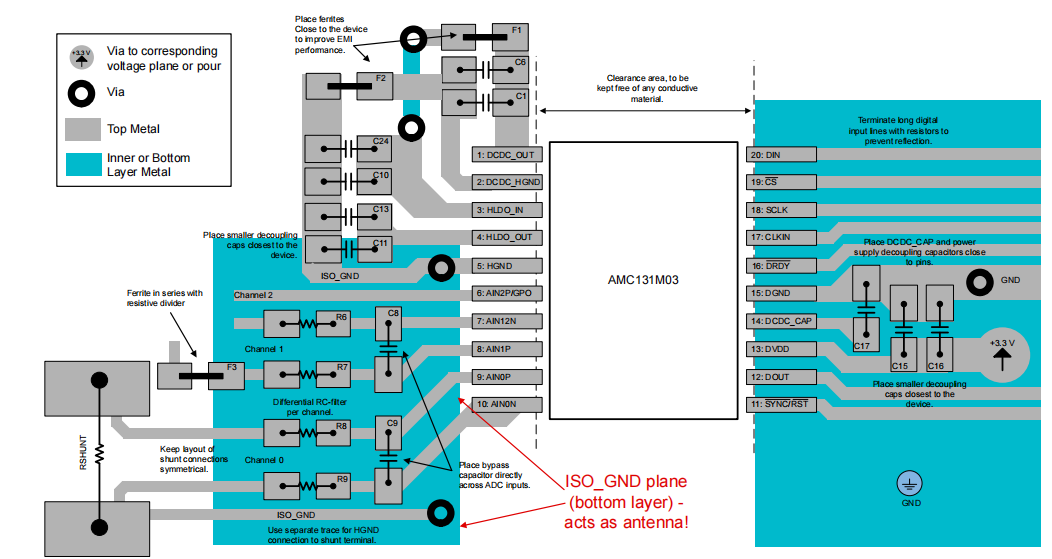

圖 4 和圖 5 展示了減少輻射發射的技術在 AMC131M03 的相應 PCB 布局中的應用。圖 4 顯示了一種“良好”布局,高壓域(AMC131M03 位置左側的 PCB 區域)的 ADC 輸入和電源線路的布線較短,將旁路電容器 C1、C6、C8、C9、C11、C13、C14 和 C24 放置在靠近 IC 的位置。

減輕 EMI 的一個重要方面是隔離式接地節點 ISO_GND 的接地方案。盡可能縮短布線長度,并且不在高壓域放置接地平面,可更大限度地減少該節點上的天線,從而更大限度地減少輻射發射。鐵氧體磁珠 F1 和 F2 插入電源連接 DCDC_OUT 和 DCDC_HGND,以阻隔高頻噪聲。您還可以在具有過高輻射發射的頻率處(取決于 PCB 設計)額外放置一個高阻抗鐵氧體磁珠 (F3),與電阻分壓器串聯,用于測量電壓。

圖 4:良好的PCB布局(低 EMI )

圖 5 展示了一種“不良”布局,其中顯示接地平面連接到 ISO_GND 節點,這起到天線的作用,會顯著增加輻射發射。

圖 5:不良 PCB 布局(高 EMI )

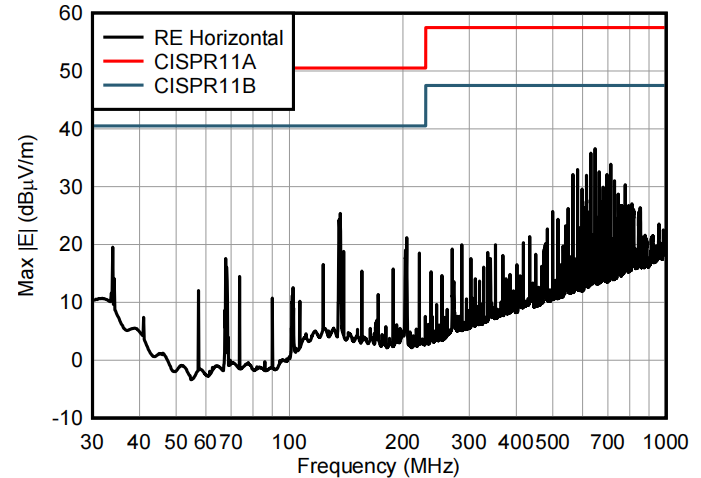

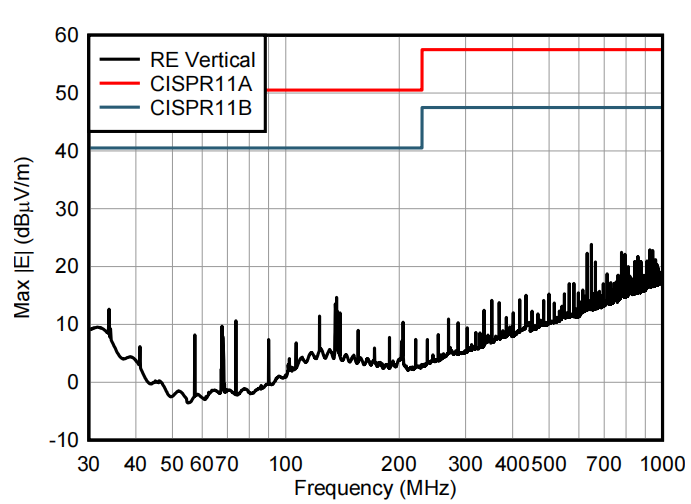

圖 6 和圖 7 顯示了使用圖 4 中所示布局實現方案的AMC131M03 PCB 的輻射發射測量。測量是按照 CISPR 11 的要求進行的,即在半電波暗室中使用為水平和垂直極化配置的寬帶天線,距離為 3m。ADC 通過 CLKIN 引腳接收連續時鐘,并生成轉換結果。不過,在對發射曲線進行表征期間沒有串行外設接口通信。該設計符合 CISPR 11 A 級和 B 級標準,裕度為 13dB,為市場上具有數據和電源增強型隔離功能的 ADC 提供超低輻射發射性能。

圖 6:水平輻射發射 CISPR

圖 7:垂直輻射發射 CISPR 11 測量

結語

為確保電子電路按設計運行,必須防止電磁干擾。同時,電路本身不得產生可能威脅或降低其他設備性能的輻射。要符合 EMC 標準,必須在四個層面上提供 EMI 保護:元件層面、電路板層面、系統層面和整個系統層面 。

本文介紹的技術可更大限度地減少 PCB 設計層面的 EMI,并可輕松應用于一個實際例子,即用于電能計量的具有增強隔離功能的一流精密 ADC 信號鏈 。憑借使用建議的 EMI 降低技術進行精心設計,該設計可實現相關 EMC 標準要求的足夠裕量 。

-

二極管

+關注

關注

147文章

9570瀏覽量

165883 -

德州儀器

+關注

關注

123文章

1686瀏覽量

140582 -

emi

+關注

關注

53文章

3582瀏覽量

127342 -

adc

+關注

關注

98文章

6430瀏覽量

544074 -

emc

+關注

關注

169文章

3872瀏覽量

182862

原文標題:模擬芯視界 | 適用于隔離式 ADC 信號鏈解決方案的低 EMI 設計

文章出處:【微信號:tisemi,微信公眾號:德州儀器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Maxim 提供優異的信號鏈解決方案(ADC、DAC、復用器···)

用于PLC的隔離式電源DC/DC成套解決方案包括層圖和原理圖

適用于工業運動控制的電流與電壓檢測

適用于工業運動控制的測量技術

適用于惡劣環境下工業應用的魯棒隔離式RS-232數據接口設計

具有低電源紋波的非隔離雙極性電源系統的電源解決方案

適用于差動信號鏈的TIDA-01427參考設計

適用于汽車電池組監測應用的的隔離式分流/電壓測量參考設計

適用于PLC應用的4輸出隔離式Fly-Buck電源參考設計

適用于筆記本計算應用中Alder Lake處理器的非隔離式直流/直流解決方案

適用于筆記本計算應用中Alder Lake的非隔離式直流/直流解決方案

適用于隔離式ADC信號鏈解決方案的低EMI設計

適用于隔離式ADC信號鏈解決方案的低EMI設計

評論