來源:中國科大微電子學院

近日,中國科大微電子學院石媛媛教授課題組設計并實現了一種直接在硅片上制造大規模單層(Monolayer, ML)單晶 MoS?高性能晶體管陣列的集成方法,相關研究成功入選2024 Symposium on VLSI Technology and Circuits(以下簡稱VLSI Symposium)。

VLSI Symposium是集成電路領域最具盛名的三大國際頂級會議(IEDM, ISSCC和VLSI)之一,今年VLSI Symposium于6月16日至20日在美國夏威夷舉行,會議匯集了世界各地行業和學術界的工程師和科學家,討論超大規模集成電路制造和設計中的挑戰和難題。

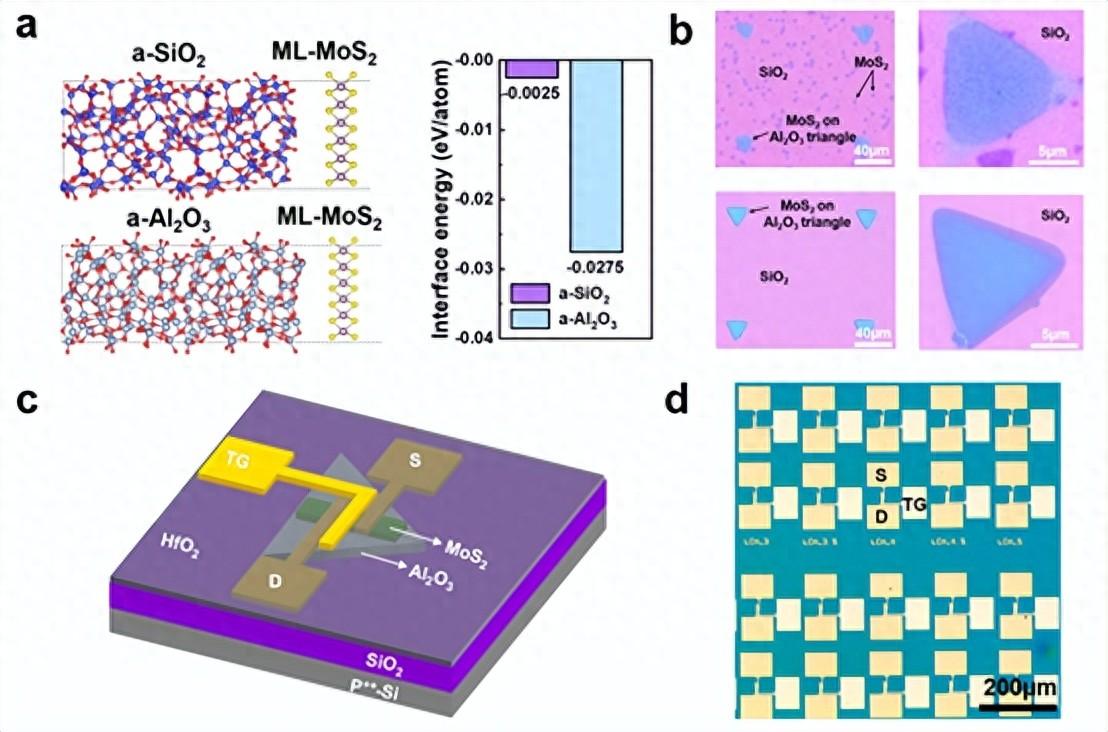

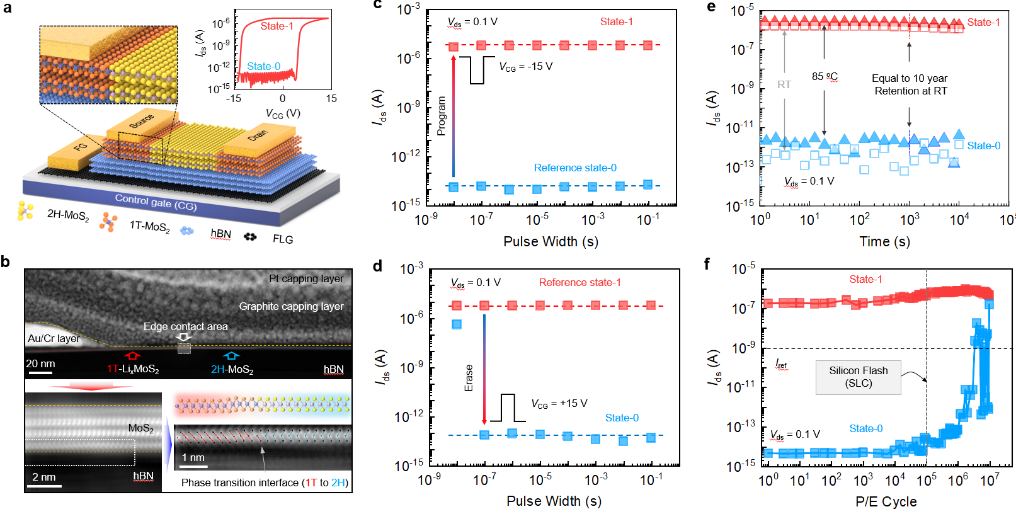

隨著先進工藝節點的持續推進,二維半導體晶體管的研發有助于延續摩爾定律,持續推進晶體管特征尺寸的微縮,不斷提升芯片算力。在基于二維半導體溝道的晶體管中,溝道的質量至關重要,常規直接生長方法沉積的多晶溝道存在大量晶界,導致器件較低的載流子遷移率。而通過單晶襯底外延生長的二維半導體成本較大,制備器件所必需的轉移過程也會帶來污染與缺陷等。此研究受單晶襯底外延生長的啟發,在硅片上設計了非晶Al?O?三角形類臺階圖案,同時利用二維半導體在非晶Al?O?和SiO?上吸附能的差異性(圖1a),促進單晶ML-MoS?陣列的選擇性區域生長(Selective area growth, SAG)(圖1b)。同時在SAG單晶ML-MoS2上直接(無需轉移過程)進行了大規模雙柵晶體管的制備(圖1c-d)。

圖1. SAG MoS? 晶體管概念與集成。(a) DFT計算二維半導體MoS?在不同非晶襯底上的吸附能;(b) 圖案化工藝輔助的SAG單晶ML-MoS?;基于SAG ML-MoS? 溝道的雙柵晶體管 (c) 三維示意圖和 (d) 陣列顯微鏡圖

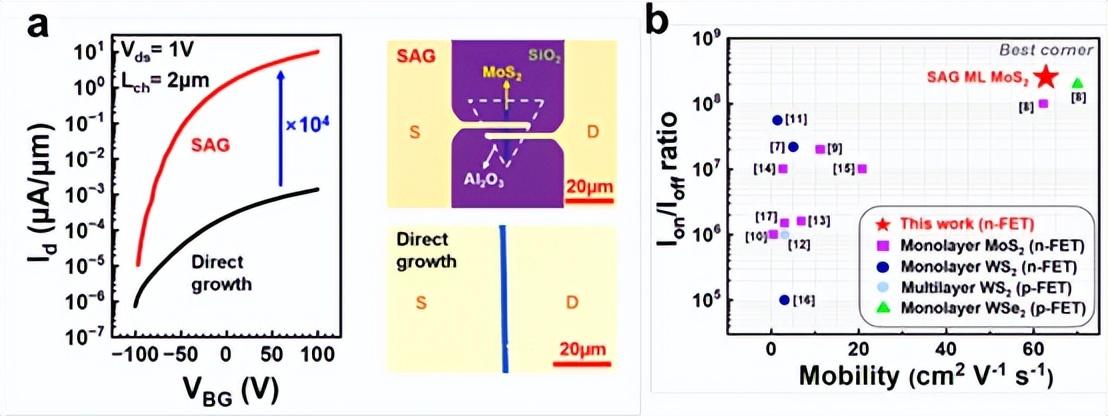

圖2. SAG MoS? 晶體管性能。(a) 基于SAG ML-MoS?溝道的背柵晶體管與直接生長制備的MoS?背柵晶體管轉移特性曲線對比;(b) 本工作中SAG ML-MoS?晶體管性能與相關文獻對比的基準圖

基于SAG ML-MoS?溝道的背柵晶體管開態電流較直接生長的MoS?溝道晶體管提升10?倍,亞閾值擺幅減小2倍(圖2)。晶體管陣列中器件最大載流子遷移率可達62.8 cm2/Vs,電流開關比>10?。此晶體管性能隨著點缺陷、柵介質等的調控可以進一步提升。該研究成果以“Single-crystalline monolayer MoS? arrays based high-performance transistors via selective-area CVD growth directly on silicon wafers”為題在大會作報告。

中國科大微電子學院碩士研究生朱貴旭為該論文第一作者,石媛媛教授為通訊作者,該項研究得到了國家自然科學基金的資助,同時也得到了中國科大何力新教授、曾華凌教授和安徽大學宋東升教授課題組的合作與支持。

審核編輯 黃宇

-

半導體

+關注

關注

334文章

26031瀏覽量

208596 -

晶體管

+關注

關注

77文章

9405瀏覽量

136654

發布評論請先 登錄

相關推薦

二維材料 ALD 的晶圓級集成變化

南方科技大學深港微電子學院三篇研究文章入選VLSI Symposium

復旦大學在壓電能量采集接口電路方向取得重要科研進展

VLSI Symposium 中國科大微電子學院在高性能二維半導體晶體管領域取得重要進展

VLSI Symposium 中國科大微電子學院在高性能二維半導體晶體管領域取得重要進展

評論