在集成電路應用設計中,項目原理圖設計完成之后,就需要進行PCB布板的設計。PCB設計是一個至關重要的環節。設計結果的優劣直接影響整個設計功能。因此,合理高效的PCB Layout是芯片電路設計調試成功中至關重要的一步。本次我們就來簡單講一講PCB Layout的設計要點。

PCB Layout設計要點

元器件封裝選擇

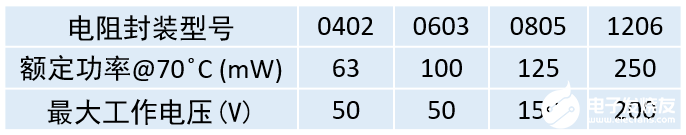

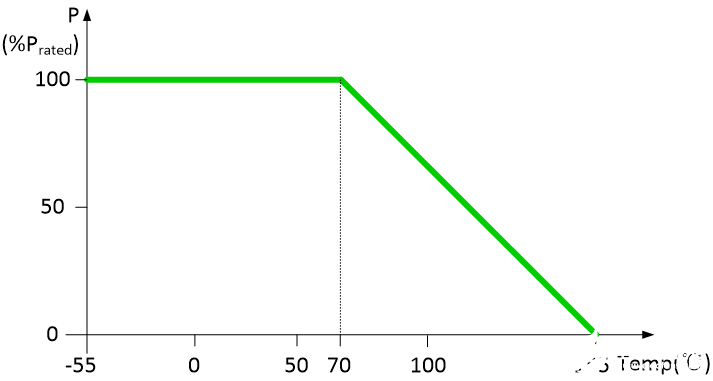

電阻選擇: 所選電阻耐壓、最大功耗及溫度不能超出使用范圍。

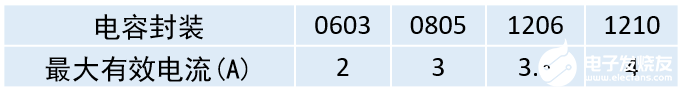

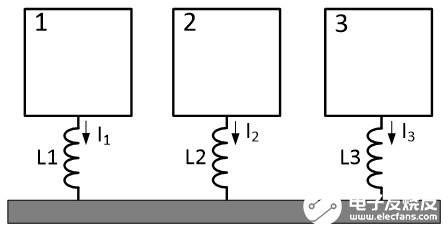

電感選擇:所選電感有效值電流、峰值電流必須大于實際電路中流過的電流。

電路設計常見干擾

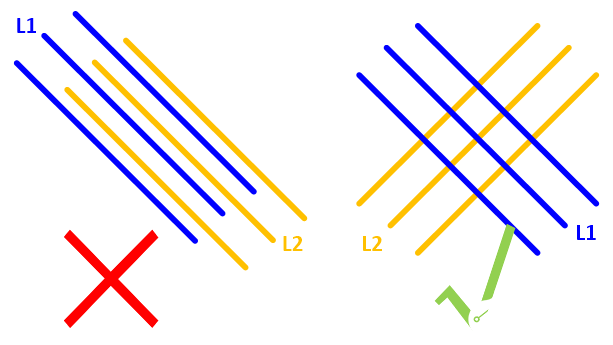

串擾: 設計線路平行走線距離過長時, 導線間的互容、互感將能量耦合至相鄰的傳輸線。可以通過以下方法減少串擾影響:

1.加入安全走線

2.實際時盡量讓相鄰走線互相垂直

3.每走一段距離的平行線,增大兩者間的間距

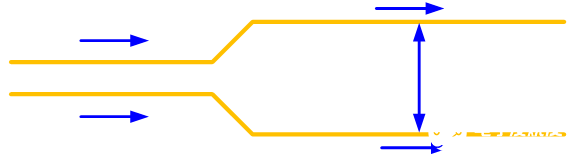

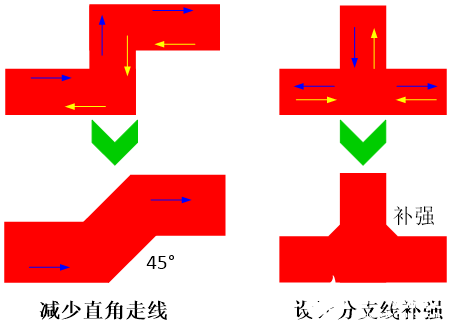

反射:由于布線的彎角、分支太多造成傳輸線上阻抗不匹配,可以通過減少線路上的彎角及分支線或者避免直角走線及分支線補強來進行改善。

確定接地方式

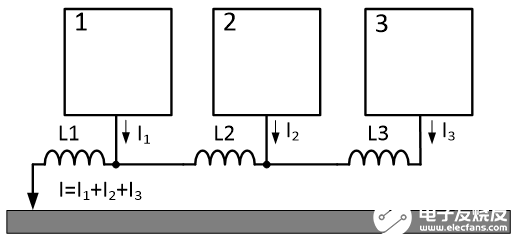

單點接地(適用于低頻電路):所有的電路接地線接到公共地線同一點, 接線簡單且減少地線回路相互干擾。

多點接地(適用于多層板電路/高頻電路):系統內部各部分就近接地,提供較低的接地阻抗。

增加濾波、旁路電容

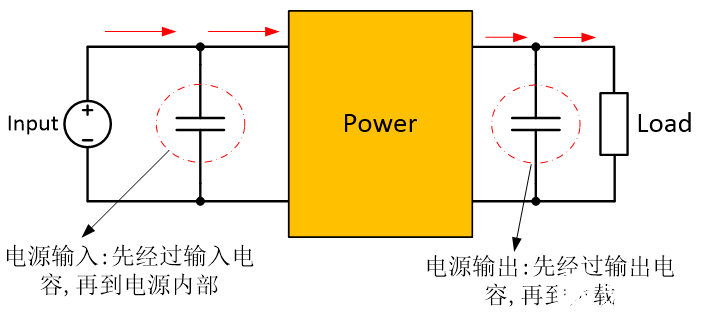

為保證輸入/輸出電壓穩定,增加輸入/輸出電容。

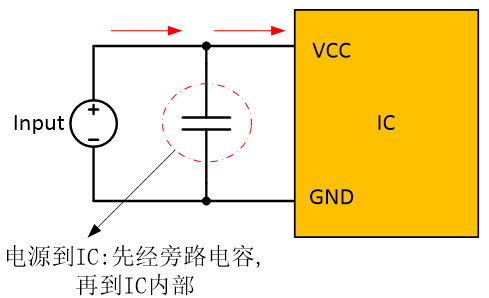

在電源和IC間增加旁路電容,以保證輸入電壓穩定并濾除高頻噪聲。

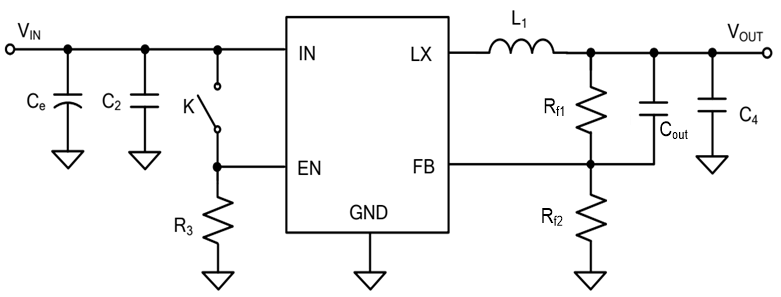

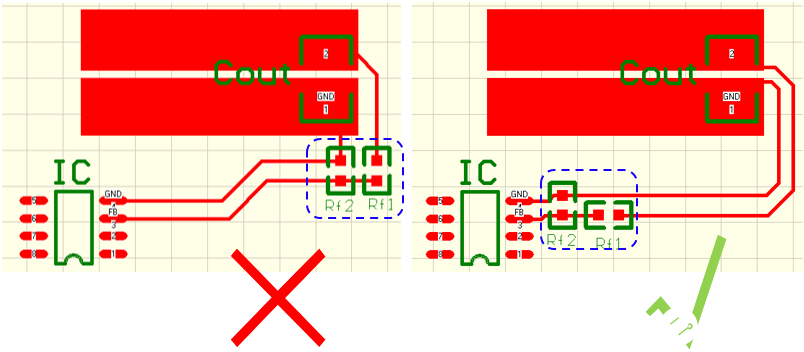

阻抗位置設計

相對來說阻抗越高的位置, 越容易被干擾。如下為一同步降壓芯片的PCB阻抗位置設計。

PCB Layout設計技巧

電源/地線處理

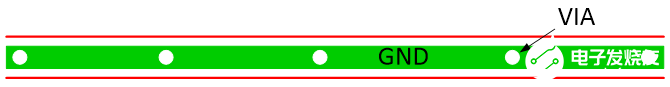

既使在整個PCB板中的布線完成得都很好,但由于電源、 地線的考慮不周到而引起的干擾,會使產品的性能下降. 布線時盡量加寬電源、地線寬度,最好是地線比電源線寬,它們的關系是:地線>電源線>信號線。

對數字電路的PCB可用寬的地導線組成一個回路, 即構成一個地網來使用(模擬電路不能使用該方法)。用大面積敷銅層作地線用,在印制板上把沒被用上的地方都與地相連接作為地線用。或是做成多層板,電源、地線各占用一層。

數字與模擬電路的共地處理

數字電路與模擬電路的共地處理: 數字電路與模擬電路共同存在時,布線需要考慮之間互相干擾問題,特別是地線上的噪音干擾。

數字電路的頻率高,模擬電路的敏感度強,對信號線來說,高頻的信號線盡可能遠離敏感的模擬電路器件,

對地線來說,整個PCB對外連接界只有一個端口,所以必須在PCB內部進行處理數、模共地的問題,而在板內部數字地和模擬地實際上是分開的它們之間互不相連,只是在PCB與外界連接的端口處(如插頭等), 數字地與模擬地有一點短接,請注意,只有一個連接點。

信號線分布層

信號線布在電源(地)層上: 在多層印制板布線時,由于在信號線層沒有布完的線剩下已經不多,再多加層數就會造成浪費也會給生產增加一定的工作量,成本也相應增加了,

為解決這個矛盾,可以考慮在電(地)層上進行布線。首先應考慮用電源層,其次才是地層。因為最好是保留地層的完整性。

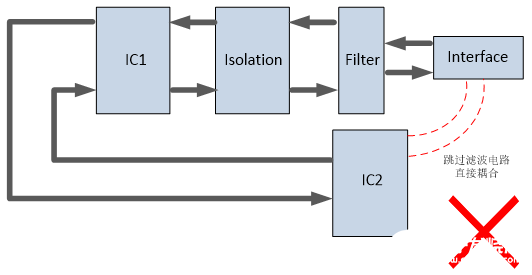

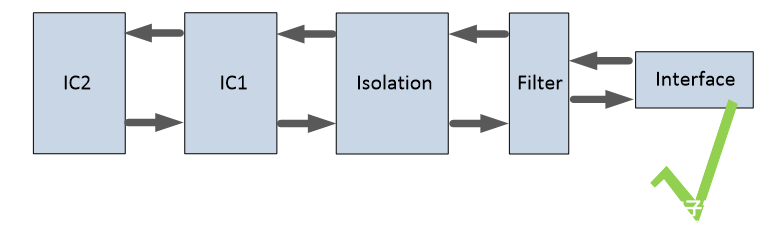

信號流向設計

PCB布局設計時,應充分遵守沿信號流向直線放置的設計原則,盡量避免來回環繞。

PCB Layout設計實例

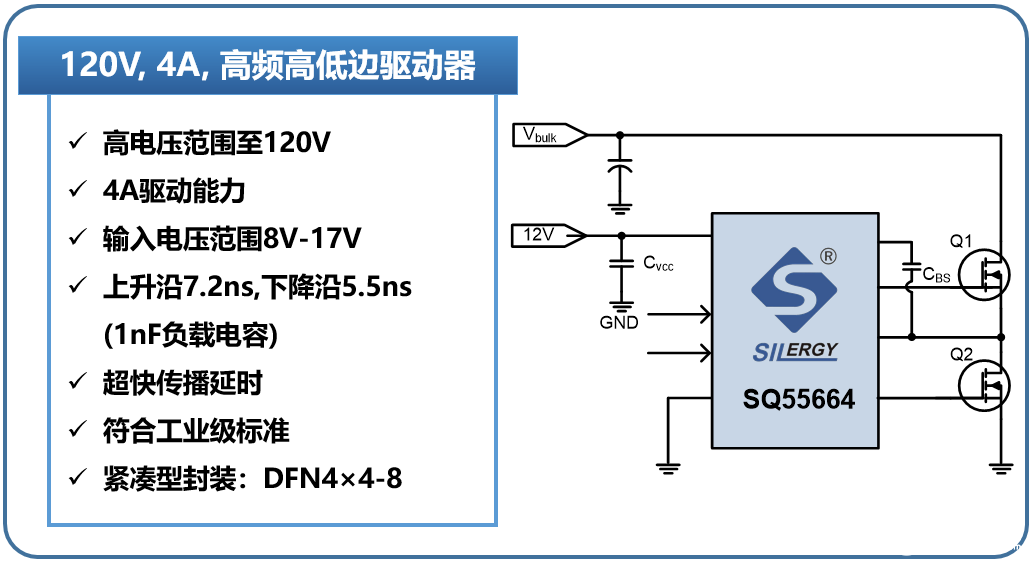

Layout設計建議

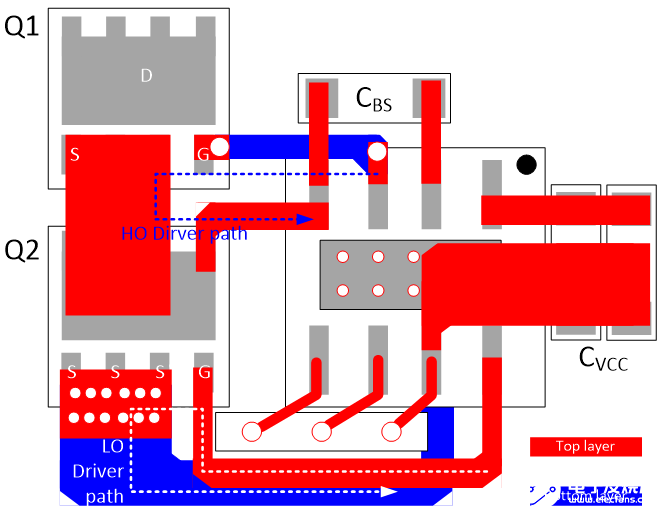

2. VCC-GND(CVCC) / VB-VS(CBS)電容盡可能靠近芯片;

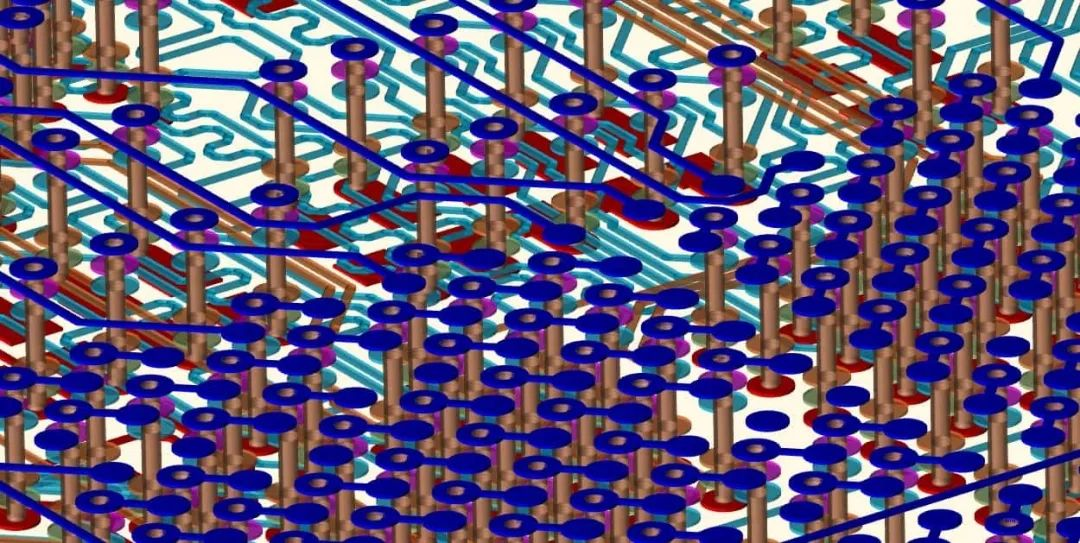

3.芯片散熱焊盤加一定數量過孔并且與GND相連接(增加散熱、減小寄生電感);

4.GND布線直接與MOSFET 源極(source)相連接, 且避免與源極(source)-漏極(drain)間大電流路徑相重合, VS 同理GND布線原則(避免功率回路與驅動回路重合);

5.HO/LO布線盡量寬(60mil-100mil,驅動電流比較高,降低寄生電感的影響);

6. LIN/HIN 邏輯輸入端口盡量遠離HS布線(避免過高的電壓擺動干擾到輸入信號)。

*SQ55664 Layout設計

免責聲明:本文轉自網絡,版權歸原作者所有,如涉及作品版權問題,請及時與我們聯系,謝謝!

審核編輯 黃宇

-

pcb

+關注

關注

4317文章

23004瀏覽量

396247 -

Layout

+關注

關注

14文章

402瀏覽量

61653

發布評論請先 登錄

相關推薦

專業PCB設計,高速PCB設計,PCB設計外包, PCB Layout,PCB Design,PCB畫板公司,PCB設計公司,迅安通科技公司介紹

PMP30784.1-2MHz 汽車類 SEPIC PCB layout 設計

PMP30916.1--8V 反相降壓/升壓 PCB layout 設計

PMP30930.1-EMI 優化型降壓 PCB layout 設計

TIDEP-01022-汽車網關 PCB layout 設計

TIDA-060029-LCR 表模擬前端 PCB layout 設計

PMP20587.1-反相降壓/升壓 PCB layout 設計

TIDA-010052-用于電機驅動的安全電源 PCB layout 設計

PMP30805.1-小型汽車 SEPIC PCB layout 設計

PMP30691.1-具有多路輸出軌 PCB layout 設計

PMP21783.1-60W、超寬范圍電源 PCB layout 設計

PMP31194.1-使用集成 FET 的汽車 SEPIC PCB layout 設計

PCB Layout 的 9 個套路

PCB Layout 的 9 個套路

評論