摘要:文章簡單介紹了微波集成電路的發展動態,綜述了以美國DARPA為代表的國內外機構在射頻微系統方面的重大研究計劃及其水平,和射頻微系統在通信、雷達、相控陣等領域的代表性應用,并總結了射頻微系統互連、仿真與優化和集成架構設計等三個關鍵技術及其進展情況,最后對射頻微系統今后的發展趨勢做出了展望。

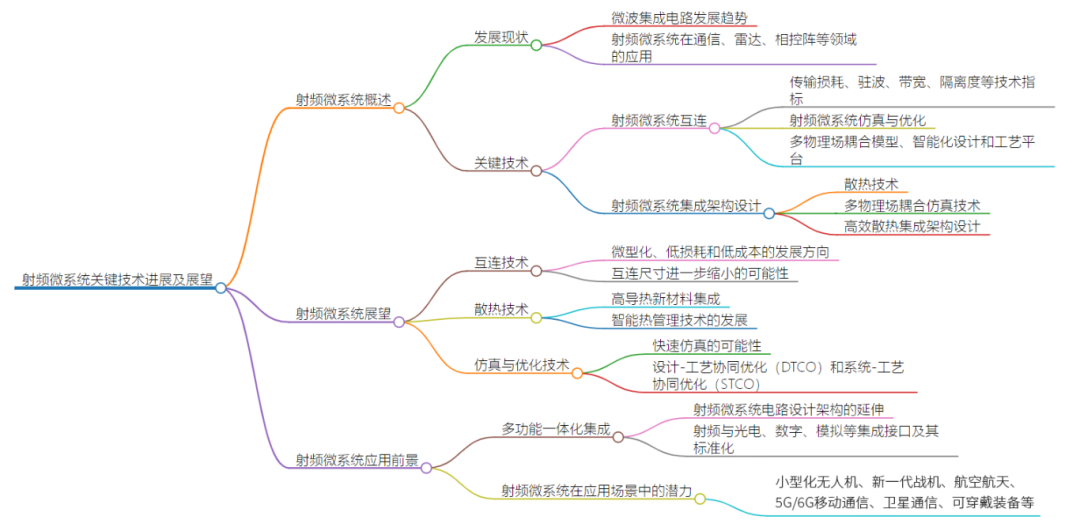

Chrent引言小型化是微波毫米波集成電路與系統發展的必然趨勢,而集成技術是必由之路。20世紀40年代雷達的出現推動了微波電路的迅猛發展,出現了以波導分離立體電路為代表的第一代微波集成電路(如圖1所示)。隨著60年代低損耗平面傳輸技術的發展,實現了單層介質基板集成電路,形成了以平面微波混合集成電路(HMIC)為代表的第二代微波集成電路,提高了性能和可靠性的同時減小了體積和重量。到70年代,依托砷化鎵等半導體芯片技術的突破發展,微波單片集成電路技術(MMIC)以其低成本、高性能、小型化等優勢,成為了第三代微波集成電路高速發展的關鍵技術。同時,低損耗多層復合介質電路板和厚膜工藝技術的發展,使得無源電路實現多層布局結構,與MMIC芯片集成后的多芯片組件(MCM)進一步實現了微波電路的小型化。

20世紀90年代末,美國國防部高級研究計劃局(DARPA)率先提出采用異構集成技術將微電子器件、光電子器件和微機械系統(MEMS)器件集成,形成微型化異構集成電路。此后,隨著異質半導體外延技術和硅通孔(TSV)為代表的垂直互連技術的突破,以片上系統(SoC)和系統級封裝(SiP)為代表的第四代微波集成電路得到了快速發展。該技術可將無源電路和有源電路在中間層上進行布線和打孔的2.5維(2.5D)或者在芯片上打孔和重布線(RDL)的3維(3D)集成方式進行,不僅實現了微波電路從小型化到微型化的跨越,且在功能集成度上有著明顯的提升,因此第四代微波集成電路也被稱為射頻微系統。

SoC技術具有最優的尺寸、重量和功耗(SWaP),然而在輸出功率、噪聲系數和成本等方面仍存在諸多瓶頸。SiP技術則采用封裝把不同功能的芯片進行高維度集成,融合了HMIC和MMIC的優點,設計更為靈活。射頻微系統的典型概念是采用異質異構集成工藝,將射頻前端功能模塊(例如變頻、接收、發射、天線等)進行2.5D/3D集成的微波電路,其小型化、低成本、多功能等優點在電子戰、新一代移動通信、物聯網、汽車雷達、可穿戴等民用領域有著廣泛的應用前景。

圖1微波集成電路發展歷程

Chrent國內外射頻微系統研究現狀異質異構集成中的“異構”集成側重“多片”,將不同工藝單獨制造的部件(芯片、組件等)通過TSV、RDL和微凸點銅柱等工藝進行系統集成;而“異質”集成側重“單片”,強調的是通過異質外延生長方式,將不同半導體材料,如硅(Si)、砷化鎵(GaAs)、磷化銦(InP)、氮化鎵(GaN)等在一個襯底上形成單片集成電路。

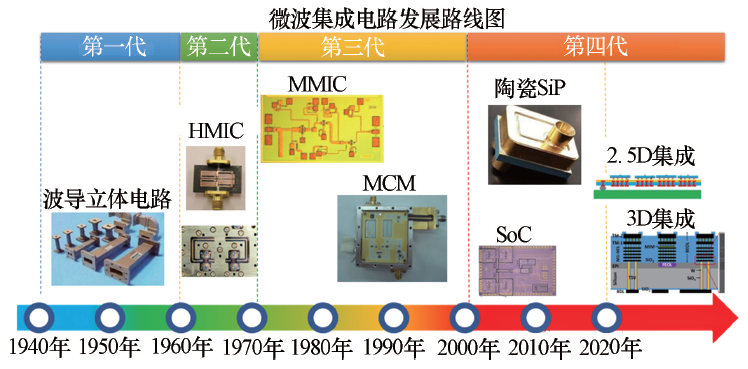

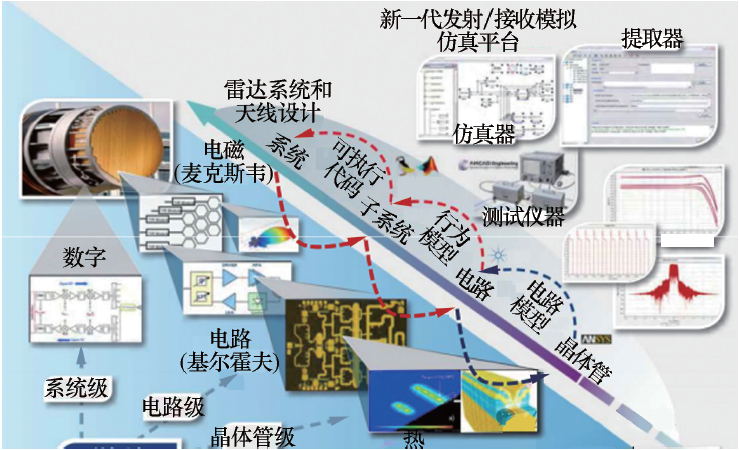

美國DARPA成立了微系統技術辦公室(MTO)重點發展集成微系統技術,在射頻微系統領域布局了一系列的研究計劃(如圖2所示)。2006年DARPA啟動了“用于可重構收發機的可擴展毫米波架構(SMART)”項目,其目標是通過毫米波收發機架構設計實現微型化和高功率,到2010年實現5W/cm2的功率密度。同年啟動的“三維微電磁射頻系統(3D-MERFS)”項目擬通過MEMS印刷電路板技術改進射頻系統的性能。

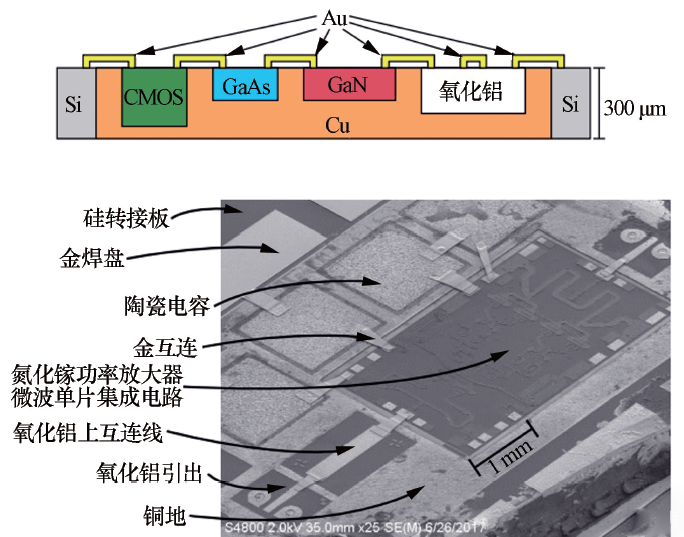

為進一步實現射頻系統的微型化,DARPA又開展了異質集成射頻微系統研究。2007年DARPA啟動“硅上化合物半導體材料(COSMOS)”項目,目標是采用互補金屬氧化物半導體(CMOS)工藝在Si上異質集成多種化合物半導體晶體管,突破了SiCMOS與InP異質結雙極晶體管(HBT)兩種器件工藝的異質集成。2013年DARPA啟動了“多樣化異質異構集成”(DAHI)項目,不僅開發了多種工藝集成技術,并實現了相應的工藝套件(PDK)和仿真平臺。Northrop Grumman公司依靠該平臺實現了InP HBT和GaN高電子遷移率晶體管(HEMT)在Si CMOS上的異質集成,首次實現三種半導體工藝的異質集成,將原本的Si基混頻器的輸出功率從8mW提高到3.4W。2017年DARPA啟動了“電子復興計劃(ERI 1.0)”,包含了三維單片集成微系統等項目,可進一步實現微型化。

圖2DARPA射頻微系統相關重點計劃

隨著系統集成復雜度的提高和工藝節點的進一步縮小,電路設計面臨著成本高、良率低、可靠性差等問題。對此,DARPA在2017年啟動了“通用異構集成及知識產權復用策略(CHIPS)”項目。該項目意在通過混合和匹配即插即用式“芯粒”(Chiplet)構建一個模塊化雷達系統,不僅可以通過減小芯片面積而降低半導體中的缺陷密度,從而提高良率和可靠性,還可以通過IP復用,降低設計成本。此后,DARPA加強了異質異構集成技術在射頻領域的應用和平臺建設方面的支持力度,2018年提出了“毫米波數字陣列(MIDAS)”項目,發展18~50 GHz頻段的多波束數字相控陣技術,采用三維異構集成,降低了體積和重量,提高了數字毫米波收發器性能。2022年DARPA宣布設立“下一代微電子制造”(NGMM)研究項目,旨在創建一個三維異構集成(3DHI)設計與工藝研究公共平臺。2023年,DARPA宣布將構建3DHI微系統設計和制造研究中心,并啟動電子復興計劃(ERI 2.0),為三維集成射頻微系統發展和應用提供更加完善的平臺。

在歐洲方面,1987年歐洲的西門子、安奕極(AEG)、飛利浦和弗勞恩霍夫開始進行3D集成技術的開發。在2006年歐洲啟動了e-CUBES(electronic-cubes)項目,實現了面向整個歐洲的3D集成系統封裝(3D-SiP)平臺。在2007-2013年又啟動了“最可靠的環境智能納米傳感系統(e-BRAINS)”項目,目的是整合3D集成與納米技術,為下一代異質集成半導體技術開發提供更高效的解決方案。

射頻微系統主要分為不集成天線的前端收發組件(FEM)射頻微系統和集成了天線的前端(FE)射頻微系統。射頻微系統的輸出功率取決于功率放大器芯片,目前典型射頻放大器芯片的半導體材料有Si、GaAs、InP、GaN等。Si基放大器成本和集成度具有優勢,但輸出功率較小且噪聲大。InP和GaAs放大器具有噪聲系數低的優勢,適合用于低噪聲放大器,其中InP放大器在220 GHz以上頻率的輸出功率有較大優勢。GaN器件因其高功率密度特性,已經是射頻固態功放中的主流技術,也是提升射頻微系統輸出功率的關鍵。

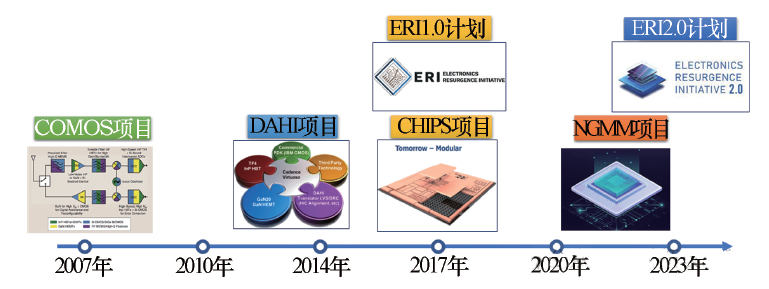

FE射頻微系統主要采用天線外集成(包括封裝上天線(AOP)片上天線(AOC))和天線內集成(AiP)兩種方式實現天線與FEM射頻微系統的集成。由于天線尺寸與工作波長成正比,再加上功放體積大、散熱困難等問題,低頻段(如L波段)的射頻微系統主要集中在FEM射頻微系統,而FE射頻微系統主要集中在毫米波和太赫茲等頻段。2012年德國英飛凌采用了內嵌晶圓級球柵陣列封裝(eWLB)首次實現了集成了77 GHz鍺硅(SiGe)4通道收發芯片和4個天線的FE射頻微系統(如圖3所示),采用RDL技術將天線集成在模組內形成AiP,使得毫米波信號無需通過PCB板進行傳輸,從而降低了互連引入的損耗,模塊體積為8×8mm2。

圖3基于eWLB工藝的77 GHz FE微系統

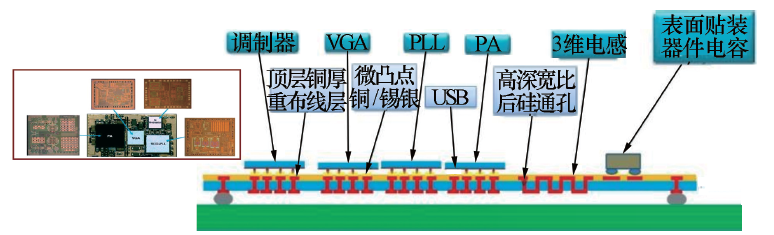

近年來,隨著射頻微系統技術的日趨成熟,已經開始從基礎研究面向了應用研究。2019年法國格勒諾布爾-阿爾卑斯大學針對下一代應急通信提出了集成3D電感的高阻Si轉接板技術,采用RDL和TSV工藝實現了集成功率放大器、可變增益放大器(VGA)、壓控振蕩器(VCO-PLL)和正交(IQ)調制器芯片的FEM微系統(如圖4所示),在實現小型化的同時滿足專業移動電臺(PMR)和3GPP等雙模通信系統要求。

圖4SiP射頻微系統模組

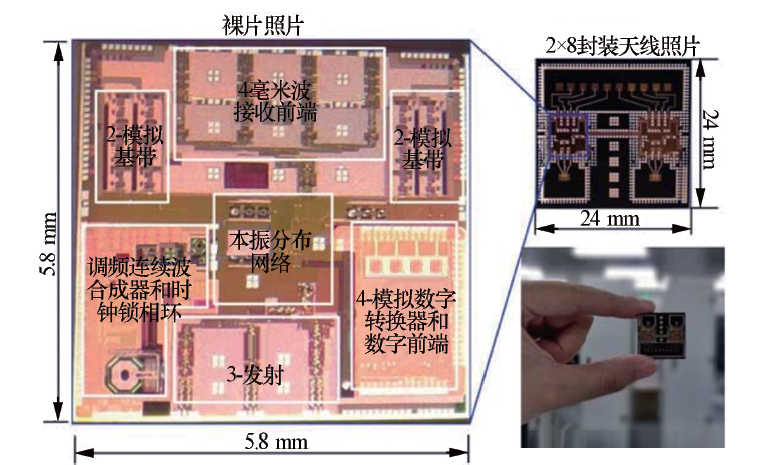

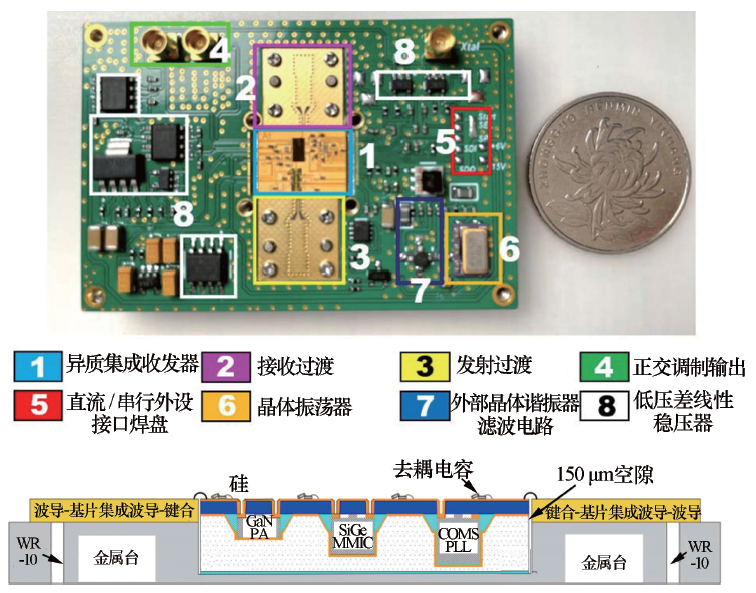

在雷達應用方面,2021年中電科38所設計了一款76~81 GHz的調頻連續波(FMCW)多輸入多輸出(MIMO)雷達(如圖5所示)。該雷達采用了埋入玻璃扇出(eGFO)工藝,集成了2個發射天線和8個接收天線,典型輸出功率為14.5 dBm,在多饋源虛擬陣下提升了7.5 dB的等效各向同性輻射功率(EIRP)。2022年上海交通大學基于苯并環丁烯(BCB)將X波段硅基鎖相環芯片、W波段SiGe毫米波芯片、GaN功率放大芯片、電容、TaN電阻和濾波器等無源元件進行集成(如圖6所示),輸出功率達到22 dBm,整體體積僅為60×40×8mm3。

圖52×8 MMIO eGFO封裝AiP

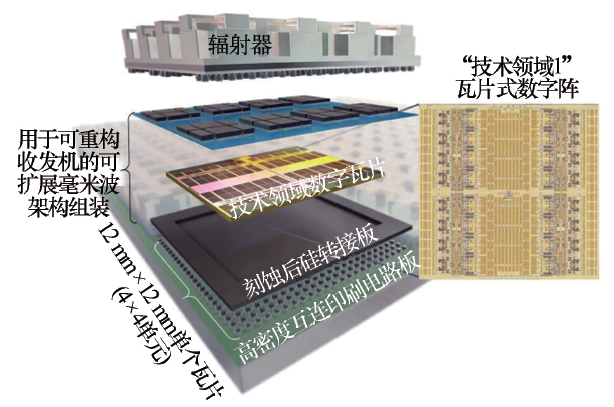

針對大陣面相控陣系統,雷神公司提出了可擴展的瓦片式FEM射頻微系統(如圖7所示)。該組件由4×4個單元組成,基于BCB的RDL和TSV轉接板將高效率InP功放、InGaAs低噪聲放大器和32通道的CMOS收發專用集成電路(ASIC)數據轉化芯片進行集成,在18~50 GHz發射功率大于3 dBm,接收支路增益可調范圍9~25 dB。

圖694 GHz FMCW射頻前端(含電源)

圖7可擴展集成架構

Chrent射頻微系統關鍵技術及其發展現狀2.1射頻微系統互連

射頻微系統的互連作為連接其中不同電路和組件的紐帶,對系統性能有著重要影響,主要技術指標包括傳輸損耗、駐波、帶寬、隔離度等。

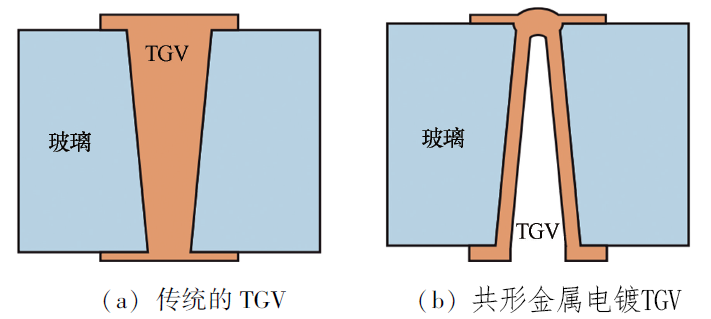

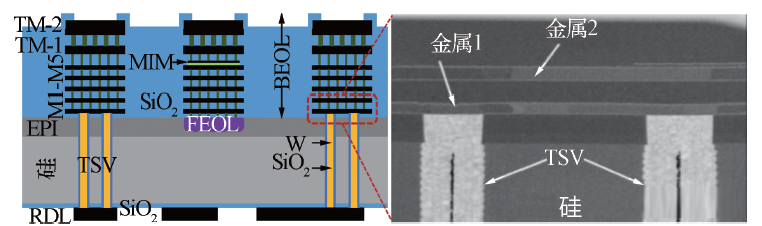

在TSV互連中,轉接板通常采用高阻Si。2008年南洋理工大學研究了基于傳統銅插入式互連與同軸式TSV互連兩種結構形式,實測表明基于高阻Si的同軸結構TSV互連(介質采用SU-8)在10 GHz下具有更低的損耗(0.33 dB/mm)和駐波特性。與TSV相比,基于更高體電阻率、更低介電常數的玻璃通孔(TGV)可以實現更低的傳輸損耗。2018年瑞典皇家理工學院提出一種共形金屬電鍍工藝(如圖8所示),實現的TGV通孔在10 GHz的插入損耗僅為0.14 dB/mm。

隨著工作頻率的進一步升高,傳輸線的導體損耗、寄生電容等寄生參數效應變大。2015年瑞典皇家理工學院采用一種可實現高深寬比的磁自組裝TSV工藝。該工藝采用比SiO2/Si3N4更低介電常數和低楊氏模量的BCB材料充當絕緣層,實現了DC~86 GHz帶寬互連,75 GHz下插損為2.12 dB/mm。2020年德國IHP萊布尼茨創新微電子研究所制備了一種BiCMOS內嵌的環形TSV結構(如圖9所示),在240 GHz和300 GHz處可以實現優于0.83 dB和0.94 dB的插損。

圖8傳統TGV與共形金屬電鍍TGV

圖9BiCMOS內嵌TSV結構

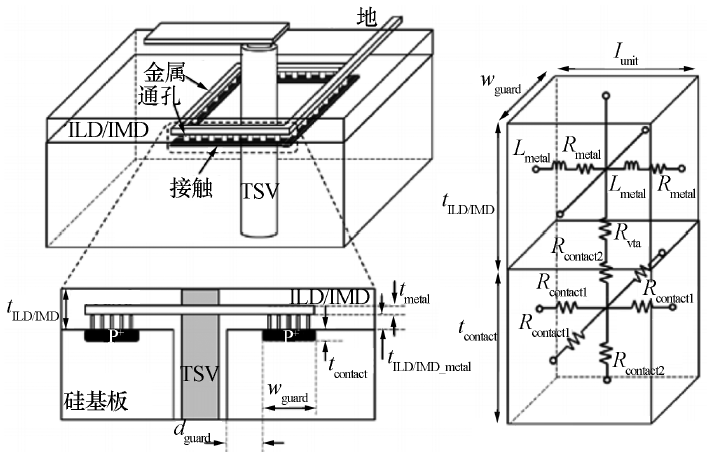

射頻微系統中互連與互連、互連與有源器件的電磁耦合效應對電路性能(特別是信號完整性)有著重要的影響,需要考慮傳輸線的隔離度。為減少串擾,一方面可從集成架構上考慮,例如采用周期性結構(EBG)進行分塊功能的隔離;另一方面,從互連線本身出發,設計高隔離的互連結構。2011年韓國科學技術院(KAIST)針對TSV互連提出了一種保護環結構(如圖10所示),可以將穿過絕緣層的泄露電流經過接地的保護環從而降低串擾噪聲。該結構在1 GHz處耦合噪聲幅值降低了53.5%,在0~20 GHz改善隔離10 dB以上。2020年西安電子科技大學提出了一種六邊形硅通孔接地屏蔽結構,通過將屏蔽通孔接地,電磁場被限制在中心導體和屏蔽通孔之間從而降低損耗,相較傳統G-S TSV分布結構,在0~20 GHz范圍內串擾優化15 dB。

2.2射頻微系統仿真與優化

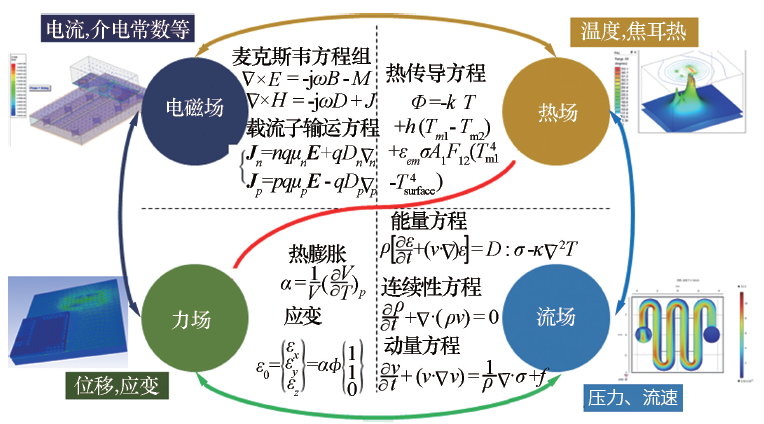

隨著射頻微系統中芯片和互連集成密度的提高,電路內部的電磁、熱、力、流等多物理場耦合效應更加突出,導致電磁兼容和可靠性問題成為應用的瓶頸。此外,系統中的尺度涵蓋10-9~10-1m,跨尺度的計算進一步加劇了射頻微系統的仿真效率,因此如何在多場-多尺度下開展射頻電路高效率仿真成為射頻微系統設計的關鍵。

圖11為射頻微系統中多物理場之間的耦合關系。電磁場與熱場間耦合效應主要由兩方面構成:一方面是材料與半導體器件在電磁場作用下產生焦耳熱;另一方面由于溫度的變化導致材料的電導率、介電常數、載流子遷移率產生變化,在影響材料和半導體器件性能的同時也產生了焦耳熱,從而形成一種互耦關系。熱場與力場的耦合效應是因為材料的熱膨脹與熱效應有關,因此溫度會改變材料的體積和位移,從而改變異構異質材料間的應力,導致形變。形變一方面會導致材料和器件電磁特性的變化,另一方面會產生材料間的應力失配而產生裂紋甚至斷裂等問題。此外,射頻微系統中為降低系統溫度,部分電路會引入流體散熱等主動散熱技術。微流道速度和流量對溫度調節效果顯著,但流速和流量的不同對流道的壓力也不同,因此在降低溫度的同時也帶了新的應力。

圖10保護環結構及其等效電路模型

圖11射頻微系統中多物理場耦合關系

目前主流的多物理場耦合仿真平臺有兩大類型一種是采用直接耦合求解方法(緊耦合,例如COMSOL),直接聯立求解所有場方程;另一種是間接耦合求解方法(松耦合,例如ANSYS),先對每一個場單獨求解,然后將求解結果代入到下一個場進行求解,完成所有場求解后迭代直至所有場的解收斂。2018年上海交通大學針對無源和有源器件進行了電-熱耦合計算和仿真,并開發了多場耦合仿真軟件。無論是緊耦合還是松耦合的求解方案,其本質均為基于有限元方法進行微分方程和偏微分方程的求解,求解依賴網格劃分的精度。射頻微系統幾何尺度跨度大,內部元器件眾多,其RDL、TSV等與芯片、封裝、PCB、腔體等結構比最大可達到1∶50000,為得到精確的仿真結果需要大量的仿真資源和計算時間。

對此,近年來模型驅動的多物理場仿真技術以其仿真計算效率高的特點獲得了關注。2013年法國THALES構建了一套協同設計平臺,可實現數字、電磁、電路、熱的多專業協同設計,以及從晶體管-組件-系統的跨層級仿真(如圖12所示)。2016年DARPA在DAHI項目下也形成了一套系統、功能單元、基礎工藝的協同設計方法,其軟件平臺已成熟應用。2021年電子科技大學對射頻微系統互連結構開展多場耦合可靠性研究,并研制了一款射頻微系統可靠性分析軟件,通過建立封裝可靠性模型,提高計算效率。2022年中電科55所通過器件級熱仿真、電路級仿真和系統級仿真相結合的方法進行了超寬帶射頻微系統熱電設計。

圖12法國THALES多場協同設計方案

2.3射頻微系統集成架構設計

射頻微系統的集成架構設計主要指堆疊結構和電路布版,除考慮系統性能、體積和成本外,還需重點考慮高效散熱和集成天線。

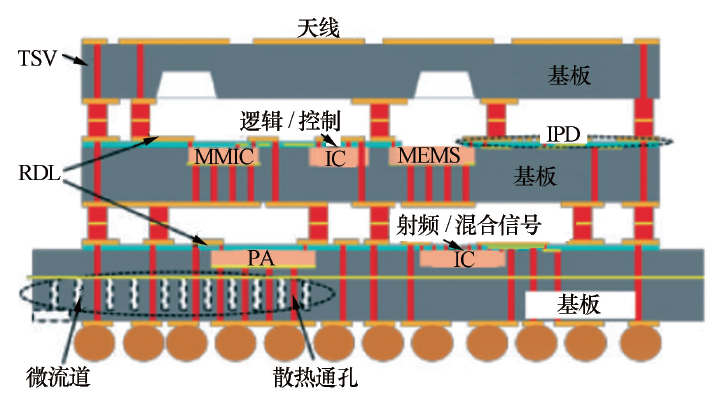

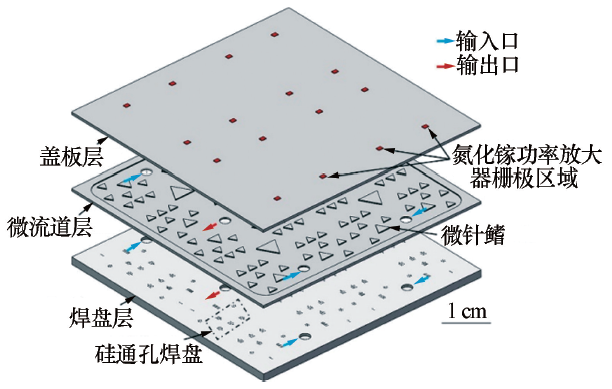

隨著集成度的提高,熱流密度也隨之增大,因此設計高效散熱的集成架構是射頻微系統需要關注的重點之一。典型的散熱技術有采用高導熱材料的被動散熱和采用微流道的主動散熱技術。2021年中電科55所基于硅基微流道散熱架構提出了一款射頻FE微系統架構(如圖13所示),內置微流道的同時還在芯片下設置金屬柱陣列提高散熱效率。2023年北京大學提出了一種內嵌微流道轉接板的優化設計方法(如圖14所示)。該結構包括三層,頂層是流道的蓋層,第二層是放置了三角形微針鰭陣列的硅基微流道層,大的微針鰭用于支撐,流道采用4進2出方式以改善溫度均勻性,最下面一層是低溫共燒陶瓷(LTCC)基板,優化后實現最大散熱能力達到1300 W/cm2,優于圓形微針鰭陣列和S形結構。

圖13硅基微流道FE射頻微系統

圖14基于內嵌微流道轉接板4×4 FEM微系統

2019年美國科羅拉多大學提出了一種金屬嵌入式芯片(MECA)高效散熱集成技術(如圖15所示)。該技術將射頻芯片和氧化鋁基板無源器件內嵌到銅金屬中,與沒有用MECA技術的裝配相比,MECA技術可使得GaN芯片在10 GHz下增益提升3 dB,效率增加3.2%。

圖15金屬嵌入式芯片結構示意圖及其集成后實物照片

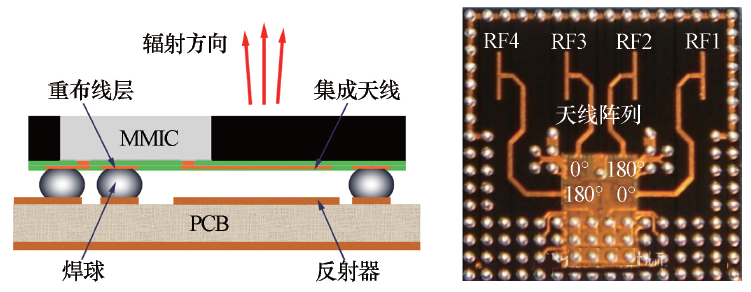

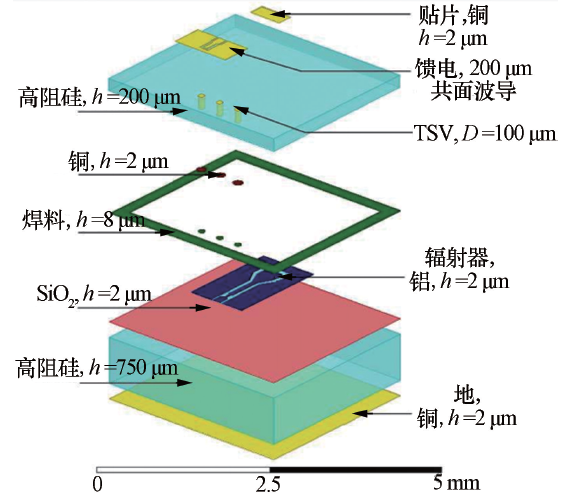

在FE射頻微系統上,其核心是如何實現AiP天線設計以及與芯片的互連。2013年新加坡微電子所設計了一種基于TSV互連的晶圓級封裝的AiP(如圖16所示),該天線采用基于TSV的兩層高阻Si堆疊,底層Si上是共面波導(CPW)饋電和槽線輻射器,頂層Si上放置了貼片用于改善增益和輻射效率,在76~93 GHz實現了2.4 dBi增益。

圖16基于TSV互連的晶圓級封裝的AiP

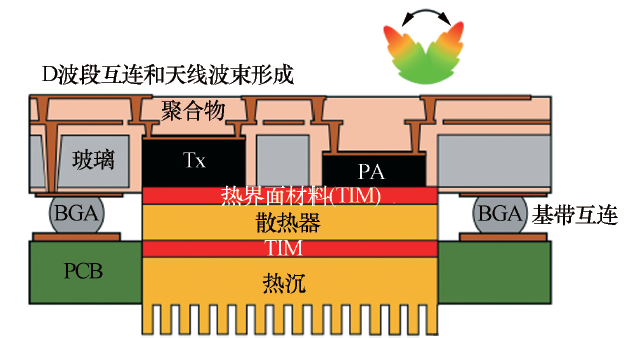

2023年,美國佐治亞理工學院提出了一種集成芯片的玻璃ABF樹脂基轉接板AiP技術,該技術采用了交錯介質通孔結構,比傳統的金絲和倒裝互連具有更低的損耗,而且利用該技術還可以集成傳統熱沉而實現高效散熱(如圖17所示)。利用該技術實現了1×8 AiP貼片天線陣列,在D波段實現了11.6 dB的高增益。

圖17玻璃樹脂基FE射頻微系統

Chrent射頻微系統展望在互連方面,目前的性能水平基本上能夠滿足射頻微系統的需求。然而互連尺寸進一步縮小可以增加射頻電路設計的靈活性,因此在微型化、低損耗和低成本方面仍是重要的發展方向。此外,微型化的同時也給可靠性帶來了新的挑戰,但目前在可靠性方面的研究仍較少。在微型化、低損耗方面,目前有研究表明選用碳納米管(CNT)充當導體材料,相較于傳統導體銅、鎢、鋁受高頻下的趨膚效應影響小,整體性能均得到有效提升,同時碳納米管具有高熱導率和高載流能力,有利于提高系統整體的可靠性,但在制備工藝上仍有較高難度。

在散熱方面,隨著射頻微系統微型化的進一步發展和高功率固態器件集成,使得射頻微系統的熱流密度進一步提升,如何實現大功率、微型化的射頻微系統將是未來發展的難點之一。除了采用傳統Si基微流道和高效散熱集成架構設計,在高導熱新材料集成方面仍有很大的空間,例如近年來面向固態微波器件的金剛石散熱技術和金剛石微流道技術已經取得較好的進展,未來如能集成到射頻微系統工藝中,將有效提升射頻微系統的輸出功率。此外,智能熱管理技術的發展也將進一步提升系統的散熱能力。

在仿真與優化方面,高效仿真平臺對縮短研發周期、降低產品成本和提升電學與可靠性性能有著重要意義,但由于射頻微系統跨尺度、多層級、多物理場耦合的特殊性,實現高效的多場協同仿真仍是未來需重點解決的問題。近年來人工智能技術發展,有望推動模型甚至數據驅動的新一代快速仿真方法。此外,在設計方面,隨著新材料和新器件的發展,未來射頻微系統的仿真將跨越到設計-工藝協同優化(DTCO)和系統-工藝協同優化(STCO)。

最后,隨著偵干探通一體化電子技術的發展,多功能一體化集成也是射頻微系統發展的趨勢,除了在集成架構方面,還需要對射頻微系統的電路設計架構上延伸,滿足不同功能的可重構和智能化。此外,射頻與光電、數字、模擬等集成接口及其標準化也是射頻微系統未來走向“芯粒”集成需要考慮的內容。

Chrent總結射頻微系統是微波電路與系統從小型化發展到微型化的標志。高性能互連、高效仿真與優化、高密度集成架構等技術是射頻微系統進一步發展和應用的關鍵。隨著新材料、新型半導體器件、新工藝和新設計理論的發展,射頻微系統在工作頻率、輸出功率、集成度和成本等特性上仍將繼續突破,對小型化無人機、新一代戰機、航空航天、5G/6G移動通信、衛星通信、可穿戴裝備等對微型化要求較高的應用場景有著巨大潛力。

文章摘自:《微波學報》

作者:徐銳敏,王歡鵬,徐躍杭

-

集成電路

+關注

關注

5382文章

11396瀏覽量

360953 -

射頻

+關注

關注

104文章

5551瀏覽量

167582 -

半導體芯片

+關注

關注

60文章

915瀏覽量

70584

發布評論請先 登錄

相關推薦

機器視覺檢測系統的關鍵技術和應用場景

柔性制造系統的關鍵技術有哪些

機器視覺的關鍵技術有哪些

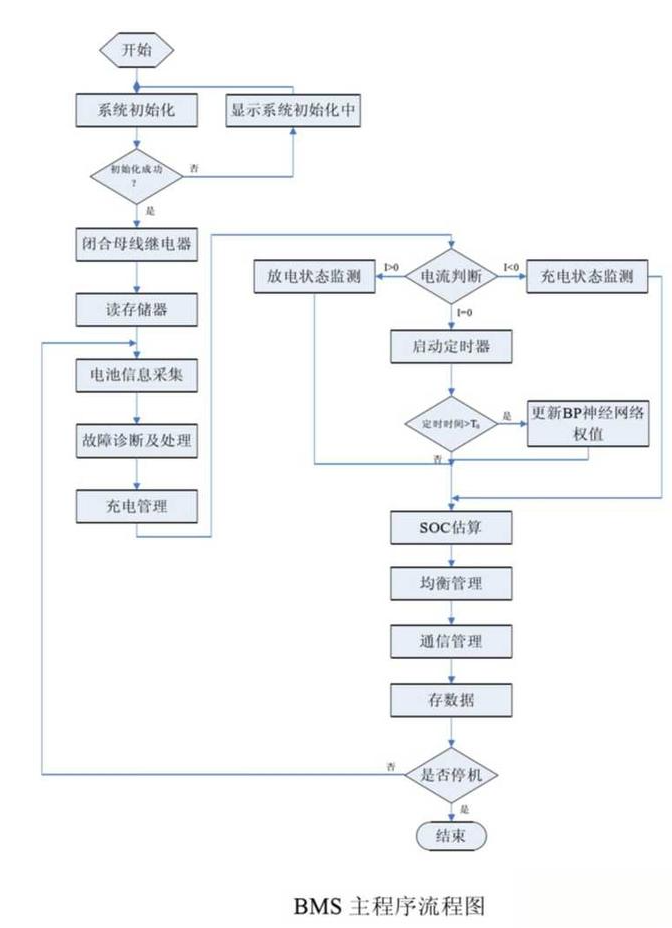

儲能BMS的關鍵技術是什么

矢量網絡分析儀的關鍵技術指標解讀

百度首席技術官王海峰解讀文心大模型的關鍵技術和最新進展

數字孿生關鍵技術及體系架構

淺談基于數字孿生的配電室關鍵技術研究

新型電力系統的智能裝備關鍵技術

射頻微系統關鍵技術進展及展望

射頻微系統關鍵技術進展及展望

評論