近日,業(yè)界傳來重要消息,臺積電已正式組建專注于扇出型面板級封裝(FOPLP)的團隊,并規(guī)劃建立小型試產(chǎn)線(mini line),標志著這家全球領(lǐng)先的半導(dǎo)體制造企業(yè)在芯片封裝技術(shù)領(lǐng)域邁出了重要一步。此舉不僅彰顯了臺積電在技術(shù)創(chuàng)新上的持續(xù)投入,也預(yù)示著芯片封裝行業(yè)即將迎來一場深刻的變革。

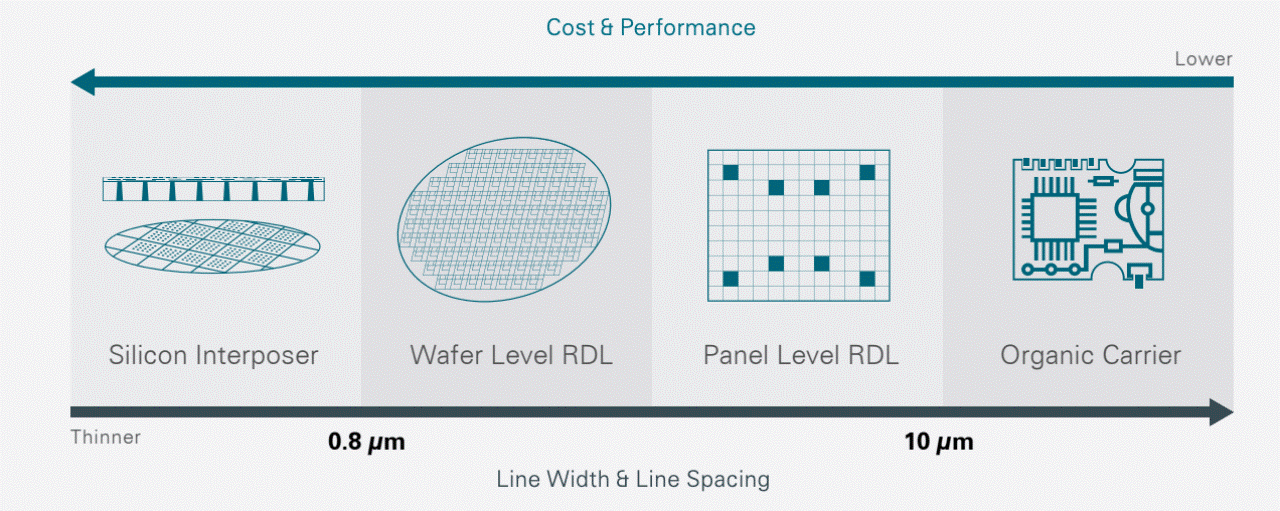

據(jù)知情人士透露,臺積電當前正在積極試驗的FOPLP技術(shù),其核心在于采用大型矩形基板替代傳統(tǒng)的圓形硅中介板。這一創(chuàng)新設(shè)計使得封裝尺寸顯著增大,據(jù)估算,其正在測試的矩形基板尺寸達到了510mm×515mm,這一尺寸下的可用面積是當前12英寸圓形晶圓的三倍多。這一變化不僅大幅提升了面積利用率,還有望顯著降低單位成本,為臺積電在激烈的市場競爭中贏得更多優(yōu)勢。

盡管目前FOPLP技術(shù)仍處于早期研發(fā)階段,距離商業(yè)化應(yīng)用尚需數(shù)年時間,但這一技術(shù)轉(zhuǎn)變對于臺積電乃至整個半導(dǎo)體行業(yè)而言都具有里程碑式的意義。此前,臺積電曾認為使用矩形基板進行封裝存在諸多挑戰(zhàn),但隨著技術(shù)的不斷進步和市場的迫切需求,臺積電毅然決然地選擇了這條充滿挑戰(zhàn)的道路。

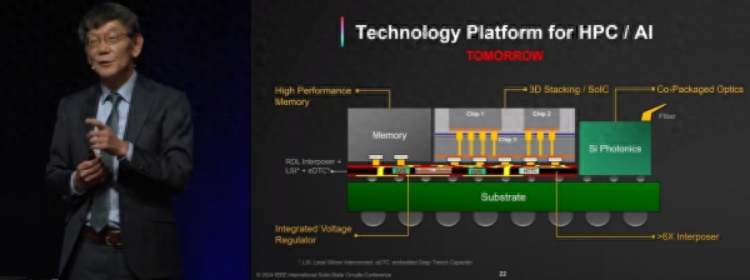

分析人士指出,臺積電發(fā)展的FOPLP技術(shù)可以被視為矩形的InFO(整合扇出型封裝)技術(shù)的升級版,它不僅繼承了InFO的低單位成本和大尺寸封裝的優(yōu)勢,還具備進一步整合臺積電3D fabric平臺上其他技術(shù)的潛力。這意味著,F(xiàn)OPLP技術(shù)有望在未來發(fā)展成為一種集高性能、低成本、高集成度于一體的先進封裝解決方案,為臺積電在高端芯片市場提供強有力的支持。

值得注意的是,F(xiàn)OPLP技術(shù)的潛在應(yīng)用領(lǐng)域十分廣泛,特別是在AI GPU領(lǐng)域展現(xiàn)出了巨大的潛力。目前,臺積電已將這一技術(shù)的目標客戶鎖定為英偉達等全球領(lǐng)先的AI芯片制造商。隨著AI技術(shù)的快速發(fā)展和應(yīng)用場景的不斷拓展,對于高性能、高集成度的AI GPU芯片的需求也將持續(xù)增長。因此,F(xiàn)OPLP技術(shù)的成功商業(yè)化無疑將為臺積電帶來更為廣闊的市場空間和更為豐厚的利潤回報。

展望未來,隨著FOPLP技術(shù)的不斷成熟和完善,我們有理由相信,這一創(chuàng)新技術(shù)將在未來幾年內(nèi)逐步走向市場,為半導(dǎo)體封裝行業(yè)帶來新的活力和機遇。同時,臺積電也將憑借其在技術(shù)創(chuàng)新和市場拓展方面的卓越表現(xiàn),繼續(xù)引領(lǐng)全球半導(dǎo)體行業(yè)的發(fā)展潮流。

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27063瀏覽量

216488 -

臺積電

+關(guān)注

關(guān)注

44文章

5611瀏覽量

166161 -

芯片封裝

+關(guān)注

關(guān)注

11文章

480瀏覽量

30567

發(fā)布評論請先 登錄

相關(guān)推薦

臺積電布局FOPLP技術(shù),推動芯片封裝新變革

臺積電布局FOPLP技術(shù),推動芯片封裝新變革

評論