DDR5標準JESD79-5文件中沒有明確的控制阻抗建議,DDR4時代基本內存條上時鐘阻抗還是跟著芯片、主板走的70-80歐姆。線寬相對而言比較細。不知道你開始使用DDR5沒有,你有關注過DDR5內存條上的時鐘走線嗎?

DDR5內存條上Clock走線突然變粗了,阻抗只有50ohm。旁邊細線就是地址控制信號,在DDR4上,時鐘走線和地址信號粗細差不多,單根控制阻抗值也是差不多40歐姆的。

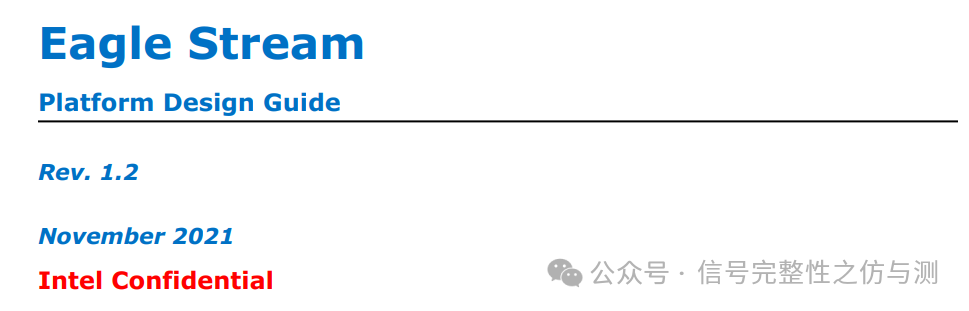

然而,我們看DDR5的平臺,以Intel EGS為例,差不多兩年前新出的DDR5要求,主板端Clock單根依舊是按照40歐姆,差分差不多75歐姆控制阻抗。

那為什么CPU、主板、甚至內存插槽走勢按照75歐及以上的阻抗來控制,而內存條要控制50歐姆呢?而且,內存條本身就是一個很小的尺寸,空間夠緊張了,還有把線寬調到8-9mil來控制差分50的阻抗,你想過原因嗎?

這個問題也咨詢過內存模組廠商,答復是按照高速傳輸線理論,DDR5信號電壓更低、速率更高,使用更低的特征阻抗在信號時延和串擾方面會表現更好。

我有點疑惑,信號時延主要是跟走線長度和板材介電常數關系大。阻抗會影響嗎?

下面一起來看看究竟是什么原因。

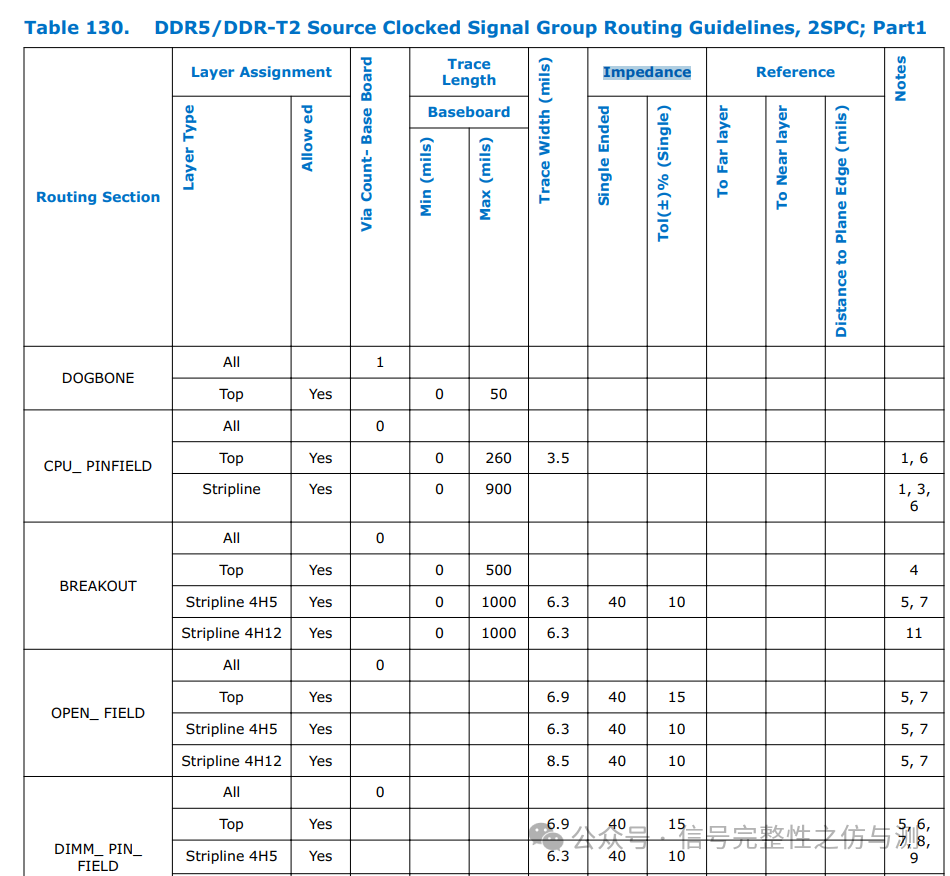

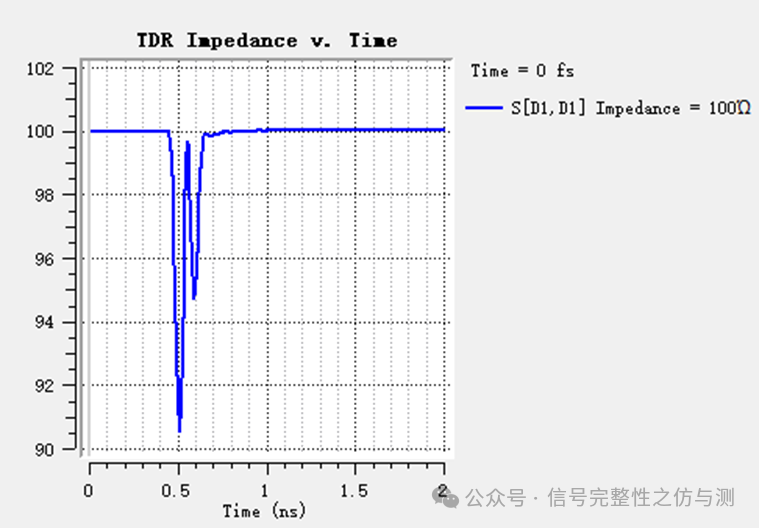

確認一下CPU的Package阻抗,通過TDR顯示,確實是75Ω左右。

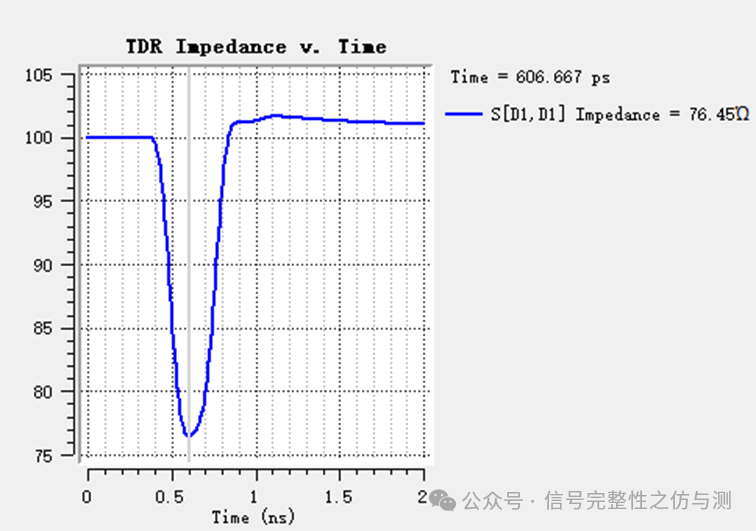

再看看主板走線的阻抗,主板阻抗值73-75ohm。

內存連接器呢?內存連接器的阻抗值是90-100ohm,這是SMT的,沒有stub,連接器基本都是按照單根50歐姆來設計。

最后,看看內存條上走線的阻抗,內存條走線的阻抗值50-60ohm。

為什么要換軟件?大家知道,內存條是多顆粒的,提取的S參數是一個多端口的,此時在ADS里面總是顯示不正常,可能我沒玩明白,但是Circuit看阻抗肯定是最優選擇,那就不折騰了。

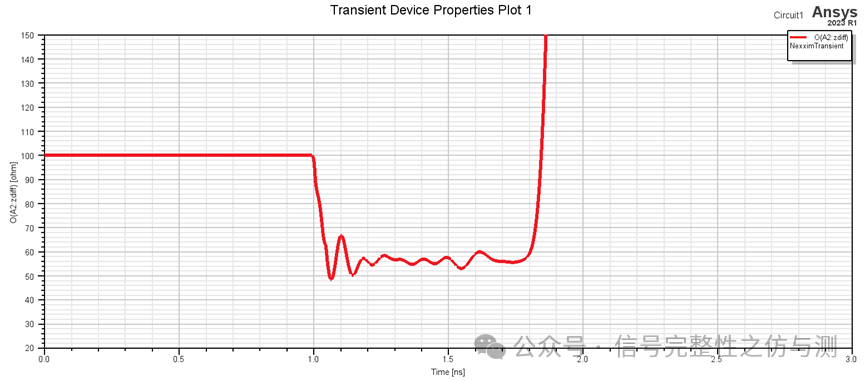

另外,我們還做了一個方案,假設內存條還是按照DDR4時代控制阻抗,會是什么結果。

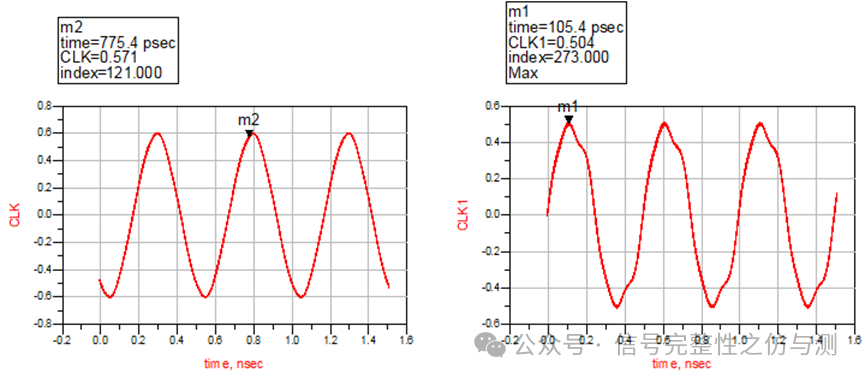

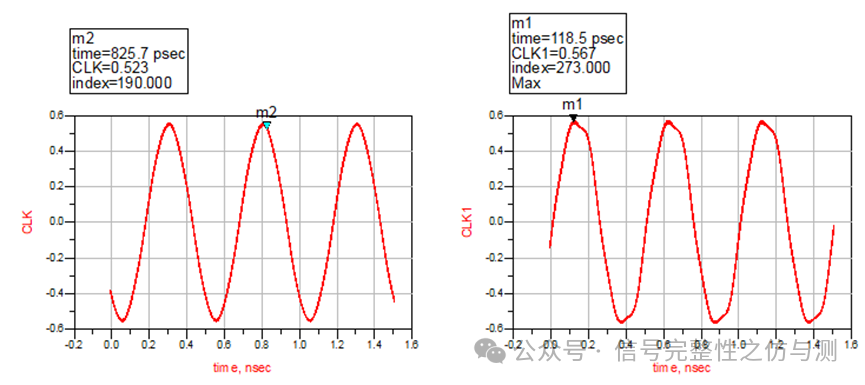

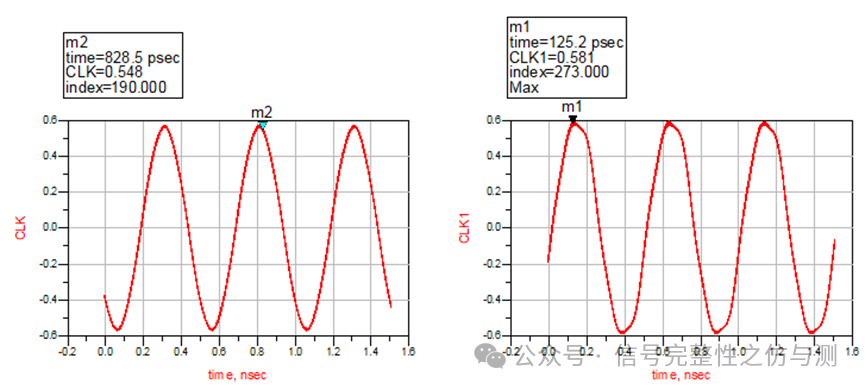

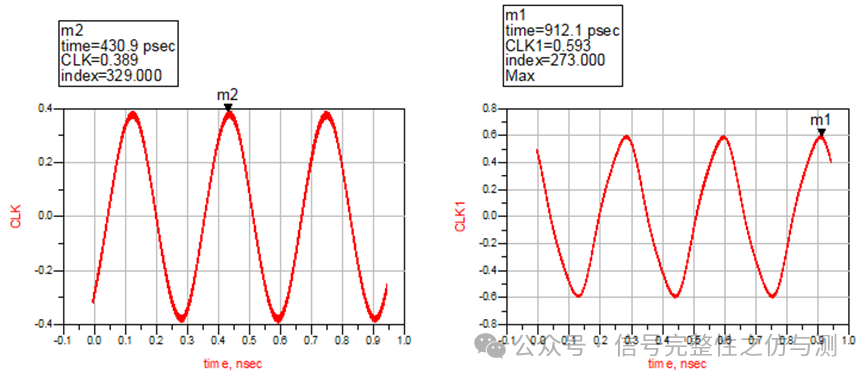

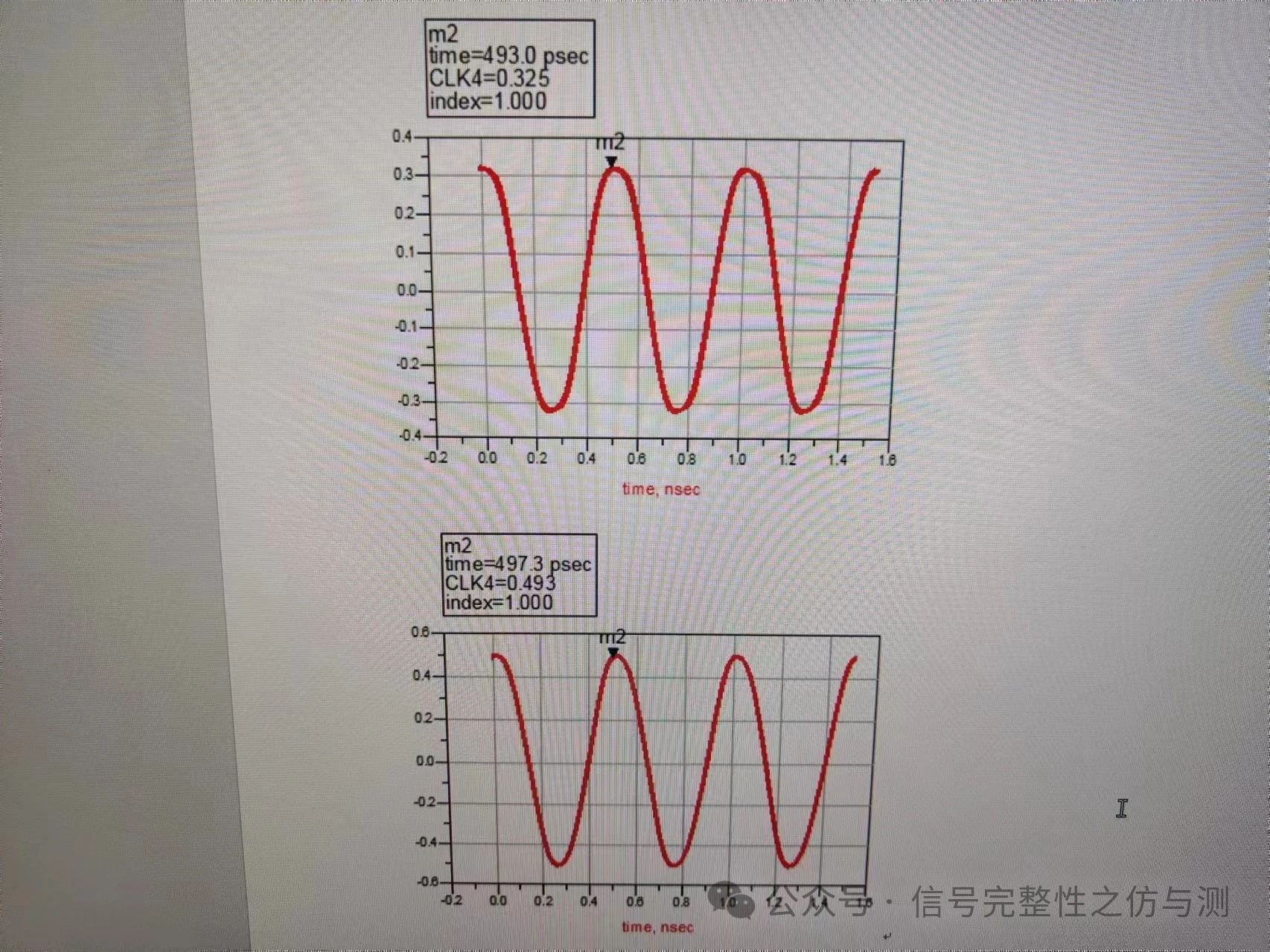

正常4-4.8Gbps的DDR5速率

①主板阻抗75ohm,內存阻抗50ohm

②主板阻抗75ohm,內存阻抗75ohm

③主板阻抗50ohm,內存阻抗75ohm

④主板阻抗50ohm,內存阻抗50ohm

也就是說,在速率比較低時,DDR5的Clock阻抗要求比較寬松。就算與主板不匹配,也沒有任何問題。

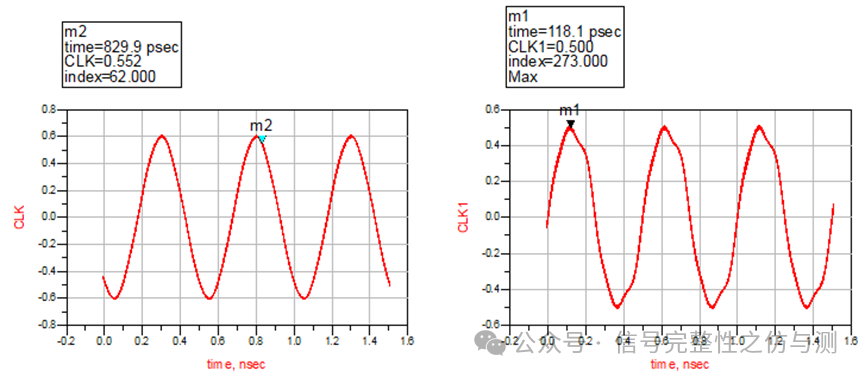

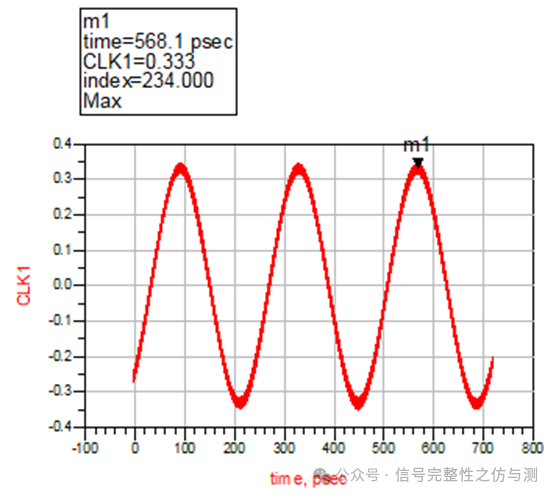

內存速率提升到6.4Gbps

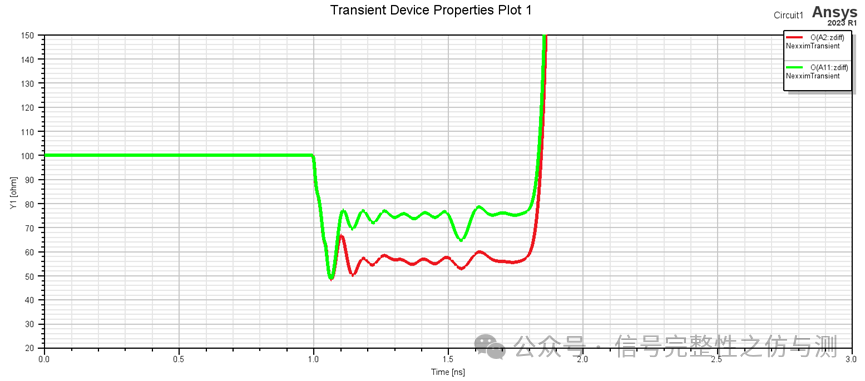

如果內存阻抗使用與主板一致的75ohm,顆粒1的差分電壓降至329mV

同等條件下,將內存阻抗降至50ohm,顆粒1和顆粒2電壓均能抬升60mV。

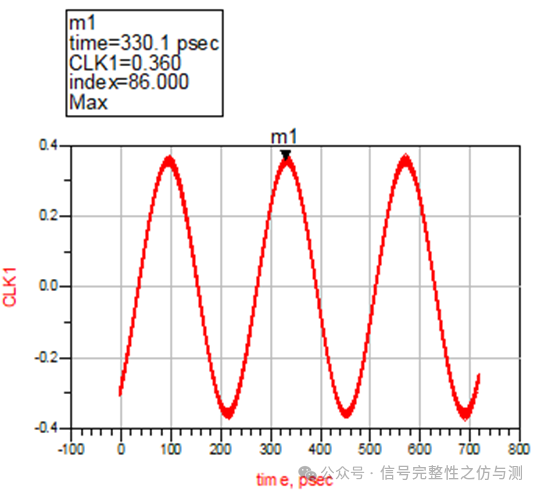

內存速率提升到8.4Gbps

顆粒1的差分電壓降至333mV,比較臨界。

同等條件下,將內存阻抗降至50ohm,同樣電壓有提升。

值得注意的是,對于UDIMM,這個設計是不適合8400速率的,這里只是借用這個走線驗證不同阻抗對電壓的影響。

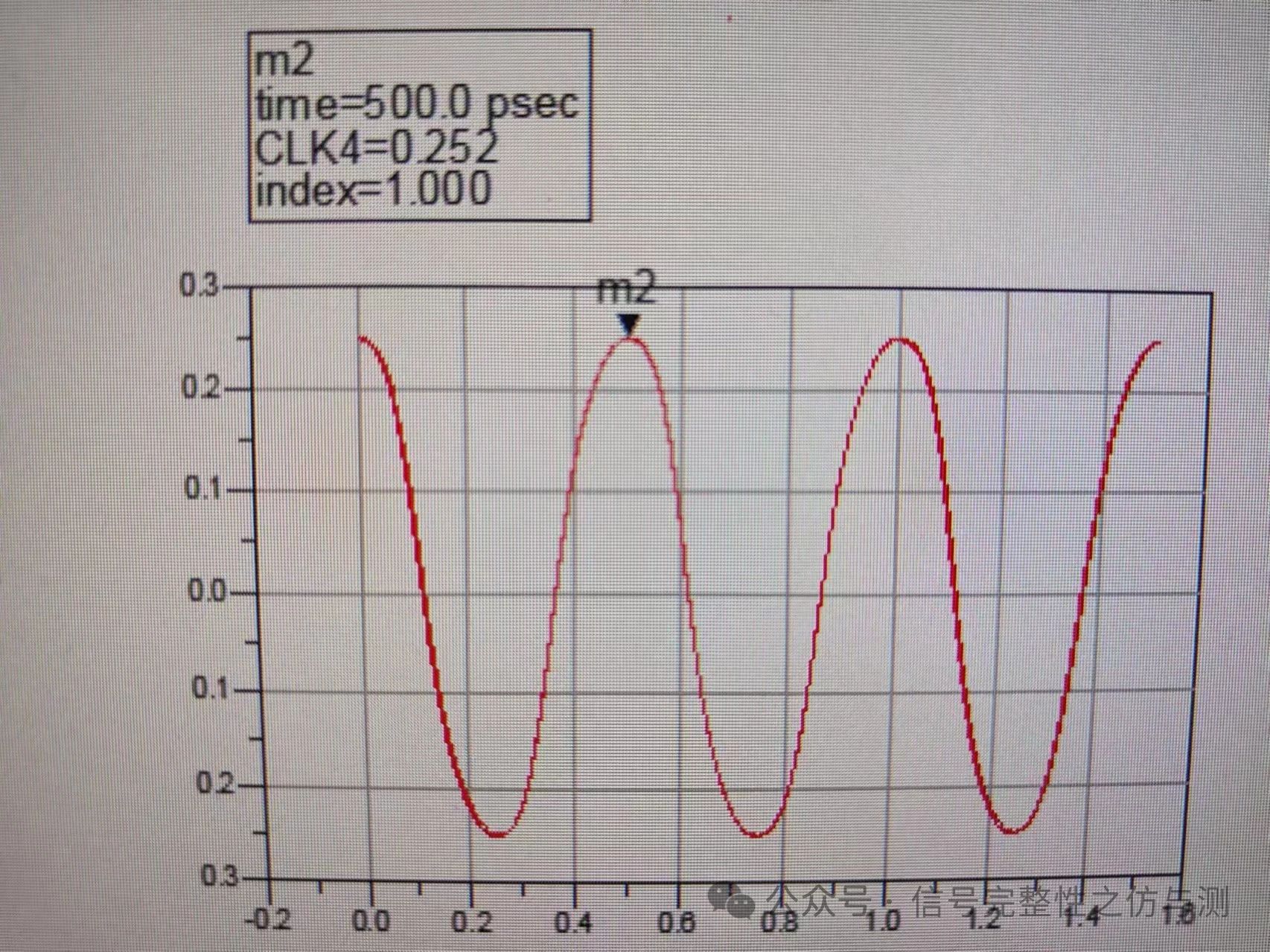

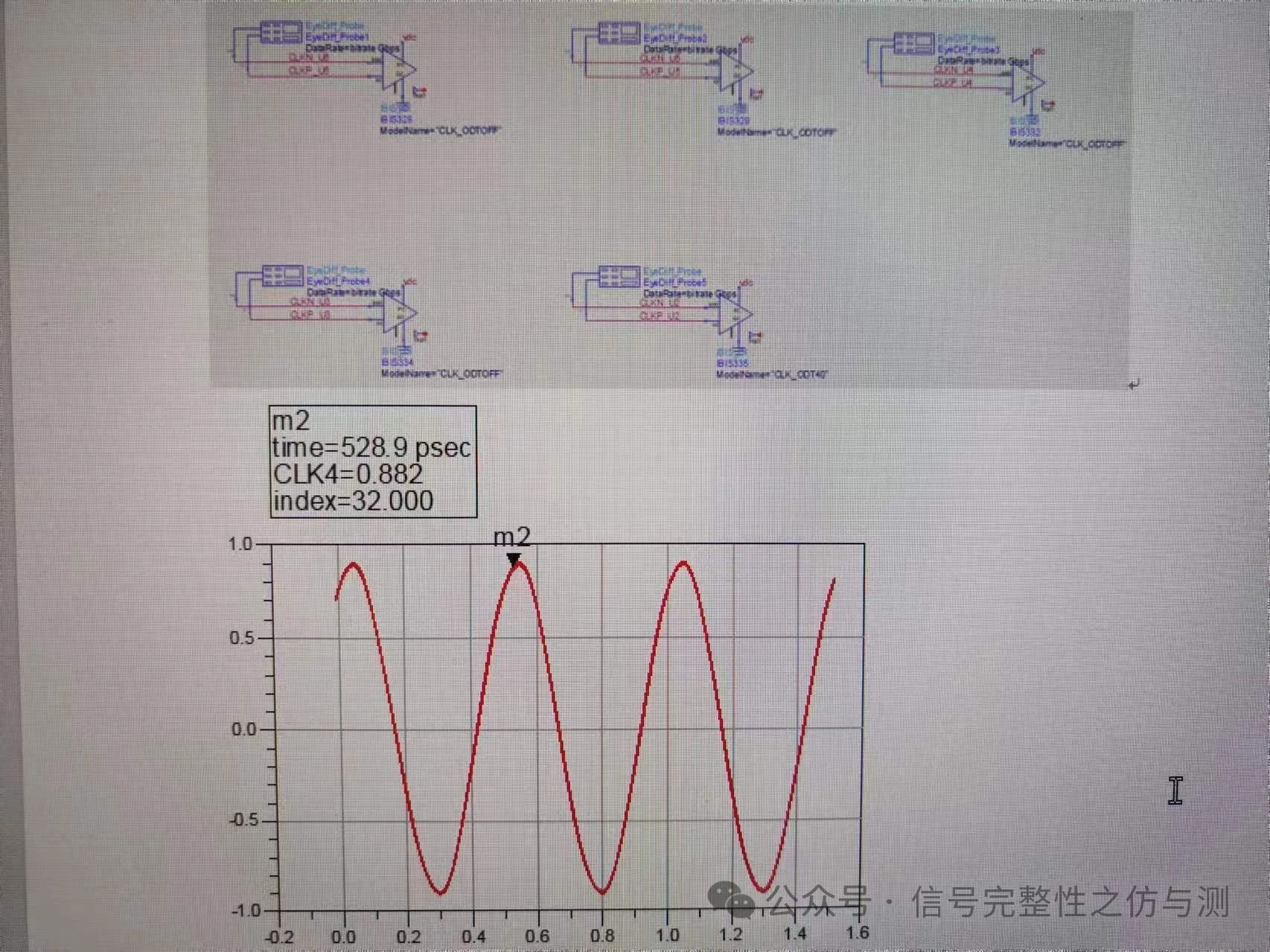

UDIMM如此,那RDIMM呢,RDIMM的時鐘已經跟CPU、主板端沒什么關系了,是由RCD芯片發出的。RCD出來后再經過5顆顆粒。

末端顆粒CLK電壓只有252mV,顯然不滿足要求。

逐漸順次關閉顆粒的ODT

只開最后一個顆粒ODT

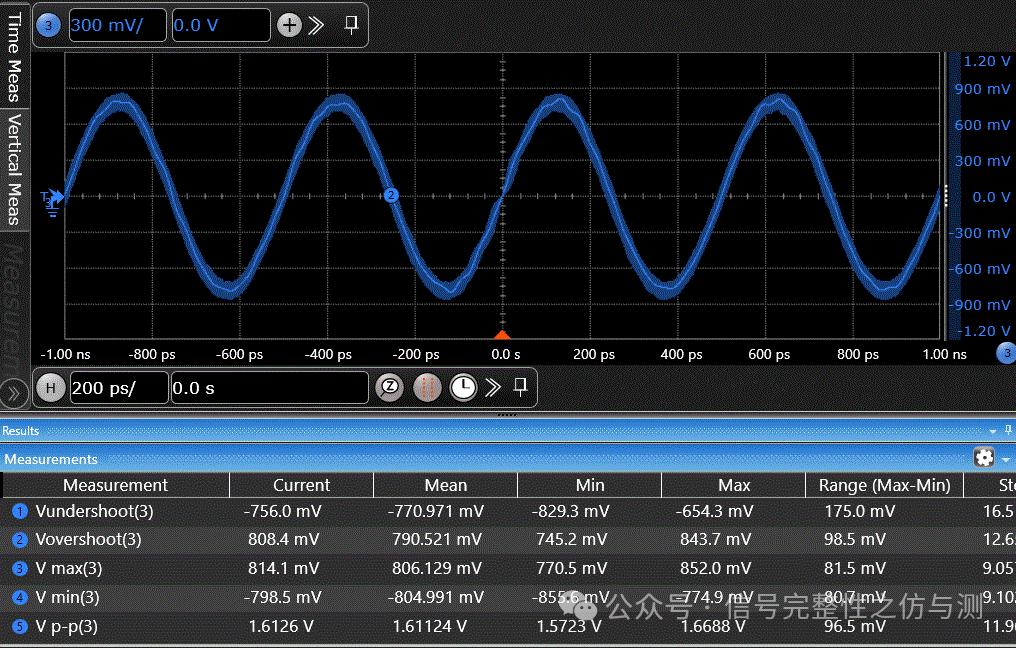

實際上在RDIMM上最后一個顆粒測試的max值也是800多mV,說明仿真設置是對的,后面按照這個配置來設置。

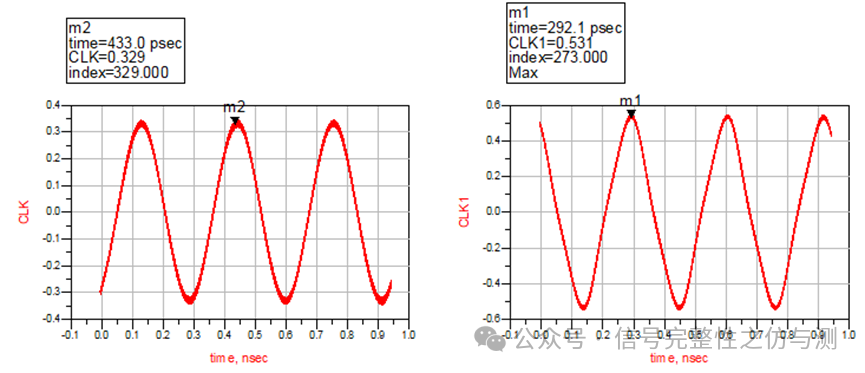

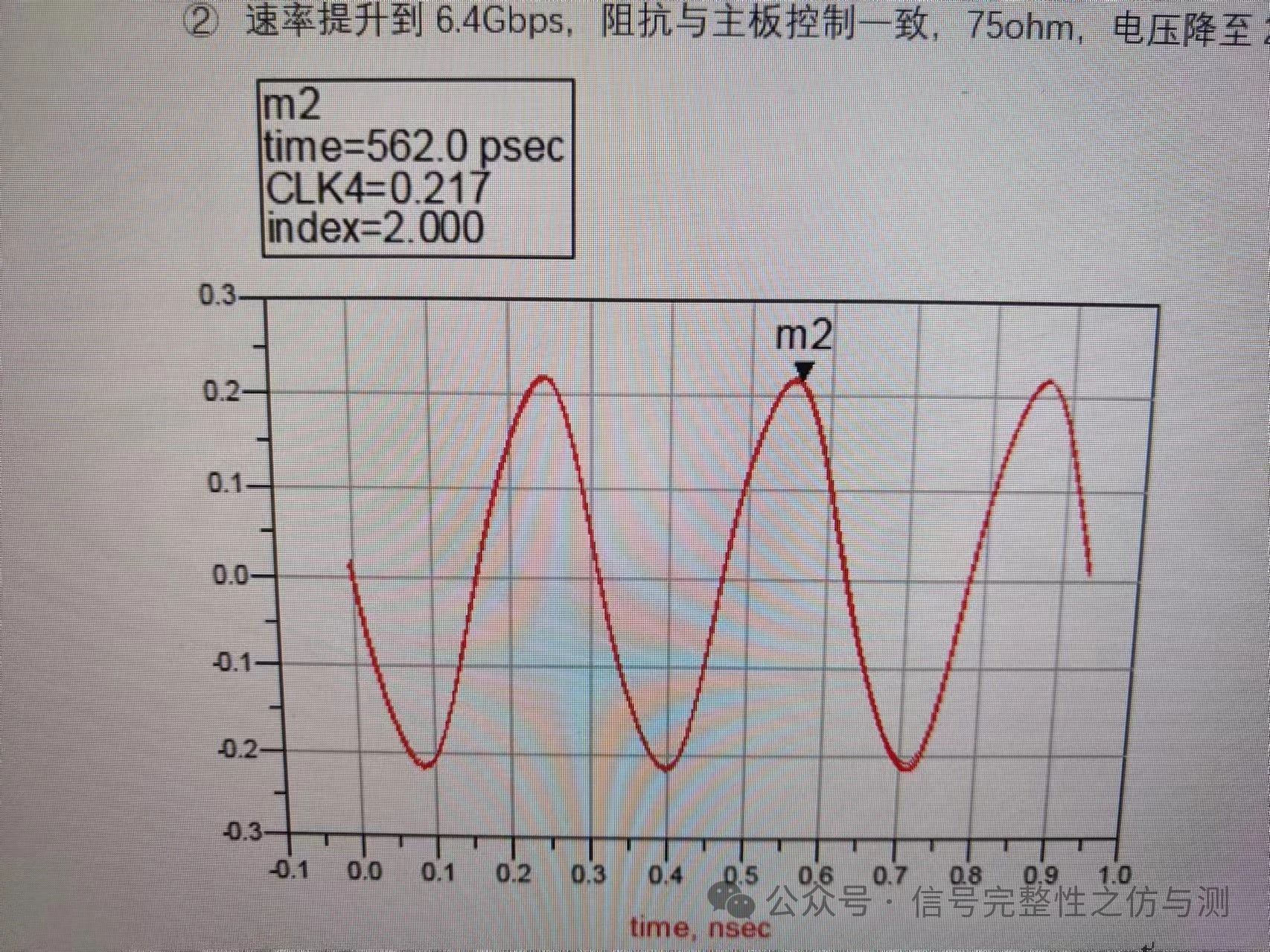

RDIMM內存速率提升到6.4Gbps

電壓降至497mV

此時如果阻抗與主板控制一致,75Ω,電壓降至217mV

速率恢復以前,內存阻抗與主板控制一致,75Ω

電壓值也完全恢復了。

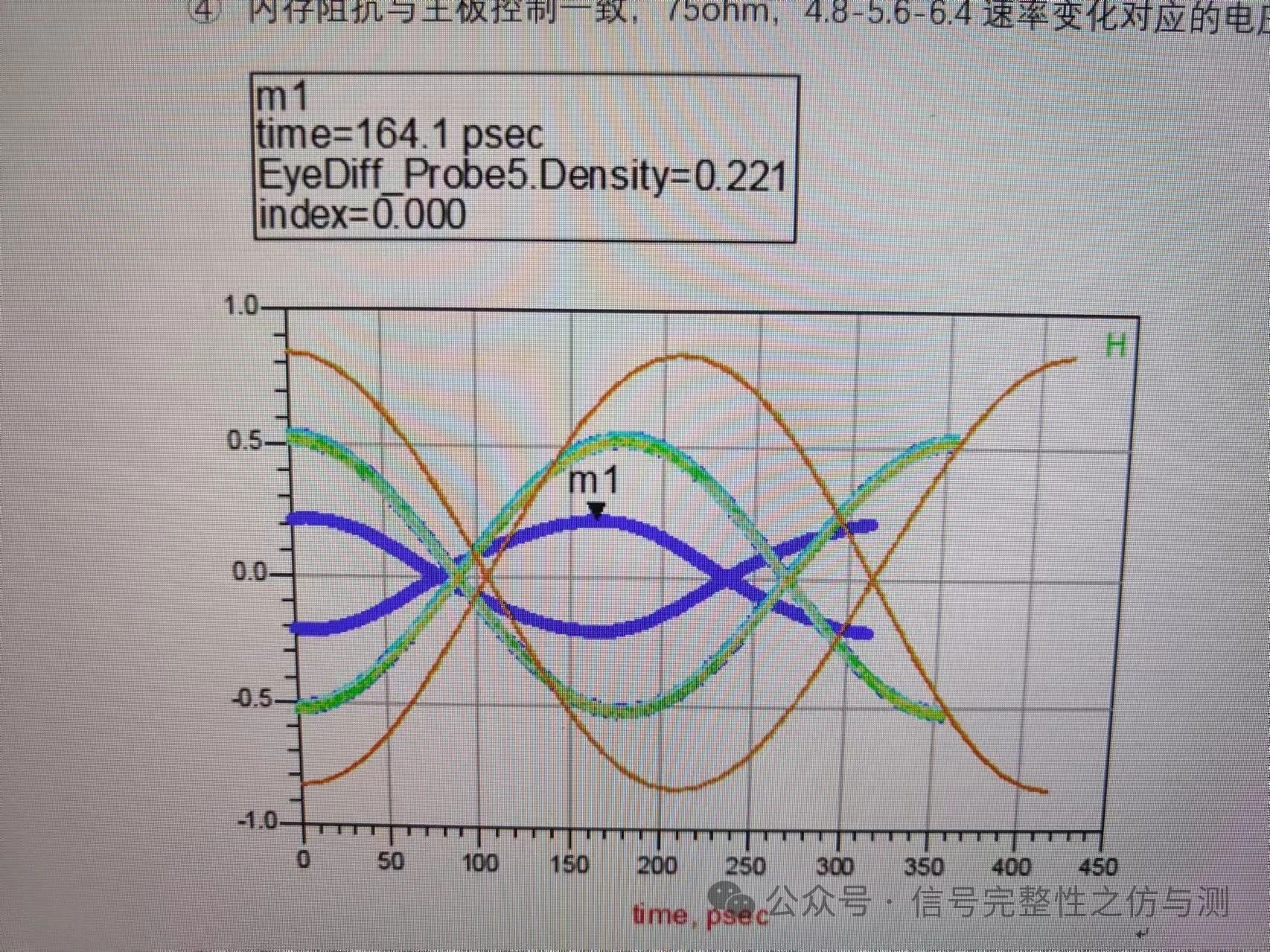

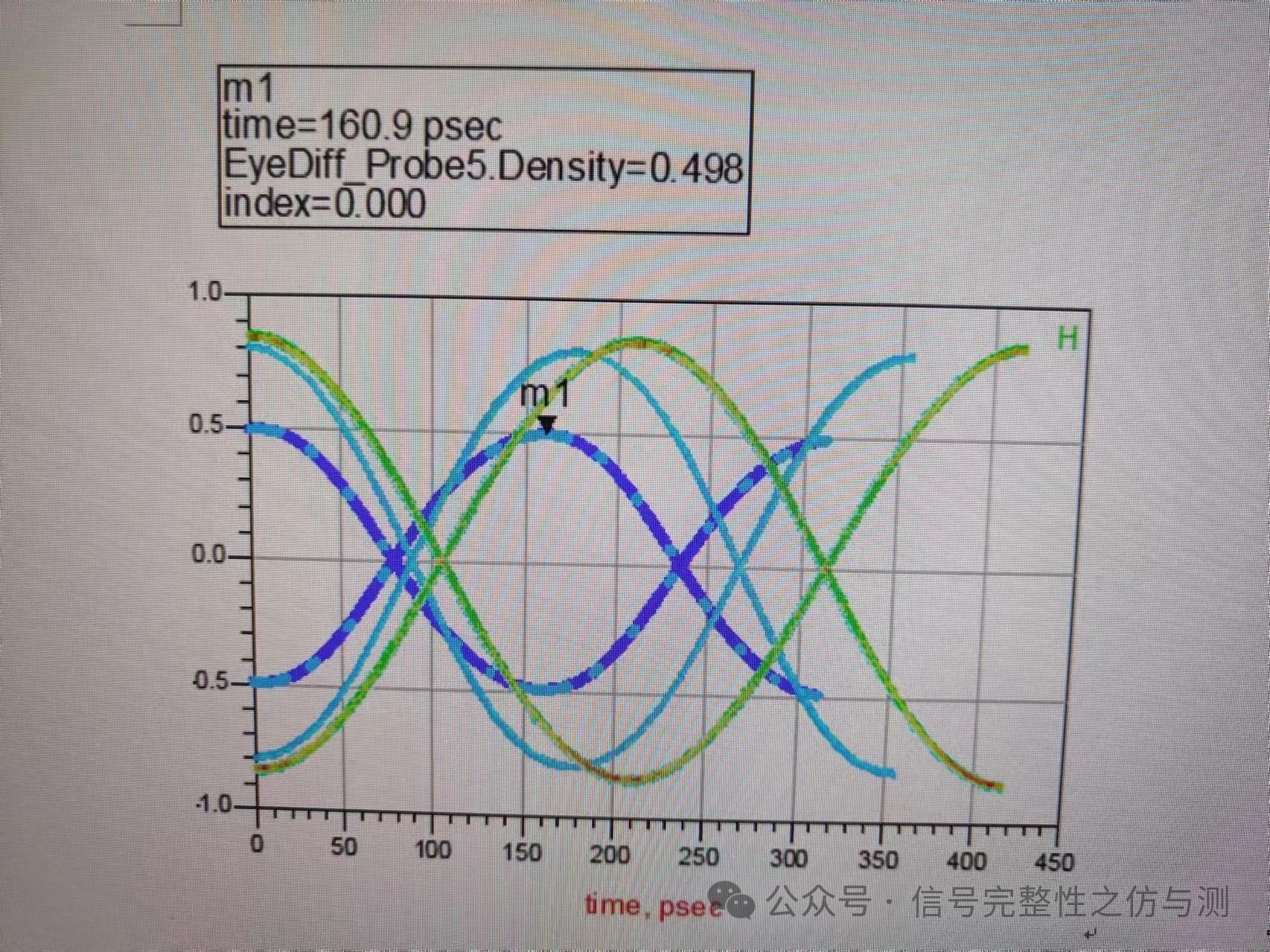

那么,內存阻抗與主板控制一致,75Ω,速率在4.8-5.6-6.4變化時對應的電壓變化是什么樣呢?

內存阻抗與主板控制不一致,50歐姆,速率在4.8-5.6-6.4變化時對應的電壓變化是什么樣呢?

結果不言而喻!

因此,為了適應DDR5更高速率,內存的阻抗設計為50ohm,通過更低的阻抗來減少信號的衰減和失真。

-

cpu

+關注

關注

68文章

10702瀏覽量

209361 -

時鐘

+關注

關注

10文章

1673瀏覽量

130956 -

50歐姆

+關注

關注

0文章

5瀏覽量

6208 -

DDR5

+關注

關注

1文章

409瀏覽量

24035

原文標題:突破傳統:DDR5時鐘阻抗50歐姆的革新之路

文章出處:【微信號:si-list,微信公眾號:高頻高速研究中心】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

嘉合勁威布局導入DDR5內存新技術 明年量產

新一代DDR5內存模組密集發布,支持DDR5 CPU隨后就到!

FPGA對DDRSDRAM內存條的控制

SK海力士最新DDR5 EEC內存條,性能有巨大的提升

SK海力士最新DDR5 EEC內存條展示,采用1znm內存制造工藝制造

內存條ddr4和顯卡ddr5

國內廠商已開始布局DDR5內存明年量產

DDR5內存將面向數據中心市場

Longsys DDR5內存條預計在2022年進入量產階段

臺電追風A60 DDR5內存條全面上市

研華工控機購買指南:DDR3、DDR4、DDR5怎么選?如何選擇內存條?

DDR5內存條上的時鐘走線

DDR5內存條上的時鐘走線

評論