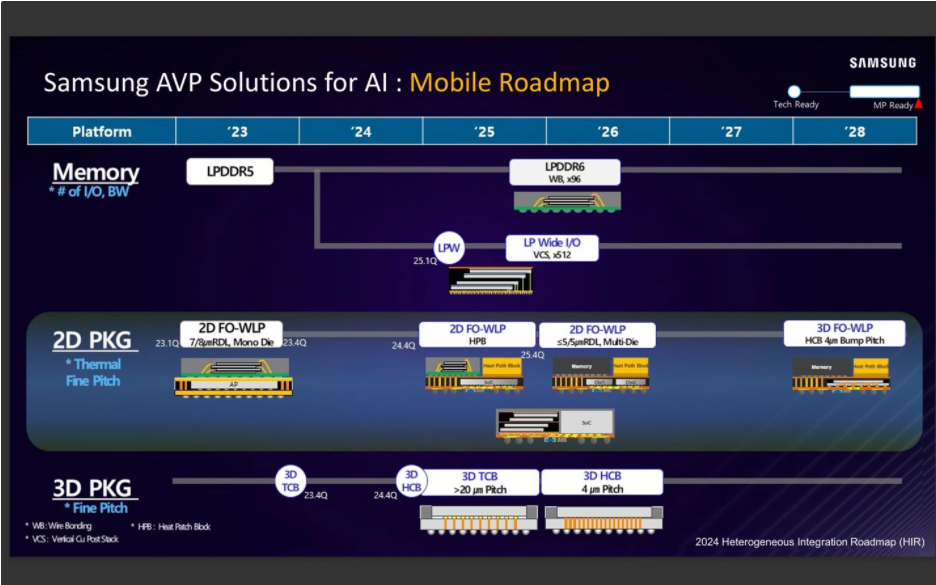

7月17日,三星電子公布了其雄心勃勃的2024年異構(gòu)集成路線圖,其中一項(xiàng)關(guān)鍵研發(fā)成果引發(fā)了業(yè)界廣泛關(guān)注——一款名為L(zhǎng)P Wide I/O的創(chuàng)新型移動(dòng)內(nèi)存即將面世。這款內(nèi)存不僅預(yù)示著存儲(chǔ)技術(shù)的又一次飛躍,還可能與公司此前提及的LLW(Low Latency Wide I/O)內(nèi)存存在某種關(guān)聯(lián),盡管兩者之間的確切關(guān)系尚待揭曉。

據(jù)路線圖規(guī)劃,LP Wide I/O內(nèi)存預(yù)計(jì)將于2025年第一季度在技術(shù)層面達(dá)到成熟狀態(tài),隨后在同年下半年至2026年期間做好量產(chǎn)準(zhǔn)備,正式邁向市場(chǎng)。其核心亮點(diǎn)在于其單封裝位寬達(dá)到了驚人的512bit,這一數(shù)字幾乎是目前高端HBM內(nèi)存位寬的一半,遠(yuǎn)遠(yuǎn)超出了當(dāng)前LPDDR5內(nèi)存的四通道共64bit規(guī)格,即便是未來的LPDDR6內(nèi)存,其位寬也僅規(guī)劃為96bit。

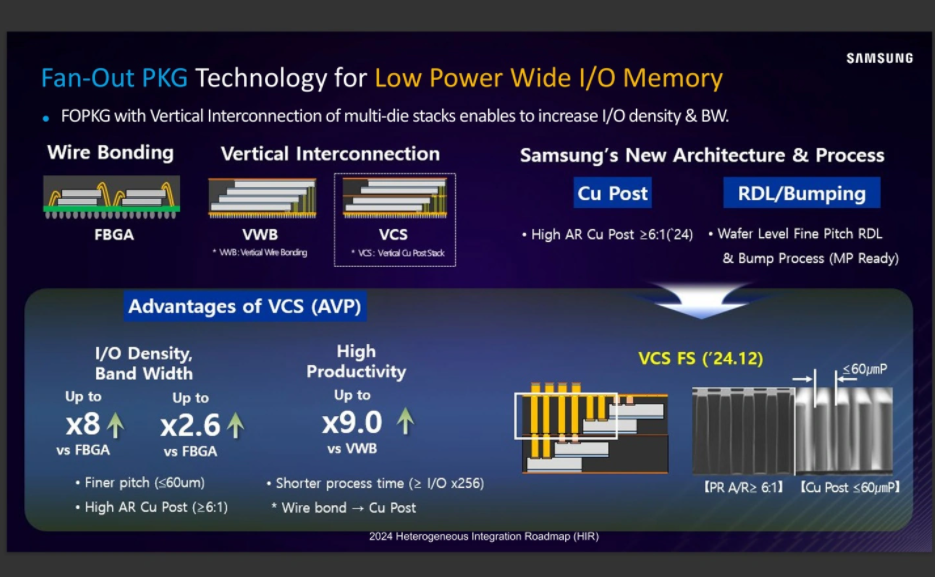

如此巨大的位寬提升,意味著LP Wide I/O內(nèi)存將能夠提供前所未有的內(nèi)存帶寬,這對(duì)于日益增長(zhǎng)的設(shè)備端AI應(yīng)用等高性能需求場(chǎng)景而言,無疑是巨大的福音。為了實(shí)現(xiàn)這一突破性的位寬設(shè)計(jì),三星電子不得不面對(duì)如何在有限空間內(nèi)堆疊DRAM芯片的挑戰(zhàn),而傳統(tǒng)的HBM所采用的TSV(硅通孔)技術(shù)顯然并不適合移動(dòng)內(nèi)存的場(chǎng)景。

為此,三星電子獨(dú)創(chuàng)了VCS(Vertical Cu Post Stack)垂直互聯(lián)技術(shù),這一技術(shù)巧妙地結(jié)合了扇出封裝與垂直通道的概念,與SK海力士的VFO技術(shù)有異曲同工之妙,但在生產(chǎn)效率與性能上據(jù)稱有顯著提升。三星電子自豪地宣稱,其VCS技術(shù)相比傳統(tǒng)引線鍵合技術(shù),在I/O密度和帶寬上分別實(shí)現(xiàn)了8倍和2.6倍的增長(zhǎng);而與類似的VWB(Vertical Wire Bonding,疑似指代SK海力士的VFO技術(shù))相比,VCS技術(shù)的生產(chǎn)效率更是高達(dá)9倍,展現(xiàn)出了巨大的技術(shù)優(yōu)勢(shì)。

值得注意的是,三星電子還透露,作為其內(nèi)存產(chǎn)品線的另一重要成員,LPDDR6內(nèi)存同樣預(yù)計(jì)將在2025至2026年期間達(dá)到量產(chǎn)就緒狀態(tài),進(jìn)一步豐富了公司的移動(dòng)內(nèi)存產(chǎn)品線,為市場(chǎng)帶來更多選擇。這一系列動(dòng)作無疑表明了三星電子在推動(dòng)移動(dòng)存儲(chǔ)技術(shù)革新方面的堅(jiān)定決心與強(qiáng)大實(shí)力。

-

三星電子

+關(guān)注

關(guān)注

34文章

15856瀏覽量

180934 -

內(nèi)存

+關(guān)注

關(guān)注

8文章

3004瀏覽量

73901 -

移動(dòng)內(nèi)存

+關(guān)注

關(guān)注

0文章

9瀏覽量

7273

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

未來10年智能傳感器怎么發(fā)展?美國(guó)發(fā)布最新MEMS路線圖

三星電子計(jì)劃在2026年推出最后一代10nm級(jí)工藝1d nm

三星開始量產(chǎn)其最薄LPDDR5X內(nèi)存產(chǎn)品,助力端側(cè)AI應(yīng)用

2024學(xué)習(xí)生成式AI的最佳路線圖

三星電子計(jì)劃2025~2026年推出LP Wide I/O內(nèi)存

三星展望2027年:1.4nm工藝與先進(jìn)供電技術(shù)登場(chǎng)

三星將于今年內(nèi)推出3D HBM芯片封裝服務(wù)

三星公布最新工藝路線圖

三星芯片制造技術(shù)路線圖出爐,意強(qiáng)化AI芯片代工市場(chǎng)競(jìng)爭(zhēng)力

iPhone升級(jí)路線圖曝光:1年后才配12G內(nèi)存,2026年有折疊屏

事關(guān)衛(wèi)星物聯(lián)網(wǎng)!LoRaWAN 2027 發(fā)展路線圖重磅公布

三星電子公布2024年異構(gòu)集成路線圖,LP Wide I/O移動(dòng)內(nèi)存即將面世

三星電子公布2024年異構(gòu)集成路線圖,LP Wide I/O移動(dòng)內(nèi)存即將面世

評(píng)論