本文主要講解的是FPGA高速收發(fā)器的來源,著重從三個(gè)方面解析,可能部分理解會(huì)存在有錯(cuò)誤,想要不一致的可以來評(píng)論區(qū)交流哦。

01回顧其余接口

首先應(yīng)該了解這種接口出現(xiàn)的原因,為什么會(huì)有這種接口出現(xiàn),就拿ADC芯片的接口舉例吧。

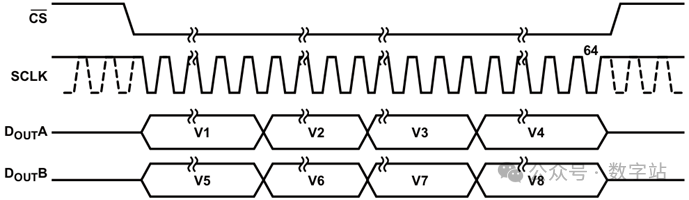

下圖是ad7606芯片的串行數(shù)據(jù)傳輸模式的時(shí)序圖,像這種采樣率較低,一般小于1MHz。一般使用spi這種低速接口即可,也是出現(xiàn)比較早的接口。

圖1 ad7606時(shí)序圖

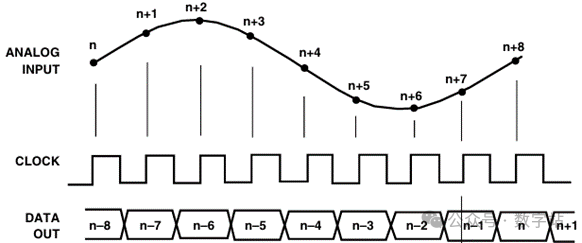

下圖ad9226的時(shí)序圖,接口包含一根時(shí)鐘線CLOCK和一組數(shù)據(jù)線DATA OUT,每個(gè)時(shí)鐘傳輸一個(gè)數(shù)據(jù),時(shí)鐘頻率最大可以達(dá)到65MHz。

圖2 ad9226時(shí)序圖

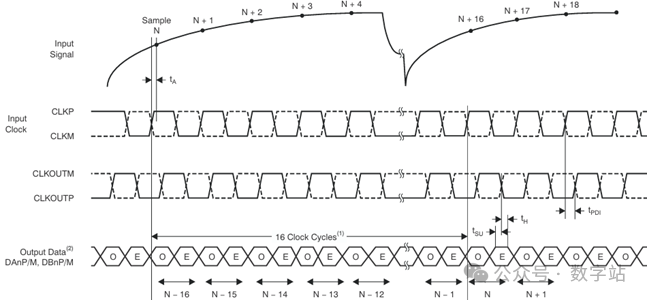

之后ADC芯片的采樣率進(jìn)一步提升,高于100MHz,為了提高數(shù)據(jù)傳輸?shù)姆€(wěn)定性,將時(shí)鐘和數(shù)據(jù)都變?yōu)?strong>差分信號(hào),增加抗干擾能力。如下圖是ads4225的LVDS接口時(shí)序圖。

圖3 ADS4225的LVDS接口時(shí)序圖

上述ad9226和ads4225的LVDS并行接口,時(shí)鐘線和數(shù)據(jù)線都要保證等長(zhǎng)。

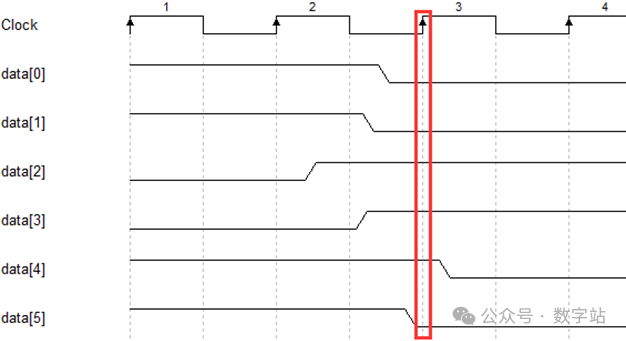

舉個(gè)例子,如下圖所示,在時(shí)鐘上升沿采集data的數(shù)據(jù),由于data數(shù)據(jù)線并沒有嚴(yán)格等長(zhǎng),data[2]的線比較短,第二個(gè)時(shí)鐘上升沿之后一段時(shí)間就傳輸?shù)紽PGA的端口寄存器了,data[4]的走線比較長(zhǎng),第三個(gè)時(shí)鐘上升沿之后都沒有傳輸?shù)紽PGA的端口寄存器,那么在clk第三個(gè)時(shí)鐘上升沿會(huì)采集到錯(cuò)誤數(shù)據(jù)。這就是為什么數(shù)據(jù)線和時(shí)鐘線均要做等長(zhǎng)的原因。

這種少數(shù)走線差別可以通過FPGA的input delay進(jìn)行約束,需要計(jì)算每根線的PCB走線延遲,輸出寄存器延時(shí)等等,會(huì)比較麻煩,并且不能對(duì)代碼進(jìn)行移植,所以對(duì)于這種并行傳輸?shù)慕涌谠谠O(shè)計(jì)PCB時(shí)數(shù)據(jù)線和時(shí)鐘線必須做等長(zhǎng)處理。

圖4 并行數(shù)據(jù)傳輸

但LVDS的數(shù)據(jù)線和時(shí)鐘線都是差分信號(hào),導(dǎo)致數(shù)據(jù)線很多,等長(zhǎng)處理很麻煩,但是還能有效果。比如時(shí)鐘頻率200MHz,那么數(shù)據(jù)只要在5ns之內(nèi)能夠穩(wěn)定傳輸?shù)捷斎爰拇嫫饕矝]有問題,即使每根走線之間有點(diǎn)差距,也問題不大。

但如果時(shí)鐘頻率繼續(xù)增加,就要求增加走線等長(zhǎng)的精度。當(dāng)數(shù)據(jù)傳輸速率大于2Gbps時(shí),時(shí)鐘周期小于0.5ns,此時(shí)即使微小的等長(zhǎng)差距也會(huì)引發(fā)錯(cuò)誤,甚至無法完成這樣的PCB布線。

在這種傳輸速率下,并行接口將不再合適,進(jìn)而推出了高速串行接口。

高速串行接口取消了時(shí)鐘線,只有一對(duì)差分?jǐn)?shù)據(jù)線,接收端通過CDR技術(shù)從串行數(shù)據(jù)中恢復(fù)時(shí)鐘信號(hào),之后將數(shù)據(jù)與時(shí)鐘同步給用戶。像PCIE、JE204B接口均是高速串行接口。

使用串行接口就可以避免時(shí)鐘同步和多位寬數(shù)據(jù)等長(zhǎng)問題,但是對(duì)于恢復(fù)時(shí)鐘和數(shù)據(jù)接收難度就增大了,發(fā)展到如今,高速串行接口也已經(jīng)很成熟了。

02FPGA中其余接口

FPGA內(nèi)部包含普通bank和gt bank兩種,后者就是高速收發(fā)器所在bank。xilinx的芯片根據(jù)架構(gòu)不同,包含不同類型的bank,其中A7只有HR bank,而K7除此之外還包含HP bank。下文將展示這些普通bank能夠達(dá)到的數(shù)據(jù)傳輸速率。

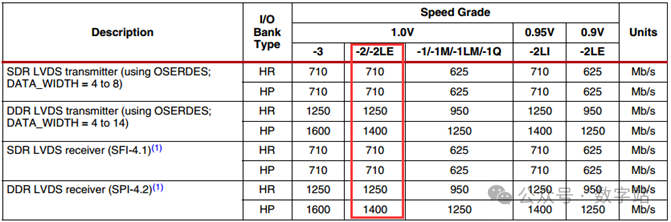

如下圖所示,以K7為例,平常使用芯片速度等級(jí)大多為-2,因此以-2舉例。HP和HR bank的單沿?cái)?shù)據(jù)傳輸速率均可以達(dá)到710Mb/s。

圖5 接口性能

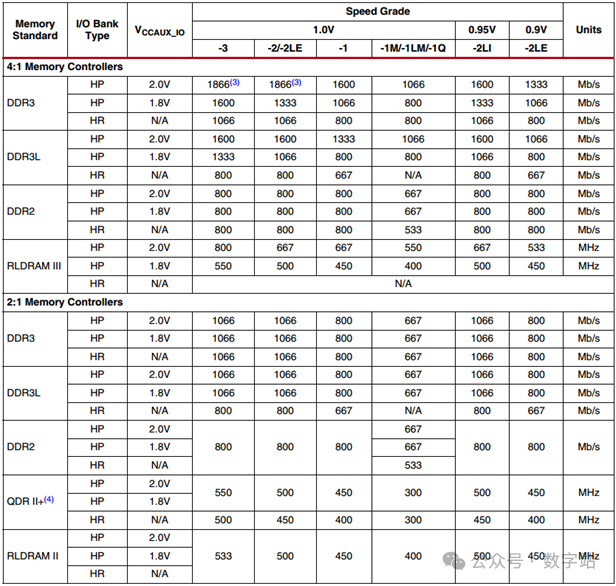

對(duì)于K7的DDR3硬核數(shù)據(jù)收發(fā)速率基本可以達(dá)到1600Mb/s以上,如下圖所示。

圖6 K7內(nèi)存接口IP的最大物理接口速率

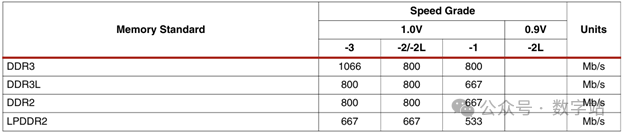

下圖是A7的DDR控制器的數(shù)據(jù)收發(fā)速率,一般在800Mb/s左右,是K7速率的一半。

圖7 A7內(nèi)存接口IP的最大物理接口速率

由上述可知,除了DDR硬核控制器之外,HP和HR bank的ISERDES和OSERDES即使能夠?qū)崿F(xiàn)單沿并行數(shù)據(jù)與雙沿串行數(shù)據(jù)的轉(zhuǎn)換,但是數(shù)據(jù)傳輸?shù)乃俾室琅f不是很高。如果要應(yīng)對(duì)高速ADC和PCIE這些接口,顯然速率不夠。

03Gigabyte Transceiver

基于上述原因,xilinx就推出了Gigabyte Transceiver。Xilinx 7系列的FPGA支持的GT一共有四種,分別為:GTP,GTX,GTH,GTZ,區(qū)別在于線速率不同。

其中GTP被用于A7系列,GTX通常被用于K7系列,GTH一般被用于V7系列,GTZ被用于少數(shù)V7系列。

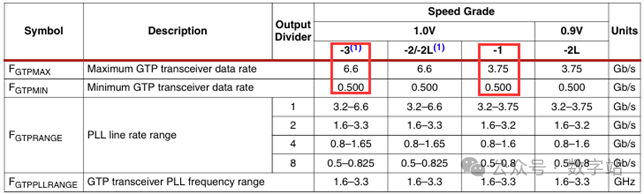

GTP線速率可以達(dá)到6.6Gb/s,具體速率與芯片的速度等級(jí)有關(guān),如下表所示,速度等級(jí)為-2的芯片線速率可以達(dá)到6.6Gb/s。

圖8 GTP速率

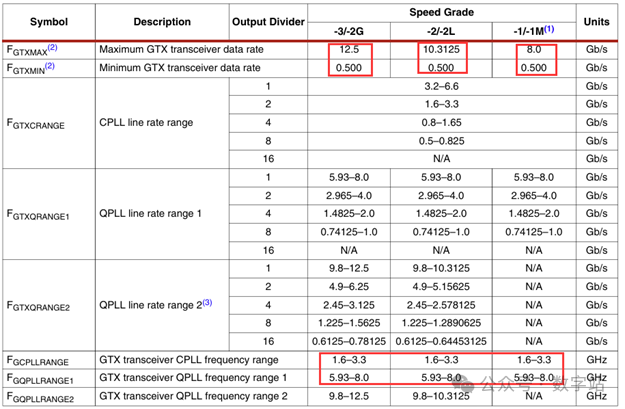

GTX線速率可以達(dá)到12.5Gb/s,我用的芯片型號(hào)為xc7z030ffg676-2,因此速率可以達(dá)到10.3125Gb/s,可以實(shí)現(xiàn)萬兆網(wǎng)傳輸。從下圖知最大速率與QPLL和CPLL也有關(guān),當(dāng)線速率大于5.93GHz時(shí)使用QPLL。

圖9 GTX速率

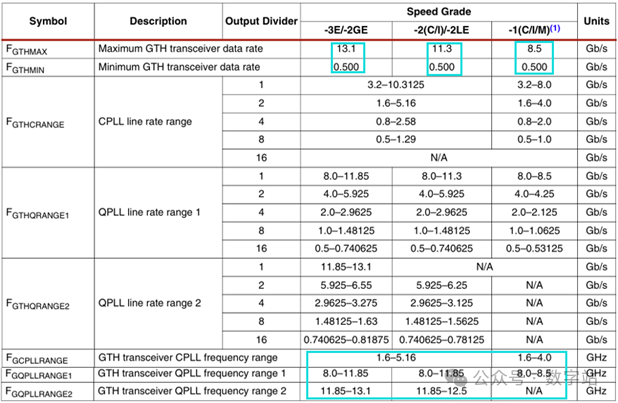

GTH線速率可以達(dá)到13.1Gb/s,如下圖所示,GTZ線速率可以達(dá)到28.05Gb/s,暫時(shí)沒有找到其數(shù)據(jù)手冊(cè)。

圖10 GTH速率

關(guān)于GT收發(fā)器出現(xiàn)背景以及HP、HR bank、高速收發(fā)器的速率就講解到這里吧。

來源:本文轉(zhuǎn)載自數(shù)字站公眾號(hào)

-

FPGA

+關(guān)注

關(guān)注

1626文章

21665瀏覽量

601808 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3393瀏覽量

105860 -

接口

+關(guān)注

關(guān)注

33文章

8496瀏覽量

150834 -

adc

+關(guān)注

關(guān)注

98文章

6430瀏覽量

544078

原文標(biāo)題:FPGA高速收發(fā)器的來源

文章出處:【微信號(hào):FPGA研究院,微信公眾號(hào):FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA設(shè)計(jì)之GTP、GTX、GTH以及GTZ四種串行高速收發(fā)器

#fpga 利用IBERT IP核實(shí)現(xiàn)GTX收發(fā)器硬件誤碼率測(cè)試實(shí)例

求助FPGA高速串行收發(fā)器,輸出12.5Gbps的信號(hào)要用什么電平 ...

關(guān)于FPGA如何連接CAN收發(fā)器?

FPGA高速收發(fā)器設(shè)計(jì)要遵循哪些原則?

FPGA高速收發(fā)器的設(shè)計(jì)原則有哪些?

FPGA高速收發(fā)器設(shè)計(jì)原則

Xilinx推出UltraScale FPGA收發(fā)器設(shè)計(jì)

40-nm收發(fā)器FPGA和ASIC系列的特點(diǎn)

高速ADC與高速串行收發(fā)器

基于XilinxVirtex?-6FPGA 11.18 Gbps收發(fā)器的高速互操作性

Logos系列FPGA高速串行收發(fā)器(HSST)用戶指南

FPGA高速收發(fā)器的來源

FPGA高速收發(fā)器的來源

評(píng)論