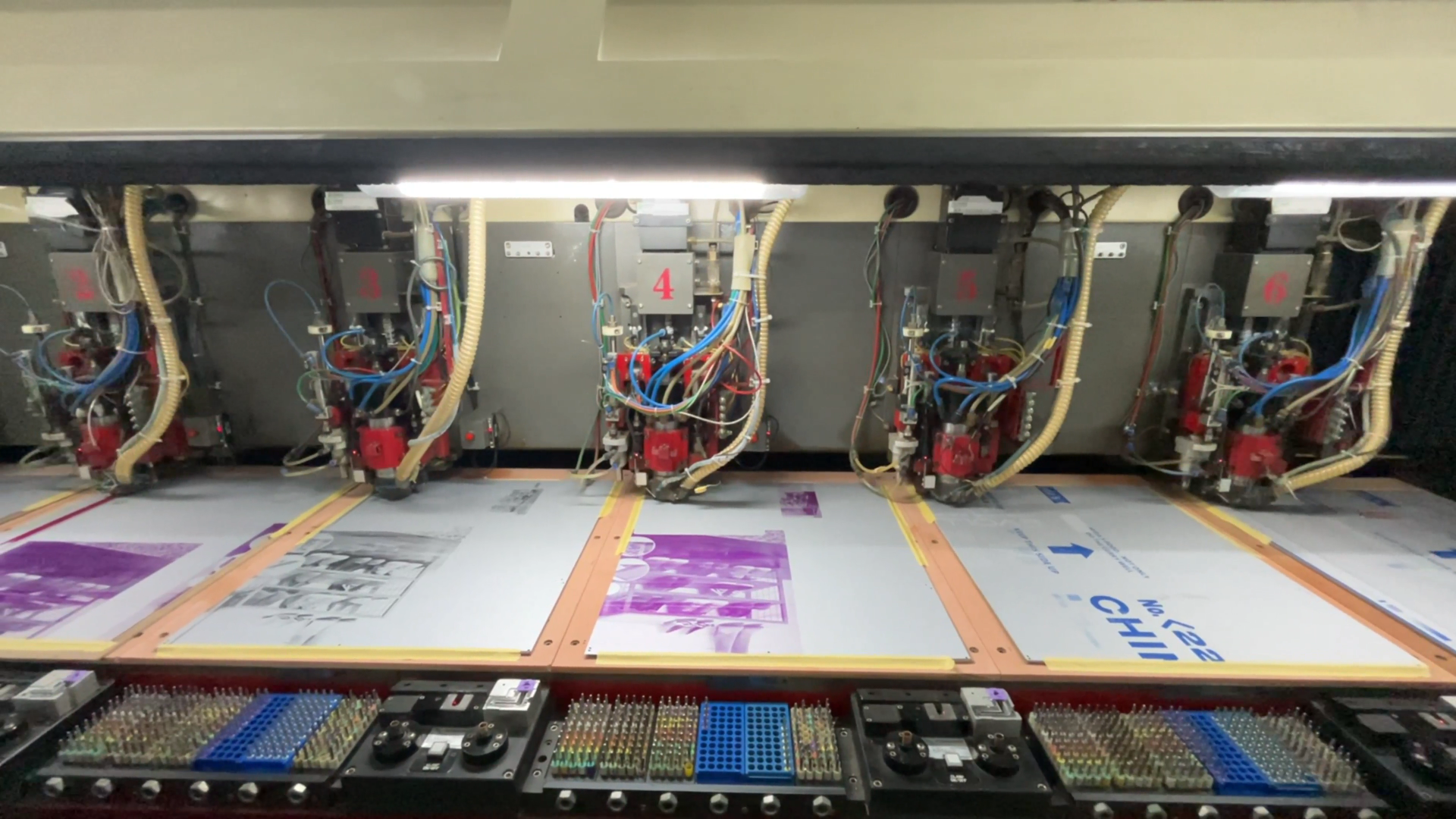

作為現(xiàn)代傳感器重要的制造技術(shù),MEMS工藝深刻地影響了現(xiàn)今傳感器產(chǎn)業(yè)的發(fā)展。可以說,MEMS的工藝技術(shù)都是從集成電路(IC)行業(yè)借鑒而來的,特別在MEMS剛興起時(shí),傳統(tǒng)IC行業(yè)的工藝設(shè)備和技術(shù)為MEMS制造提供了巨大的基礎(chǔ)設(shè)施。比如,MEMS中使用的光刻設(shè)備,可能是為IC制造而設(shè)計(jì)的前幾代設(shè)備,但設(shè)備的性能足以滿足MEMS的要求,其價(jià)格卻大幅降低。

MEMS芯片制造采用光刻、干法刻蝕、濕法刻蝕、薄膜沉積、氧化、擴(kuò)散、注入、濺射、蒸鍍、鍵合等基本工藝步驟來制造復(fù)雜三維結(jié)構(gòu)的微加工技術(shù)。隨著多年發(fā)展,MEMS領(lǐng)域也出現(xiàn)了一些專門的工藝,例如各向異性濕法蝕刻(anisotropic wet etching)、晶圓鍵合(wafer bonding)、深反應(yīng)離子蝕刻(deep reactive ion etching)等,但其應(yīng)用仍然僅限于 MEMS,目前來看并沒反過來應(yīng)用于IC行業(yè)。

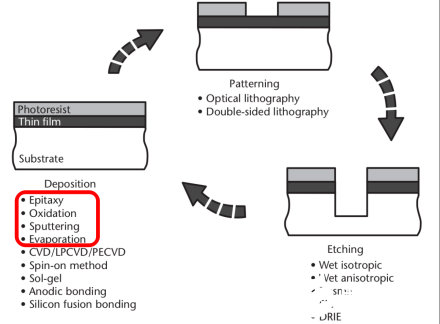

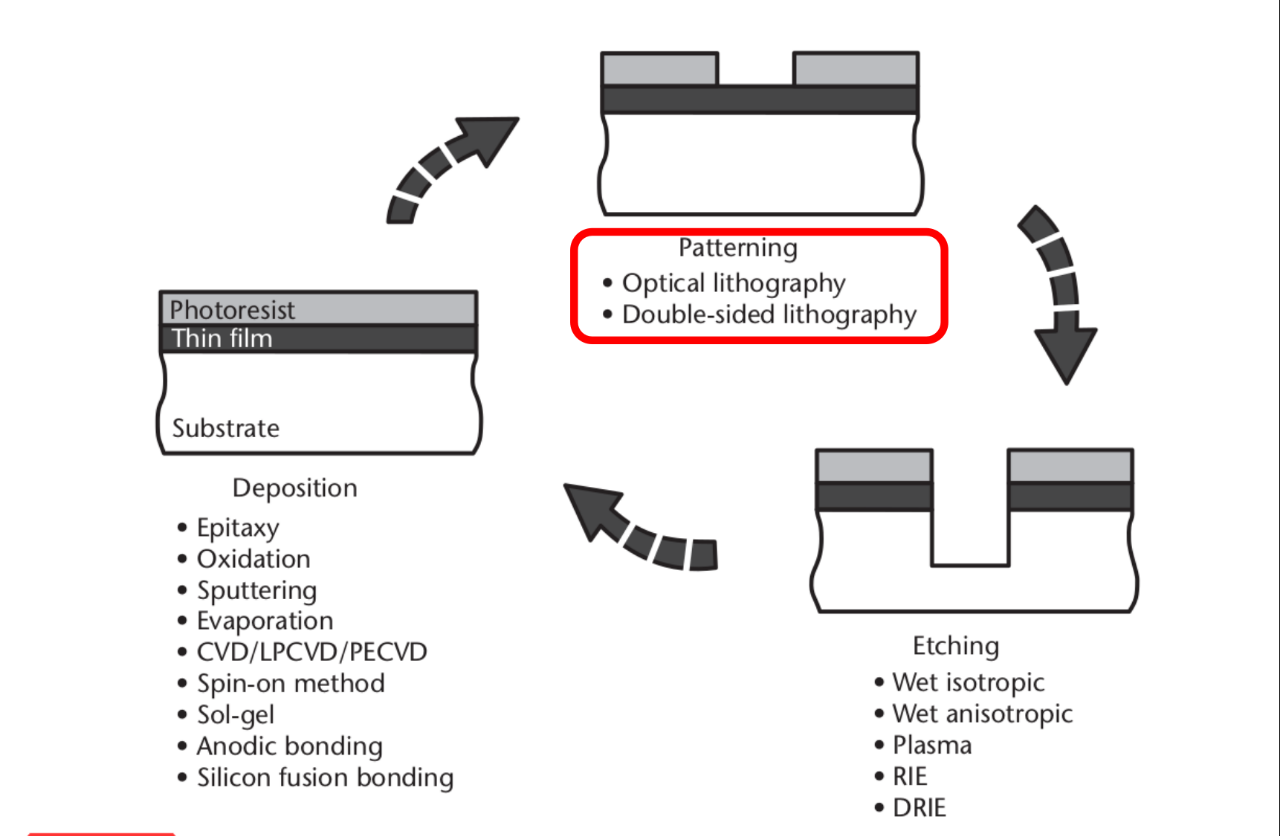

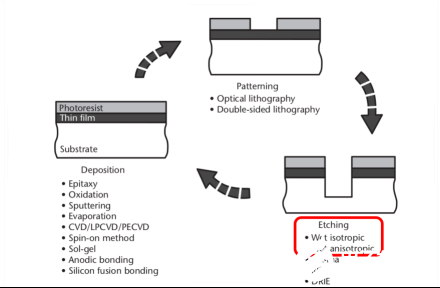

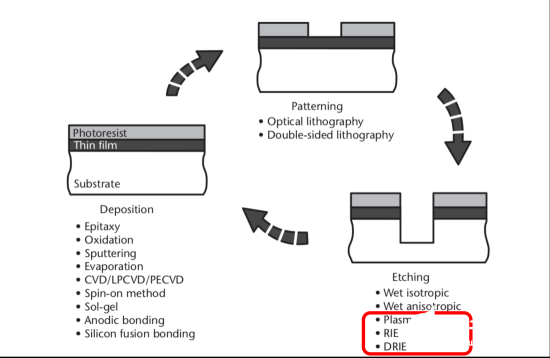

一般來說,MEMS芯片制造的基本工藝包括三個(gè)關(guān)鍵步驟:沉積(Deposition)、圖形化轉(zhuǎn)移(Patterning)、蝕刻(Etching),整個(gè)過程即:①晶圓/襯底涂抹光刻膠,然后②通過對(duì)光刻膠曝光,去除非圖形化部分的光刻膠,然后③用光刻膠作為掩模來蝕刻下方的材料。整個(gè)過程重復(fù)進(jìn)行,直到完成微觀結(jié)構(gòu)。

圖- MEMS制造的基本工藝流程

圖- MEMS制造的基本工藝流程

下文全面介紹MEMS芯片中制造的常用基本工藝,以及討論各種工藝對(duì)MEMS芯片及傳感器產(chǎn)品的影響,部分目錄如下:

↓↓↓向下滑動(dòng),查看更多↓↓↓

一、沉積1、外延(Epitaxy)2、氧化(Oxidating)3、濺射(Sputtering)4、蒸發(fā)(Evaporation)5、化學(xué)氣相沉積(Chemical vapor deposition)6、多晶硅(Poly silicon)的沉積7、二氧化硅(Silicon Dioxide)的沉積8、氮化硅(Silicon Nitrides)的沉積9、旋涂工藝(Spin-On)二、光刻1、掩膜版(Mask)與光刻膠(Photoresist)2、光學(xué)曝光(Exposure)3、光刻膠厚度對(duì)光刻的影響4、地形高度變化對(duì)光刻的影響5、視場(field of view)對(duì)光刻的影響6、需要雙面光刻的情況三、刻蝕1、濕法刻蝕(1)濕法與干法刻蝕(2)各向同性與各向異性(3)刻蝕的三維結(jié)構(gòu)(4)小結(jié)2、干法刻蝕(1)電化學(xué)蝕刻(2)等離子蝕刻與反應(yīng)離子刻蝕(3)深度反應(yīng)離子蝕刻(博世工藝)

來源:芯生活SEMI Businessweek

一、沉積 外延(Epitaxy)、氧化(Oxidating)、濺射(Sputtering)、蒸發(fā)(Evaporation)等屬于沉積(Deposition)類別的基本工藝,也是用于沉積均勻的半導(dǎo)體、金屬、絕緣體和聚合物層的常用技術(shù)。1、外延(Epitaxy)

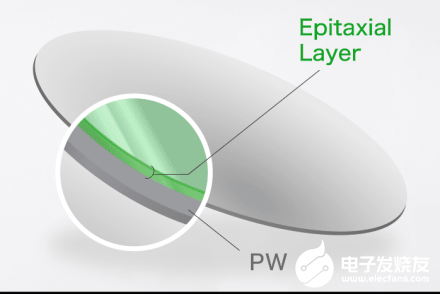

外延是一種在硅晶圓上生長晶體硅(crystalline silicon)層的沉積方法,但具有不同的摻雜劑類型和濃度。外延層的厚度通常為 1 至 20 μm。它表現(xiàn)出與下面的晶體基板相同的晶體取向。當(dāng)然,如果是在非晶材料(例如二氧化硅層)上生長時(shí),它是多晶的。

圖-硅襯底上的外延層

外延可以是在氣相化學(xué)沉積反應(yīng)器中通過含硅源氣體在高溫(>800℃)下的離解或氫還原發(fā)生的。常見的含硅源氣體有硅烷(SiH4)、二氯硅烷(SiH 2Cl2)或四氯化硅(SiCl4)。生長速率在 0.2 至 4 μm/min 之間,具體取決于源氣體和生長溫度。在生長過程中,同時(shí)摻入雜質(zhì)摻雜劑,如,砷化氫(AsH3)和磷化氫(PH3)用于砷和磷(n型)摻雜;而乙硼烷(B2H6)用于硼(p型)摻雜。

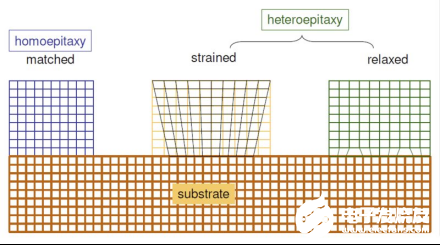

外延可用于在其他類型的晶體基板,例如藍(lán)寶石襯底(Al2O3)上生長晶體硅。該過程稱為異質(zhì)外延,以表明材料的差異 藍(lán)寶石上硅(Silicon-on-sapphire)晶圓在需要絕緣或透明基板的應(yīng)用中非常有效。藍(lán)寶石和硅晶體之間的晶格失配(lattice mismatch)將硅的厚度限制在大約一微米。較厚的硅膜存在高缺陷密度和電子性能下降的問題。

圖-硅襯底上的外延層

外延可以是在氣相化學(xué)沉積反應(yīng)器中通過含硅源氣體在高溫(>800℃)下的離解或氫還原發(fā)生的。常見的含硅源氣體有硅烷(SiH4)、二氯硅烷(SiH 2Cl2)或四氯化硅(SiCl4)。生長速率在 0.2 至 4 μm/min 之間,具體取決于源氣體和生長溫度。在生長過程中,同時(shí)摻入雜質(zhì)摻雜劑,如,砷化氫(AsH3)和磷化氫(PH3)用于砷和磷(n型)摻雜;而乙硼烷(B2H6)用于硼(p型)摻雜。

外延可用于在其他類型的晶體基板,例如藍(lán)寶石襯底(Al2O3)上生長晶體硅。該過程稱為異質(zhì)外延,以表明材料的差異 藍(lán)寶石上硅(Silicon-on-sapphire)晶圓在需要絕緣或透明基板的應(yīng)用中非常有效。藍(lán)寶石和硅晶體之間的晶格失配(lattice mismatch)將硅的厚度限制在大約一微米。較厚的硅膜存在高缺陷密度和電子性能下降的問題。

圖-外延層晶格失配

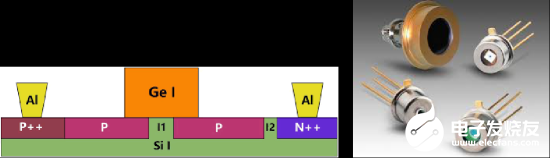

當(dāng)然也有在硅襯底上生長鍺(Germanium)薄膜外延技術(shù),這種基于硅基鍺的工藝,通常用于光電子探測器件。

圖-外延層晶格失配

當(dāng)然也有在硅襯底上生長鍺(Germanium)薄膜外延技術(shù),這種基于硅基鍺的工藝,通常用于光電子探測器件。

圖-鍺外延與APD光電子探測器件

2、氧化(Oxidating)

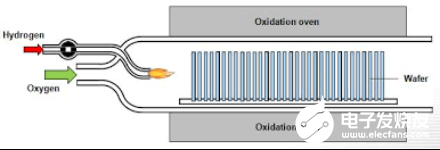

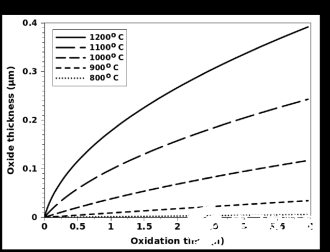

高品質(zhì)非晶態(tài)二氧化硅是通過在干燥氧氣或高溫蒸汽(850℃ - 1150℃)下氧化硅而獲得的。最終氧化物厚度隨溫度、氧化環(huán)境和時(shí)間變化情況如下圖所示。

圖-鍺外延與APD光電子探測器件

2、氧化(Oxidating)

高品質(zhì)非晶態(tài)二氧化硅是通過在干燥氧氣或高溫蒸汽(850℃ - 1150℃)下氧化硅而獲得的。最終氧化物厚度隨溫度、氧化環(huán)境和時(shí)間變化情況如下圖所示。

圖-熱氧爐

圖-熱氧爐

圖-熱氧厚度與溫度、時(shí)間曲線

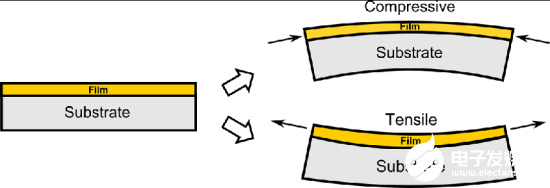

硅的熱氧化在二氧化硅薄膜層中產(chǎn)生壓應(yīng)力。產(chǎn)生應(yīng)力的原因有兩個(gè):二氧化硅分子比硅原子占據(jù)更大的體積,以及硅和二氧化硅的熱膨脹系數(shù)不匹配。應(yīng)力取決于二氧化硅層的總厚度,可以達(dá)到數(shù)百M(fèi)Pa。結(jié)果,熱生長的氧化膜導(dǎo)致下面的襯底彎曲/翹曲(bowing)。

此外,由熱生長氧化硅制成的獨(dú)立式薄膜和懸臂梁(一種MEMS結(jié)構(gòu))由于薄膜厚度上的應(yīng)力變化而容易變形或卷曲。

圖-熱氧厚度與溫度、時(shí)間曲線

硅的熱氧化在二氧化硅薄膜層中產(chǎn)生壓應(yīng)力。產(chǎn)生應(yīng)力的原因有兩個(gè):二氧化硅分子比硅原子占據(jù)更大的體積,以及硅和二氧化硅的熱膨脹系數(shù)不匹配。應(yīng)力取決于二氧化硅層的總厚度,可以達(dá)到數(shù)百M(fèi)Pa。結(jié)果,熱生長的氧化膜導(dǎo)致下面的襯底彎曲/翹曲(bowing)。

此外,由熱生長氧化硅制成的獨(dú)立式薄膜和懸臂梁(一種MEMS結(jié)構(gòu))由于薄膜厚度上的應(yīng)力變化而容易變形或卷曲。

圖-晶圓翹曲

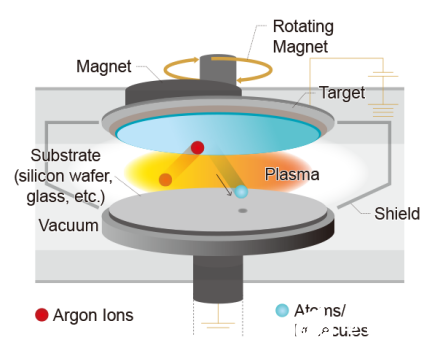

3、濺射(Sputtering)

在濺射沉積中,由待沉積材料制成的靶材在壓力為 0.1–10 Pa 的真空室中受到惰性氣體離子流(通常是氬氣Argon)的物理轟擊。來自靶材的原子或分子被噴射并沉積到晶圓上。濺射機(jī)臺(tái)其離子激發(fā)機(jī)制各不相同,但涉及磁場、電場、射頻等物理原理,都要產(chǎn)生一些高能或高速的粒子。典型的沉積速率為 0.1–0.3 μm/min,在某些濺射工具中鋁的沉積速率可高達(dá) 1 μm/min。

圖-晶圓翹曲

3、濺射(Sputtering)

在濺射沉積中,由待沉積材料制成的靶材在壓力為 0.1–10 Pa 的真空室中受到惰性氣體離子流(通常是氬氣Argon)的物理轟擊。來自靶材的原子或分子被噴射并沉積到晶圓上。濺射機(jī)臺(tái)其離子激發(fā)機(jī)制各不相同,但涉及磁場、電場、射頻等物理原理,都要產(chǎn)生一些高能或高速的粒子。典型的沉積速率為 0.1–0.3 μm/min,在某些濺射工具中鋁的沉積速率可高達(dá) 1 μm/min。

圖-濺射(Sputtering)

幾乎任何無機(jī)材料都可以濺射。濺射是MEMS領(lǐng)域常用的方法,用于在低溫(<150℃)下沉積金屬薄膜,例如鋁、鈦、鉻、鉑、鈀、鎢、和 合金、非晶硅、絕緣體包括玻璃和壓電陶瓷(例如 PZT 和 ZnO等)。在稱為反應(yīng)濺射(reactive sputtering)的工藝中,在金屬濺射期間添加諸如氮?dú)饣蜓鯕獾姆磻?yīng)氣體以形成諸如氮化鈦或二氧化鈦的化合物。

濺射工藝的方向隨機(jī)性,只要靶材尺寸大于晶圓,就會(huì)產(chǎn)生良好的覆蓋率(薄膜的均勻性),盡管拐角附近會(huì)發(fā)生一些減薄。沉積的薄膜具有非常細(xì)小的顆粒結(jié)構(gòu),并且通常處于有應(yīng)力的狀態(tài)之下。

圖-濺射(Sputtering)

幾乎任何無機(jī)材料都可以濺射。濺射是MEMS領(lǐng)域常用的方法,用于在低溫(<150℃)下沉積金屬薄膜,例如鋁、鈦、鉻、鉑、鈀、鎢、和 合金、非晶硅、絕緣體包括玻璃和壓電陶瓷(例如 PZT 和 ZnO等)。在稱為反應(yīng)濺射(reactive sputtering)的工藝中,在金屬濺射期間添加諸如氮?dú)饣蜓鯕獾姆磻?yīng)氣體以形成諸如氮化鈦或二氧化鈦的化合物。

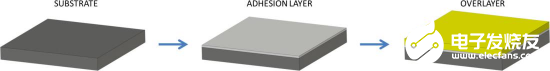

濺射工藝的方向隨機(jī)性,只要靶材尺寸大于晶圓,就會(huì)產(chǎn)生良好的覆蓋率(薄膜的均勻性),盡管拐角附近會(huì)發(fā)生一些減薄。沉積的薄膜具有非常細(xì)小的顆粒結(jié)構(gòu),并且通常處于有應(yīng)力的狀態(tài)之下。沉積過程中應(yīng)力水平隨濺射功率和腔室壓力而變化,在較低功率和較高壓力下出現(xiàn)拉伸應(yīng)力(tensile stress),在較高功率和較低壓力下出現(xiàn)壓縮應(yīng)力(compressive stress)。零應(yīng)力沉積的理想點(diǎn)很難難控制。在沉積過程中加熱基底有時(shí)可以用于減少薄膜應(yīng)力。 許多金屬,特別是金、銀和鉑等惰性金屬,不能很好地粘附到硅、二氧化硅或氮化硅上,在沉積后或在后續(xù)處理過程中會(huì)立即剝落。一層薄薄的(5 至 20 納米)粘合層(adhesion layer)與底層材料及其上方的金屬粘合,使惰性金屬能夠粘附。最常見的粘附層是 Cr、Ti 和 Ti/W 合金。惰性金屬必須在真空的情況下沉積在粘合層上,因?yàn)榭諝庵械难鯕鈺?huì)立即氧化粘合層,使其粘合效果失效。

圖-粘合層

4、蒸發(fā)(Evaporation)

蒸發(fā)涉及將源材料加熱至高溫,產(chǎn)生蒸氣并在基材上凝結(jié)形成薄膜。幾乎任何元素(例如 Al、Si、Ti、Au),包括許多高熔點(diǎn)(難熔)金屬和化合物(例如 Cr、Mo、Ta、Pd、Pt、Ni/Cr、Al 2 O 3 ),可以通過蒸發(fā)而沉積。

蒸發(fā)在背景壓力通常低于10^-4 Pa的真空室中進(jìn)行。源材料加熱可以通過使電流流過裝有所需材料的鎢絲、鎢條或鎢舟來實(shí)現(xiàn)。或者,可以通過在源材料上掃描高壓(10kV)電子束(e-beam)來完成加熱。

在這種情況下,材料的載體通常由鎢、石墨、氧化鋁或銅等熱的優(yōu)良導(dǎo)體制成。相比之下,電子束蒸發(fā)可以提供質(zhì)量更好的薄膜和稍高的沉積速率(5-100 nm/min),但沉積系統(tǒng)更復(fù)雜。此外,在這個(gè)過程中,如果某些輻射能量穿透硅基板表面,可能會(huì)損壞晶體并降低電子電路的特性。

圖-粘合層

4、蒸發(fā)(Evaporation)

蒸發(fā)涉及將源材料加熱至高溫,產(chǎn)生蒸氣并在基材上凝結(jié)形成薄膜。幾乎任何元素(例如 Al、Si、Ti、Au),包括許多高熔點(diǎn)(難熔)金屬和化合物(例如 Cr、Mo、Ta、Pd、Pt、Ni/Cr、Al 2 O 3 ),可以通過蒸發(fā)而沉積。

蒸發(fā)在背景壓力通常低于10^-4 Pa的真空室中進(jìn)行。源材料加熱可以通過使電流流過裝有所需材料的鎢絲、鎢條或鎢舟來實(shí)現(xiàn)。或者,可以通過在源材料上掃描高壓(10kV)電子束(e-beam)來完成加熱。

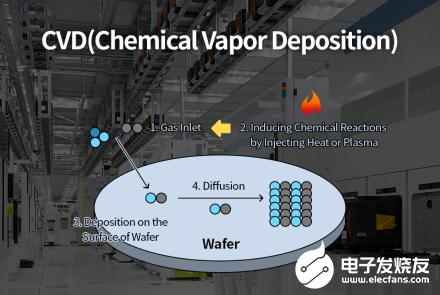

在這種情況下,材料的載體通常由鎢、石墨、氧化鋁或銅等熱的優(yōu)良導(dǎo)體制成。相比之下,電子束蒸發(fā)可以提供質(zhì)量更好的薄膜和稍高的沉積速率(5-100 nm/min),但沉積系統(tǒng)更復(fù)雜。此外,在這個(gè)過程中,如果某些輻射能量穿透硅基板表面,可能會(huì)損壞晶體并降低電子電路的特性。蒸發(fā)是一種來自相對(duì)較小體積來源的定向沉積過程。這導(dǎo)致大部分材料顆粒以特定角度沉積到基板上,導(dǎo)致臺(tái)階覆蓋不良,并有角落和側(cè)壁暴露的現(xiàn)象。如果需要薄膜連續(xù)性(例如,當(dāng)金屬是電互連時(shí)),這通常是不期望的效果。在沉積過程中旋轉(zhuǎn)基板以不同角度面對(duì)源會(huì)減少這種影響。 通過蒸發(fā)沉積的薄膜往往會(huì)表現(xiàn)出拉伸應(yīng)力,并且隨著材料熔點(diǎn)的升高而增加。例如,蒸發(fā)的鈮和鉑薄膜可能具有超過 1 GPa 的拉伸應(yīng)力,足以導(dǎo)致晶圓卷曲甚至剝離。此外,與濺射一樣,許多金屬必須使用粘合層。5、化學(xué)氣相沉積(Chemical vapor deposition) 化學(xué)氣相沉積(CVD)的工作原理是在受控氣氛中引發(fā)表面化學(xué)反應(yīng),從而導(dǎo)致反應(yīng)物質(zhì)沉積在加熱的基材上。與上一節(jié)的濺射相反,CVD是一種高溫工藝,通常在300°C以上進(jìn)行。在IC行業(yè)對(duì)用于多層電互連的高質(zhì)量、薄電介質(zhì)和金屬薄膜的需求的推動(dòng)下,CVD技術(shù)發(fā)展已大幅增長。 通過CVD沉積的常見薄膜包括多晶硅、硅氧化物和氮化物、鎢、鈦、鉭等金屬及其氮化物,以及最近的銅和低介電常數(shù)絕緣體(εr<3)。后兩者正在成為IC行業(yè)中超高速電氣互連的主力材料。而在MEMS領(lǐng)域,多晶硅、氧化硅和氮化物的CVD沉積是最常見的。

圖-CVD反應(yīng)

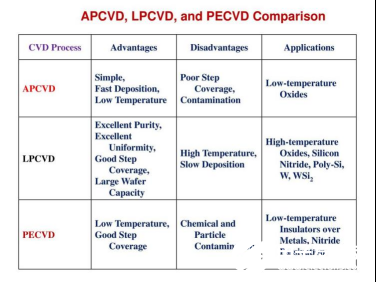

化學(xué)氣相沉積工藝分為大氣壓CVD(稱為APCVD,Atmospheric-pressure CVD)、低壓CVD(LPCVD,Low-pressure CVD)或等離子體增強(qiáng)CVD(PECVD,Plasma-enhanced CVD),其中還包括高密度等離子體CVD(HDP-CVD,High-density plasma CVD)。

圖-CVD反應(yīng)

化學(xué)氣相沉積工藝分為大氣壓CVD(稱為APCVD,Atmospheric-pressure CVD)、低壓CVD(LPCVD,Low-pressure CVD)或等離子體增強(qiáng)CVD(PECVD,Plasma-enhanced CVD),其中還包括高密度等離子體CVD(HDP-CVD,High-density plasma CVD)。

圖-CVD基本類型APCVD LPCVD PECVD

APCVD和LPCVD工藝需要在相當(dāng)高的溫度(400°C–800°C)進(jìn)行。而在PECVD和HDP-CVD中,在室溫下等離子體沉積氮化硅是可行的,但襯底溫度通常也要接近300°C。

沉積參數(shù)對(duì)薄膜特性的影響是顯著的,特別是對(duì)于氧化硅和氮化硅等薄膜。這些參數(shù)包括了:襯底溫度、氣流、壓力、及是否存在摻雜劑等,這些是所有類型CVD的重要變量。此外,功率和等離子體激發(fā)射頻頻率對(duì)于PECVD也很重要。

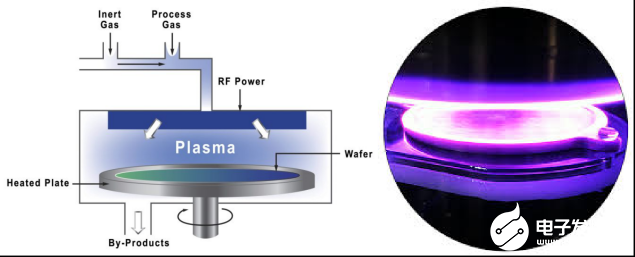

特別地,對(duì)于PECVD,需要在高頻電磁場中進(jìn)行,在這種環(huán)境中激發(fā)的高能電子與氣體分子碰撞,形成離子和反應(yīng)性中性物質(zhì)。電子、離子和中性物質(zhì)的混合物稱為等離子體,構(gòu)成了不同于固體、液體或氣體的物質(zhì)相。等離子體相操作增加了可以參與化學(xué)反應(yīng)(無論是沉積還是蝕刻)的離子和中性物質(zhì)的密度,因此可以加快反應(yīng)速率。

圖-CVD基本類型APCVD LPCVD PECVD

APCVD和LPCVD工藝需要在相當(dāng)高的溫度(400°C–800°C)進(jìn)行。而在PECVD和HDP-CVD中,在室溫下等離子體沉積氮化硅是可行的,但襯底溫度通常也要接近300°C。

沉積參數(shù)對(duì)薄膜特性的影響是顯著的,特別是對(duì)于氧化硅和氮化硅等薄膜。這些參數(shù)包括了:襯底溫度、氣流、壓力、及是否存在摻雜劑等,這些是所有類型CVD的重要變量。此外,功率和等離子體激發(fā)射頻頻率對(duì)于PECVD也很重要。

特別地,對(duì)于PECVD,需要在高頻電磁場中進(jìn)行,在這種環(huán)境中激發(fā)的高能電子與氣體分子碰撞,形成離子和反應(yīng)性中性物質(zhì)。電子、離子和中性物質(zhì)的混合物稱為等離子體,構(gòu)成了不同于固體、液體或氣體的物質(zhì)相。等離子體相操作增加了可以參與化學(xué)反應(yīng)(無論是沉積還是蝕刻)的離子和中性物質(zhì)的密度,因此可以加快反應(yīng)速率。

圖-PECVD反應(yīng)環(huán)境

6、多晶硅(Poly silicon)的沉積

化學(xué)氣相沉積工藝允許在硅基板上沉積多晶硅薄膜。薄膜厚度可以在幾十納米到幾微米之間。甚至,具有多層的多晶硅薄膜的結(jié)構(gòu)也是可行的。多晶硅是一種具有體硅特性的材料,易于沉積,使其成為表面微加工領(lǐng)域極具吸引力的材料。

圖-PECVD反應(yīng)環(huán)境

6、多晶硅(Poly silicon)的沉積

化學(xué)氣相沉積工藝允許在硅基板上沉積多晶硅薄膜。薄膜厚度可以在幾十納米到幾微米之間。甚至,具有多層的多晶硅薄膜的結(jié)構(gòu)也是可行的。多晶硅是一種具有體硅特性的材料,易于沉積,使其成為表面微加工領(lǐng)域極具吸引力的材料。

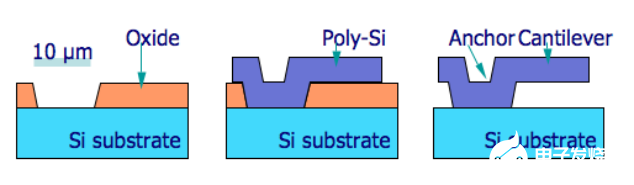

圖-MEMS中的多晶硅

多晶硅是通過在LPCVD反應(yīng)器中將硅烷(SiH4)熱解成硅和氫而沉積的。低溫PECVD反應(yīng)器中的硅烷沉積也是可能的,但會(huì)產(chǎn)生非晶硅(amorphous silicon)。LPCVD中的沉積溫度通常在550°C至700°C之間,溫度會(huì)影響薄膜的顆粒結(jié)構(gòu),如果低于約600°C,薄膜完全非晶態(tài),在約630°C以上時(shí),它呈現(xiàn)出晶粒結(jié)構(gòu)。溫度、硅烷氣體的壓力和流速也影響沉積速率。

圖-MEMS中的多晶硅

多晶硅是通過在LPCVD反應(yīng)器中將硅烷(SiH4)熱解成硅和氫而沉積的。低溫PECVD反應(yīng)器中的硅烷沉積也是可能的,但會(huì)產(chǎn)生非晶硅(amorphous silicon)。LPCVD中的沉積溫度通常在550°C至700°C之間,溫度會(huì)影響薄膜的顆粒結(jié)構(gòu),如果低于約600°C,薄膜完全非晶態(tài),在約630°C以上時(shí),它呈現(xiàn)出晶粒結(jié)構(gòu)。溫度、硅烷氣體的壓力和流速也影響沉積速率。

圖-LPCVD沉積多晶硅

一般來說,LPCVD多晶硅薄膜與晶圓上的底層形貌吻合良好,表現(xiàn)出良好的階梯覆蓋性。在縱橫比(深度與寬度之比)超過10的深溝槽中,側(cè)壁上會(huì)出現(xiàn)一定程度的薄膜變薄,但這并不限制使用多晶硅填充深達(dá)500μm的溝槽。

多晶硅可以在沉積過程中通過引入摻雜劑源氣體進(jìn)行摻雜,稱為原位摻雜,特別是用于n型摻雜的砷或磷,以及用于p型摻雜的乙硼烷。砷和磷大大降低了沉積速率,約為未摻雜多晶硅的三分之一,而乙硼烷則提高了沉積速率。原位摻雜薄膜的電阻率保持在1至10mΩ·cm范圍內(nèi)。

圖-LPCVD沉積多晶硅

一般來說,LPCVD多晶硅薄膜與晶圓上的底層形貌吻合良好,表現(xiàn)出良好的階梯覆蓋性。在縱橫比(深度與寬度之比)超過10的深溝槽中,側(cè)壁上會(huì)出現(xiàn)一定程度的薄膜變薄,但這并不限制使用多晶硅填充深達(dá)500μm的溝槽。

多晶硅可以在沉積過程中通過引入摻雜劑源氣體進(jìn)行摻雜,稱為原位摻雜,特別是用于n型摻雜的砷或磷,以及用于p型摻雜的乙硼烷。砷和磷大大降低了沉積速率,約為未摻雜多晶硅的三分之一,而乙硼烷則提高了沉積速率。原位摻雜薄膜的電阻率保持在1至10mΩ·cm范圍內(nèi)。摻雜的多晶硅薄膜的固有應(yīng)力可能很大(>500MPa),應(yīng)力可能是拉伸應(yīng)力,也可能是壓縮應(yīng)力,具體取決于沉積溫度。此外,薄膜厚度上通常存在應(yīng)力梯度,這會(huì)導(dǎo)致釋放后的微機(jī)械結(jié)構(gòu)卷曲。所以需要在900°C或更高溫度下進(jìn)行退火,通過晶界的結(jié)構(gòu)變化產(chǎn)生應(yīng)力松弛,并將應(yīng)力降低至微機(jī)械結(jié)構(gòu)通常認(rèn)為可接受的水平(<50MPa)和應(yīng)力梯度。 7、二氧化硅(Silicon Dioxide)的沉積 通過在APCVD、LPCVD或PECVD反應(yīng)器中使硅烷和氧氣發(fā)生反應(yīng),在低于500°C的溫度下沉積二氧化硅。由于與熱生長氧化物的工藝(thermally grown oxide,簡稱熱氧)相比溫度較低,因此被稱為低溫氧化物(LTO,low-temperature oxide)。

圖-二氧化硅沉積

沉積過程中可用磷或硼摻雜氧化硅。摻有磷的薄膜通常稱為磷硅酸鹽玻璃(PSG);摻雜有磷和硼的玻璃被稱為硼磷硅酸鹽玻璃(BPSG)。當(dāng)在接近1,000°C的溫度下退火時(shí),PSG和BPSG都會(huì)軟化并流動(dòng),以符合下面的表面形貌并改善階梯覆蓋。LTO薄膜用于鋁上的鈍化涂層,但沉積溫度必須保持在400°C以下,以防止下方金屬降解。

也可以在650°C至750°C溫度下,通過LPCVD對(duì)四乙氧基硅烷(也稱為TEOS)的熱解,沉積二氧化硅。從TEOS源沉積的二氧化硅層表現(xiàn)出優(yōu)異的均勻性和階梯覆蓋性,但高溫工藝使其無法在鋁上使用。

與多晶硅LPCVD的情況一樣,二氧化硅的沉積速率隨著溫度的升高而增加。低壓下典型的LTO沉積速率在400°C時(shí)為25nm/min,在大氣壓和450°C時(shí)升至150nm/min;使用TEOS的沉積速率從650°C時(shí)的5nm/min到750°C時(shí)的50nm/min不等。

沉積的二氧化硅薄膜是無定形的,其結(jié)構(gòu)類似于熔融二氧化硅。在高溫(600°C–1,000°C)下進(jìn)行退火會(huì)導(dǎo)致薄膜中摻入的氫逸出,密度略有增加,但非晶結(jié)構(gòu)沒有變化。這個(gè)過程稱為致密化。

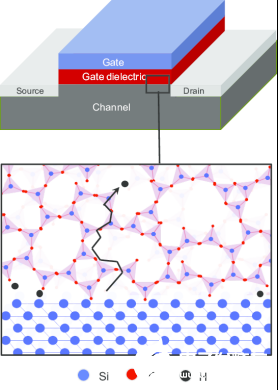

使用CVD方法沉積的二氧化硅作為金屬層之間的介電絕緣體,或作為表面微加工中的犧牲層非常有用,后者使用氫氟酸蝕刻。然而,其電性能不如熱生長二氧化硅。例如,CVD氧化硅的介電強(qiáng)度可以是熱生長二氧化硅(簡稱熱氧)的介電強(qiáng)度的一半,所以CMOS晶體管的柵極絕緣體一般采用后一種工藝類型。一般來說,CVD氧化硅處于壓縮應(yīng)力(100–300MPa)下。

圖-二氧化硅沉積

沉積過程中可用磷或硼摻雜氧化硅。摻有磷的薄膜通常稱為磷硅酸鹽玻璃(PSG);摻雜有磷和硼的玻璃被稱為硼磷硅酸鹽玻璃(BPSG)。當(dāng)在接近1,000°C的溫度下退火時(shí),PSG和BPSG都會(huì)軟化并流動(dòng),以符合下面的表面形貌并改善階梯覆蓋。LTO薄膜用于鋁上的鈍化涂層,但沉積溫度必須保持在400°C以下,以防止下方金屬降解。

也可以在650°C至750°C溫度下,通過LPCVD對(duì)四乙氧基硅烷(也稱為TEOS)的熱解,沉積二氧化硅。從TEOS源沉積的二氧化硅層表現(xiàn)出優(yōu)異的均勻性和階梯覆蓋性,但高溫工藝使其無法在鋁上使用。

與多晶硅LPCVD的情況一樣,二氧化硅的沉積速率隨著溫度的升高而增加。低壓下典型的LTO沉積速率在400°C時(shí)為25nm/min,在大氣壓和450°C時(shí)升至150nm/min;使用TEOS的沉積速率從650°C時(shí)的5nm/min到750°C時(shí)的50nm/min不等。

沉積的二氧化硅薄膜是無定形的,其結(jié)構(gòu)類似于熔融二氧化硅。在高溫(600°C–1,000°C)下進(jìn)行退火會(huì)導(dǎo)致薄膜中摻入的氫逸出,密度略有增加,但非晶結(jié)構(gòu)沒有變化。這個(gè)過程稱為致密化。

使用CVD方法沉積的二氧化硅作為金屬層之間的介電絕緣體,或作為表面微加工中的犧牲層非常有用,后者使用氫氟酸蝕刻。然而,其電性能不如熱生長二氧化硅。例如,CVD氧化硅的介電強(qiáng)度可以是熱生長二氧化硅(簡稱熱氧)的介電強(qiáng)度的一半,所以CMOS晶體管的柵極絕緣體一般采用后一種工藝類型。一般來說,CVD氧化硅處于壓縮應(yīng)力(100–300MPa)下。

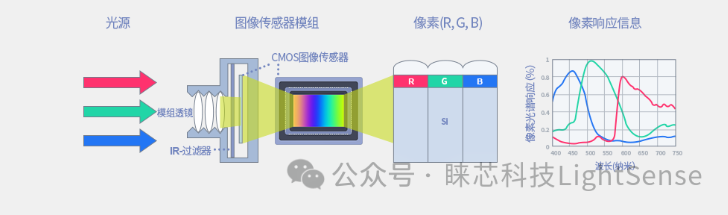

圖-CMOS晶體管的柵極中的二氧化硅

8、氮化硅(Silicon Nitrides)的沉積

氮化硅在半導(dǎo)體工業(yè)中常用于電子器件的鈍化,因?yàn)樗梢孕纬蓸O好的保護(hù)屏障,防止水和鈉離子的擴(kuò)散。在MEMS微機(jī)械加工中,LPCVD氮化硅薄膜可有效用作在堿性溶液(例如氫氧化鉀)中選擇性蝕刻硅的掩模。氮化硅也已被用作結(jié)構(gòu)材料。

圖-CMOS晶體管的柵極中的二氧化硅

8、氮化硅(Silicon Nitrides)的沉積

氮化硅在半導(dǎo)體工業(yè)中常用于電子器件的鈍化,因?yàn)樗梢孕纬蓸O好的保護(hù)屏障,防止水和鈉離子的擴(kuò)散。在MEMS微機(jī)械加工中,LPCVD氮化硅薄膜可有效用作在堿性溶液(例如氫氧化鉀)中選擇性蝕刻硅的掩模。氮化硅也已被用作結(jié)構(gòu)材料。

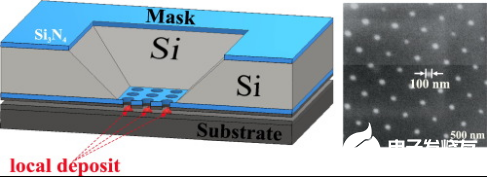

圖-氮化硅作為刻蝕掩模

氮化硅(Si3N4)通過硅烷(SiH4)和氨(NH3)反應(yīng)在大氣壓下沉積,或者通過二氯硅烷(SiCl2H2)和氨反應(yīng)在低壓下沉積。沉積溫度都在700°C至900°C之間。且都會(huì)產(chǎn)生副產(chǎn)品氫,其中一些會(huì)融入沉積薄膜中。APCVD和LPCVD氮化硅薄膜通常表現(xiàn)出接近1,000MPa的大拉伸應(yīng)力。然而,如果LPCVD氮化硅在800°C–850°C溫度下沉積,并且由于二氯硅烷流速大大增加而富含硅(薄膜中硅過量),則應(yīng)力可低于100MPa,這是大多數(shù)微加工應(yīng)用可接受的水平。

對(duì)于低于400°C的沉積,通過在PECVD室中使硅烷與氨或氮?dú)夥磻?yīng)獲得非化學(xué)計(jì)量氮化硅(SixNy)。氫氣也是該反應(yīng)的副產(chǎn)品,并以較高濃度(20%–25%)融入薄膜中。折射率是氮化硅膜化學(xué)計(jì)量的間接量度。化學(xué)計(jì)量LPCVD氮化硅的折射率為2.01,PECVD薄膜的折射率范圍在1.8到2.5之間。該范圍內(nèi)的高值表示硅過量,而低值通常表示氮過量。

圖-氮化硅作為刻蝕掩模

氮化硅(Si3N4)通過硅烷(SiH4)和氨(NH3)反應(yīng)在大氣壓下沉積,或者通過二氯硅烷(SiCl2H2)和氨反應(yīng)在低壓下沉積。沉積溫度都在700°C至900°C之間。且都會(huì)產(chǎn)生副產(chǎn)品氫,其中一些會(huì)融入沉積薄膜中。APCVD和LPCVD氮化硅薄膜通常表現(xiàn)出接近1,000MPa的大拉伸應(yīng)力。然而,如果LPCVD氮化硅在800°C–850°C溫度下沉積,并且由于二氯硅烷流速大大增加而富含硅(薄膜中硅過量),則應(yīng)力可低于100MPa,這是大多數(shù)微加工應(yīng)用可接受的水平。

對(duì)于低于400°C的沉積,通過在PECVD室中使硅烷與氨或氮?dú)夥磻?yīng)獲得非化學(xué)計(jì)量氮化硅(SixNy)。氫氣也是該反應(yīng)的副產(chǎn)品,并以較高濃度(20%–25%)融入薄膜中。折射率是氮化硅膜化學(xué)計(jì)量的間接量度。化學(xué)計(jì)量LPCVD氮化硅的折射率為2.01,PECVD薄膜的折射率范圍在1.8到2.5之間。該范圍內(nèi)的高值表示硅過量,而低值通常表示氮過量。

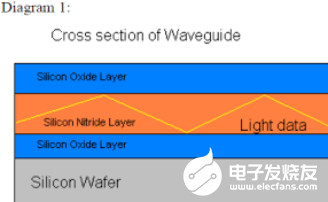

圖-氮化硅用于波導(dǎo)

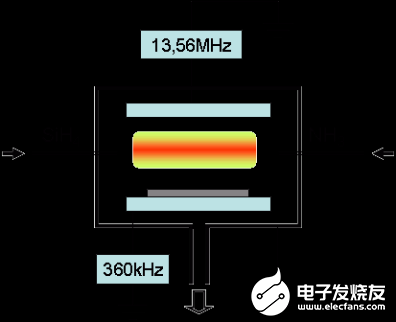

PECVD氮化物的主要優(yōu)點(diǎn)之一是能夠在沉積過程中控制應(yīng)力。在13.56MHz的等離子體激發(fā)頻率下沉積的氮化硅表現(xiàn)出約400MPa的拉升應(yīng)力,而在50kHz的頻率下沉積的膜具有200MPa的壓縮應(yīng)力。通過在沉積期間交替頻率,可以獲得較低應(yīng)力的薄膜。

9、旋涂工藝(Spin-On)

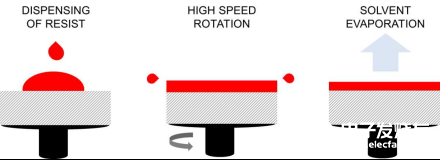

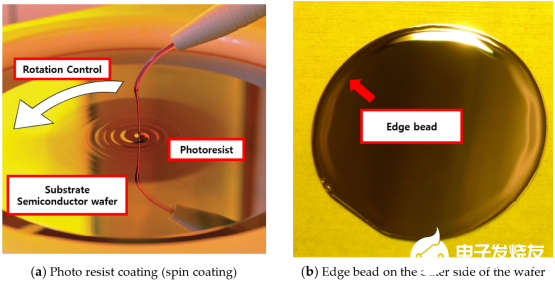

旋涂是一種沉積介電絕緣體和有機(jī)材料層的工藝。與前面的CVD不同,旋涂設(shè)備很簡單,只需要一個(gè)帶有適當(dāng)安全屏障的變速旋轉(zhuǎn)臺(tái),然后用噴嘴將材料以液體溶液的形式滴在晶圓的中心。旋轉(zhuǎn)臺(tái)以500至5,000rpm的速度旋轉(zhuǎn)晶圓30至60秒,將材料鋪展至均勻的厚度。

圖-氮化硅用于波導(dǎo)

PECVD氮化物的主要優(yōu)點(diǎn)之一是能夠在沉積過程中控制應(yīng)力。在13.56MHz的等離子體激發(fā)頻率下沉積的氮化硅表現(xiàn)出約400MPa的拉升應(yīng)力,而在50kHz的頻率下沉積的膜具有200MPa的壓縮應(yīng)力。通過在沉積期間交替頻率,可以獲得較低應(yīng)力的薄膜。

9、旋涂工藝(Spin-On)

旋涂是一種沉積介電絕緣體和有機(jī)材料層的工藝。與前面的CVD不同,旋涂設(shè)備很簡單,只需要一個(gè)帶有適當(dāng)安全屏障的變速旋轉(zhuǎn)臺(tái),然后用噴嘴將材料以液體溶液的形式滴在晶圓的中心。旋轉(zhuǎn)臺(tái)以500至5,000rpm的速度旋轉(zhuǎn)晶圓30至60秒,將材料鋪展至均勻的厚度。

圖-旋涂工藝

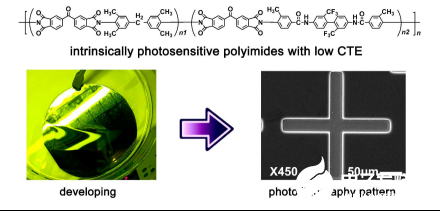

光刻膠和聚酰亞胺(PI)是常見的有機(jī)材料,可以在晶圓上旋涂,厚度通常在0.5至20μm之間,但一些特殊用途的光刻膠(例如基于環(huán)氧樹脂的SU-8)可以超過200μm。有機(jī)聚合物通常懸浮在溶劑溶液中;隨后的烘烤使溶劑蒸發(fā),形成堅(jiān)固的薄膜。

圖-旋涂工藝

光刻膠和聚酰亞胺(PI)是常見的有機(jī)材料,可以在晶圓上旋涂,厚度通常在0.5至20μm之間,但一些特殊用途的光刻膠(例如基于環(huán)氧樹脂的SU-8)可以超過200μm。有機(jī)聚合物通常懸浮在溶劑溶液中;隨后的烘烤使溶劑蒸發(fā),形成堅(jiān)固的薄膜。

圖-光敏PI膠

二、光刻

光刻工藝,它涉及了三個(gè)連續(xù)的步驟:

圖-光敏PI膠

二、光刻

光刻工藝,它涉及了三個(gè)連續(xù)的步驟:- 光刻膠(Photoresist)的應(yīng)用,它是一種感光乳劑層;

- 光學(xué)曝光(Exposure),將掩膜版(mask)上的圖像打印到光刻膠上;

- 浸入顯影溶液(Developer)中,以溶解曝光后的光刻膠并使?jié)撓窨梢姟?/span>

圖-MEMS加工工藝圖譜

1、掩膜版(Mask)與光刻膠(Photoresist)

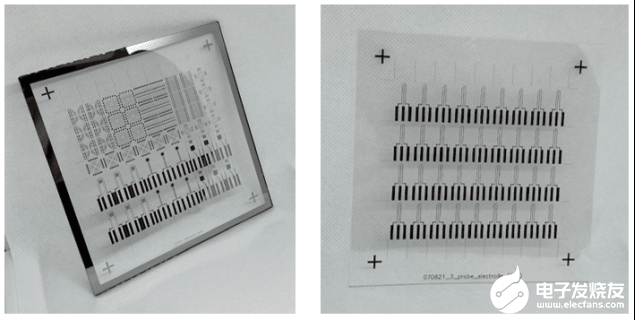

掩膜版(Mask),是在透明的熔融石英或鈉鈣玻璃基板上,構(gòu)建一層含有圖案的不透明層,如鉻、或氧化鐵層制成。掩膜版上的圖案是使用計(jì)算機(jī)輔助設(shè)計(jì)(CAD)工具生成的,并通常通過電子束或激光束等技術(shù)轉(zhuǎn)移到不透明層中。完整的MEMS / IC加工中,通常涉及使用不同的掩膜版,進(jìn)行多次光刻操作。

圖-MEMS加工工藝圖譜

1、掩膜版(Mask)與光刻膠(Photoresist)

掩膜版(Mask),是在透明的熔融石英或鈉鈣玻璃基板上,構(gòu)建一層含有圖案的不透明層,如鉻、或氧化鐵層制成。掩膜版上的圖案是使用計(jì)算機(jī)輔助設(shè)計(jì)(CAD)工具生成的,并通常通過電子束或激光束等技術(shù)轉(zhuǎn)移到不透明層中。完整的MEMS / IC加工中,通常涉及使用不同的掩膜版,進(jìn)行多次光刻操作。

圖-掩膜版

光刻膠(Photoresist)是一種光敏有機(jī)樹脂材料,它通過前文所述的旋涂工藝(Spin-on)沉積在晶圓上,典型厚度在0.5μm至10μm之間。特殊類型的光刻膠可以旋轉(zhuǎn)至超過200μm 的厚度,但較厚的光刻膠對(duì)曝光和關(guān)鍵尺寸(如較小的線寬)提出了較大挑戰(zhàn)。

圖-掩膜版

光刻膠(Photoresist)是一種光敏有機(jī)樹脂材料,它通過前文所述的旋涂工藝(Spin-on)沉積在晶圓上,典型厚度在0.5μm至10μm之間。特殊類型的光刻膠可以旋轉(zhuǎn)至超過200μm 的厚度,但較厚的光刻膠對(duì)曝光和關(guān)鍵尺寸(如較小的線寬)提出了較大挑戰(zhàn)。

圖-光刻膠旋涂

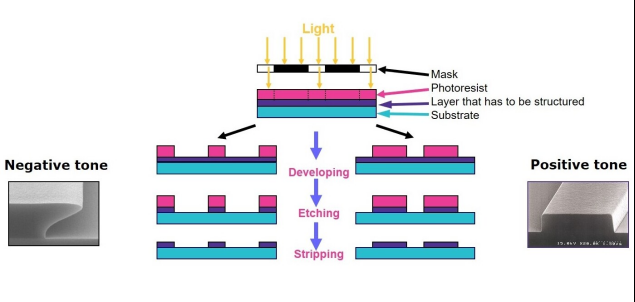

光刻膠含有正性(Positive)或負(fù)性(Negative) 敏化劑成分。對(duì)于正性光刻膠,其敏化劑可防止未曝光的光刻膠在浸入顯影液期間溶解。暴露在 200 至 450 nm 范圍內(nèi)的光(紫外線,也有更高頻率的光)下會(huì)分解敏化劑,導(dǎo)致曝光區(qū)域立即溶解在顯影液中。負(fù)性光刻膠中發(fā)生的過程恰恰相反——曝光區(qū)域保留,未曝光區(qū)域溶解在顯影劑中。

圖-光刻膠旋涂

光刻膠含有正性(Positive)或負(fù)性(Negative) 敏化劑成分。對(duì)于正性光刻膠,其敏化劑可防止未曝光的光刻膠在浸入顯影液期間溶解。暴露在 200 至 450 nm 范圍內(nèi)的光(紫外線,也有更高頻率的光)下會(huì)分解敏化劑,導(dǎo)致曝光區(qū)域立即溶解在顯影液中。負(fù)性光刻膠中發(fā)生的過程恰恰相反——曝光區(qū)域保留,未曝光區(qū)域溶解在顯影劑中。

圖-光刻膠的正性或負(fù)性

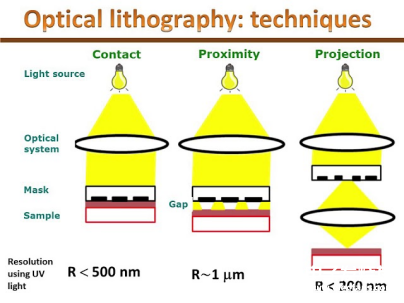

2、光學(xué)曝光(Exposure)

光學(xué)曝光,有三種不同模式:接觸(Contact)、接近(Proximity)或投影(Projection)。在接觸模式的光刻中,掩膜版接觸晶圓。這通常會(huì)縮短掩膜版的壽命,并在晶圓和掩膜版上留下不需要的光刻膠殘留物。在接近模式的光刻中,掩膜版距離光刻膠表面25至50μm以內(nèi)。在投影模式的光刻中,通過復(fù)雜的光學(xué)器件將掩膜版的圖像投影到晶圓上。

圖-光刻膠的正性或負(fù)性

2、光學(xué)曝光(Exposure)

光學(xué)曝光,有三種不同模式:接觸(Contact)、接近(Proximity)或投影(Projection)。在接觸模式的光刻中,掩膜版接觸晶圓。這通常會(huì)縮短掩膜版的壽命,并在晶圓和掩膜版上留下不需要的光刻膠殘留物。在接近模式的光刻中,掩膜版距離光刻膠表面25至50μm以內(nèi)。在投影模式的光刻中,通過復(fù)雜的光學(xué)器件將掩膜版的圖像投影到晶圓上。

圖-光學(xué)曝光有三種不同模式

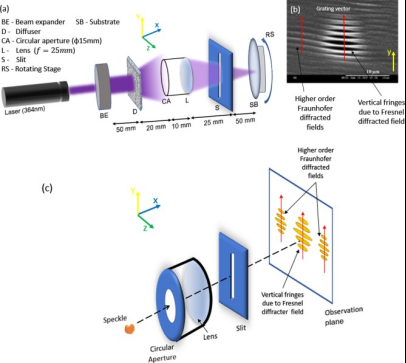

分辨率(Resolution)定義為光學(xué)系統(tǒng)可以解析的最小特征,很少成為微加工應(yīng)用的限制。這里通常會(huì)提到一個(gè)菲涅耳衍射(Fresnel diffraction)的概念,主要是指掩膜版上的圖形非常小,光波在這種情況下透過孔徑會(huì)發(fā)生衍射。

圖-光學(xué)曝光有三種不同模式

分辨率(Resolution)定義為光學(xué)系統(tǒng)可以解析的最小特征,很少成為微加工應(yīng)用的限制。這里通常會(huì)提到一個(gè)菲涅耳衍射(Fresnel diffraction)的概念,主要是指掩膜版上的圖形非常小,光波在這種情況下透過孔徑會(huì)發(fā)生衍射。

圖- 菲涅耳衍射

所以,對(duì)于接近模式的光刻系統(tǒng),分辨率被菲涅耳衍射限制為最小值約5μm。在接觸系統(tǒng)中,分辨率約為1至2μm。而對(duì)于投影系統(tǒng),分辨率由 0.5×λ/NA給出,其中λ是波長(~400nm或更高),NA是光學(xué)器件的數(shù)值孔徑(對(duì)于 MEMS 中使用的步進(jìn)器,數(shù)值孔徑約為0.25),投影系統(tǒng)光刻的分辨率通常優(yōu)于1μm。

在接近模式下,掩膜版與光刻膠的距離在25至50μm范圍內(nèi)。菲涅耳衍射將分辨率和最小特征尺寸限制為~5μm。在投影模式下,復(fù)雜的光學(xué)器件將掩模成像到光刻膠上。分辨率通常優(yōu)于1μm。

圖- 菲涅耳衍射

所以,對(duì)于接近模式的光刻系統(tǒng),分辨率被菲涅耳衍射限制為最小值約5μm。在接觸系統(tǒng)中,分辨率約為1至2μm。而對(duì)于投影系統(tǒng),分辨率由 0.5×λ/NA給出,其中λ是波長(~400nm或更高),NA是光學(xué)器件的數(shù)值孔徑(對(duì)于 MEMS 中使用的步進(jìn)器,數(shù)值孔徑約為0.25),投影系統(tǒng)光刻的分辨率通常優(yōu)于1μm。

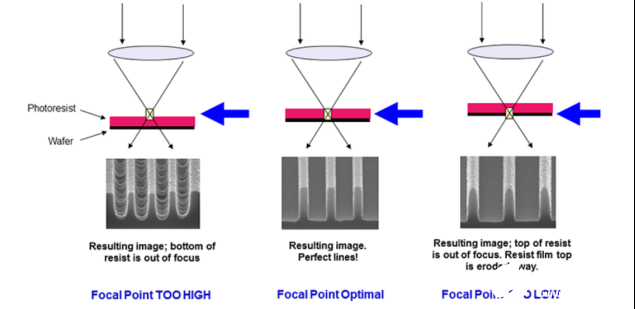

在接近模式下,掩膜版與光刻膠的距離在25至50μm范圍內(nèi)。菲涅耳衍射將分辨率和最小特征尺寸限制為~5μm。在投影模式下,復(fù)雜的光學(xué)器件將掩模成像到光刻膠上。分辨率通常優(yōu)于1μm。焦深(Depth of focus)是對(duì)光刻更嚴(yán)格的限制,特別是考慮到需要曝光較厚的光刻膠或適應(yīng)晶圓上的幾何高度變化。接觸式和接近式系統(tǒng)的焦深很差,也受到菲涅爾衍射的限制。 在投影系統(tǒng)中,可以通過調(diào)整焦點(diǎn)設(shè)置來移動(dòng)圖像平面,但一旦固定,該平面的焦深就會(huì)限制為 ±0.5 × λ/NA^2,也就是說,焦深通常限制在幾微米。投影模式的光刻系統(tǒng)顯然是一種優(yōu)越的方法,但系統(tǒng)的成本可能比接近模式或接觸模式的系統(tǒng)高得多。

圖- 曝光的焦深

雖然對(duì)于MEMS加工來說,大多數(shù)光刻系統(tǒng)的分辨率并不是關(guān)鍵限制因素,但根據(jù)應(yīng)用的性質(zhì),光刻可能具有挑戰(zhàn)性,比如涉及有挑戰(zhàn)的光刻工藝包括:較厚光刻膠的曝光、景園地形高度變化、正面到背面圖案對(duì)準(zhǔn)等。

3、光刻膠厚度對(duì)光刻的影響

較厚的光刻膠通常用作深度結(jié)構(gòu)蝕刻的保護(hù)掩模層,也可用作金屬微結(jié)構(gòu)電鍍的模板。實(shí)現(xiàn)較厚的光刻膠涂覆基材可以通過多次旋涂應(yīng)用(總計(jì)高達(dá)20μm)或通過以較慢的速度旋轉(zhuǎn)特殊的粘性光刻膠溶液(高達(dá)100μm)來實(shí)現(xiàn)。當(dāng)然,隨著光刻膠厚度的增加,保持晶圓上的厚度控制和均勻性變得困難。

圖- 曝光的焦深

雖然對(duì)于MEMS加工來說,大多數(shù)光刻系統(tǒng)的分辨率并不是關(guān)鍵限制因素,但根據(jù)應(yīng)用的性質(zhì),光刻可能具有挑戰(zhàn)性,比如涉及有挑戰(zhàn)的光刻工藝包括:較厚光刻膠的曝光、景園地形高度變化、正面到背面圖案對(duì)準(zhǔn)等。

3、光刻膠厚度對(duì)光刻的影響

較厚的光刻膠通常用作深度結(jié)構(gòu)蝕刻的保護(hù)掩模層,也可用作金屬微結(jié)構(gòu)電鍍的模板。實(shí)現(xiàn)較厚的光刻膠涂覆基材可以通過多次旋涂應(yīng)用(總計(jì)高達(dá)20μm)或通過以較慢的速度旋轉(zhuǎn)特殊的粘性光刻膠溶液(高達(dá)100μm)來實(shí)現(xiàn)。當(dāng)然,隨著光刻膠厚度的增加,保持晶圓上的厚度控制和均勻性變得困難。

圖-需要較厚的光刻膠用作深度結(jié)構(gòu)(深寬比)蝕刻的保護(hù)掩模層

圖案化較厚的光刻膠也是有挑戰(zhàn)的,這是因?yàn)楣饪滔到y(tǒng)的曝光焦深有限,曝光厚度超過5μm的光刻膠通常會(huì)降低最小可分辨特征尺寸,你可以想象:光刻膠內(nèi)的不同深度將得到不同的成像。

最終結(jié)果是曝光區(qū)域中的光刻膠沿著圖形化的輪廓傾斜。出于一般準(zhǔn)則,最大縱橫比(光刻膠厚度與最小特征尺寸之比)約為三,換句話說,可實(shí)現(xiàn)的最小特征尺寸(例如,線寬或線之間的間距)大于光刻膠的三分之一 厚度。

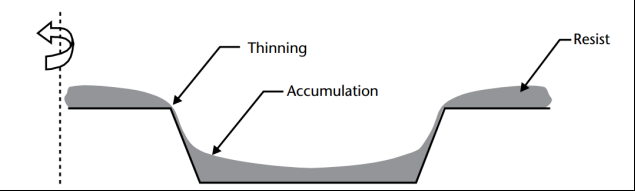

4、地形高度變化對(duì)光刻的影響

晶圓表面形貌的變化(例如深腔和溝槽)在 MEMS 器件中很常見,并對(duì)光刻膠旋轉(zhuǎn)和成像都提出了挑戰(zhàn)。對(duì)于深度超過 10 μm 的空腔,凸角處的光刻膠變薄以及空腔內(nèi)的堆積會(huì)產(chǎn)生曝光問題以及蝕刻期間留下的光刻膠厚度不足的問題。針對(duì)惡劣地形的光刻膠涂層的最新發(fā)展有兩種:噴涂光刻膠和電鍍光刻膠。

圖-需要較厚的光刻膠用作深度結(jié)構(gòu)(深寬比)蝕刻的保護(hù)掩模層

圖案化較厚的光刻膠也是有挑戰(zhàn)的,這是因?yàn)楣饪滔到y(tǒng)的曝光焦深有限,曝光厚度超過5μm的光刻膠通常會(huì)降低最小可分辨特征尺寸,你可以想象:光刻膠內(nèi)的不同深度將得到不同的成像。

最終結(jié)果是曝光區(qū)域中的光刻膠沿著圖形化的輪廓傾斜。出于一般準(zhǔn)則,最大縱橫比(光刻膠厚度與最小特征尺寸之比)約為三,換句話說,可實(shí)現(xiàn)的最小特征尺寸(例如,線寬或線之間的間距)大于光刻膠的三分之一 厚度。

4、地形高度變化對(duì)光刻的影響

晶圓表面形貌的變化(例如深腔和溝槽)在 MEMS 器件中很常見,并對(duì)光刻膠旋轉(zhuǎn)和成像都提出了挑戰(zhàn)。對(duì)于深度超過 10 μm 的空腔,凸角處的光刻膠變薄以及空腔內(nèi)的堆積會(huì)產(chǎn)生曝光問題以及蝕刻期間留下的光刻膠厚度不足的問題。針對(duì)惡劣地形的光刻膠涂層的最新發(fā)展有兩種:噴涂光刻膠和電鍍光刻膠。

圖-旋涂光刻膠在地形高度變化嚴(yán)重的表面上產(chǎn)生的不良影響。拐角處的光刻膠很薄,并積聚在空腔中。

由于焦深有限,在高度變化超過 10 μm 的表面上曝光圖案也是一項(xiàng)艱巨的任務(wù)。接觸式和接近式光刻系統(tǒng)不適合此任務(wù),除非分辨率的顯著降低是可以接受的。在高度級(jí)別變化的數(shù)量有限(例如,小于3個(gè))的某些情況下,可以使用投影式光刻系統(tǒng)來在這些高度中的每一個(gè)級(jí)別進(jìn)行具有相應(yīng)的焦點(diǎn)調(diào)整的曝光。當(dāng)然,這是昂貴的,因?yàn)檠谀:推毓獾臄?shù)量隨著高度級(jí)別的數(shù)量線性增加。

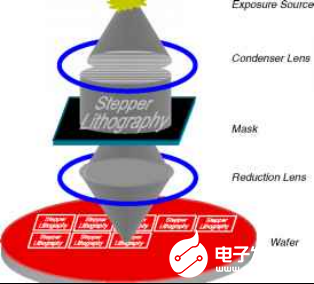

5、視場(field of view)對(duì)光刻的影響

視場是晶圓上任意時(shí)刻曝光的區(qū)域范圍。在接近式和接觸式光刻系統(tǒng)中,視場覆蓋整個(gè)晶圓。而在投影系統(tǒng)中,視場通常小于1×1cm^2。所以需要通過在二維陣列中步進(jìn)小視場來曝光整個(gè)晶圓,因此稱為步進(jìn)機(jī)。在一些應(yīng)用中,設(shè)備結(jié)構(gòu)可能跨越超過視場的尺寸。對(duì)此的補(bǔ)救措施稱為視場拼接,其中兩個(gè)或多個(gè)不同的場順序曝光,場的邊緣重疊。

圖-旋涂光刻膠在地形高度變化嚴(yán)重的表面上產(chǎn)生的不良影響。拐角處的光刻膠很薄,并積聚在空腔中。

由于焦深有限,在高度變化超過 10 μm 的表面上曝光圖案也是一項(xiàng)艱巨的任務(wù)。接觸式和接近式光刻系統(tǒng)不適合此任務(wù),除非分辨率的顯著降低是可以接受的。在高度級(jí)別變化的數(shù)量有限(例如,小于3個(gè))的某些情況下,可以使用投影式光刻系統(tǒng)來在這些高度中的每一個(gè)級(jí)別進(jìn)行具有相應(yīng)的焦點(diǎn)調(diào)整的曝光。當(dāng)然,這是昂貴的,因?yàn)檠谀:推毓獾臄?shù)量隨著高度級(jí)別的數(shù)量線性增加。

5、視場(field of view)對(duì)光刻的影響

視場是晶圓上任意時(shí)刻曝光的區(qū)域范圍。在接近式和接觸式光刻系統(tǒng)中,視場覆蓋整個(gè)晶圓。而在投影系統(tǒng)中,視場通常小于1×1cm^2。所以需要通過在二維陣列中步進(jìn)小視場來曝光整個(gè)晶圓,因此稱為步進(jìn)機(jī)。在一些應(yīng)用中,設(shè)備結(jié)構(gòu)可能跨越超過視場的尺寸。對(duì)此的補(bǔ)救措施稱為視場拼接,其中兩個(gè)或多個(gè)不同的場順序曝光,場的邊緣重疊。

圖-步進(jìn)機(jī)

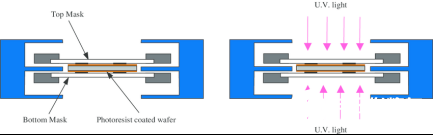

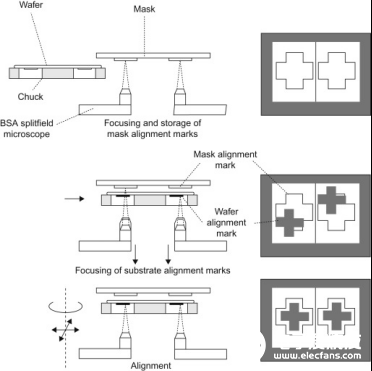

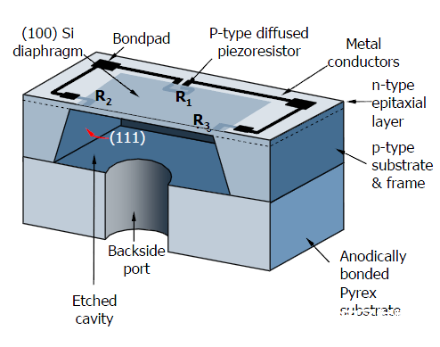

6、需要雙面光刻的情況

有時(shí),晶圓正反兩面的光刻圖案需要高精度地相互對(duì)準(zhǔn)。例如,商用壓力傳感器的制造需要在晶片的正面上形成壓阻傳感元件,這些元件與晶片背面上的空腔的邊緣對(duì)齊。不同的正面到背面對(duì)準(zhǔn)方法(也稱為雙面對(duì)準(zhǔn))已被發(fā)展出來,而且應(yīng)使用雙面拋光的晶圓。

圖-步進(jìn)機(jī)

6、需要雙面光刻的情況

有時(shí),晶圓正反兩面的光刻圖案需要高精度地相互對(duì)準(zhǔn)。例如,商用壓力傳感器的制造需要在晶片的正面上形成壓阻傳感元件,這些元件與晶片背面上的空腔的邊緣對(duì)齊。不同的正面到背面對(duì)準(zhǔn)方法(也稱為雙面對(duì)準(zhǔn))已被發(fā)展出來,而且應(yīng)使用雙面拋光的晶圓。

圖-壓力傳感器

SüSS是早期就提供能夠雙面對(duì)準(zhǔn)和曝光的設(shè)備,比如早期的MA-6,它將掩模上的十字線標(biāo)記與晶圓背面的十字線標(biāo)記對(duì)齊。首先,通過一組雙物鏡從下方觀察機(jī)械夾緊的掩模上的對(duì)準(zhǔn)標(biāo)記,并存儲(chǔ)圖像。然后,晶片上裝載有面向顯微鏡物鏡的背面對(duì)準(zhǔn)標(biāo)記,并定位成使得這些標(biāo)記與存儲(chǔ)的圖像對(duì)準(zhǔn)。對(duì)準(zhǔn)后,以接近或接觸模式完成掩模在晶圓正面的曝光。典型的配準(zhǔn)誤差(或錯(cuò)位)小于2μm。

圖-壓力傳感器

SüSS是早期就提供能夠雙面對(duì)準(zhǔn)和曝光的設(shè)備,比如早期的MA-6,它將掩模上的十字線標(biāo)記與晶圓背面的十字線標(biāo)記對(duì)齊。首先,通過一組雙物鏡從下方觀察機(jī)械夾緊的掩模上的對(duì)準(zhǔn)標(biāo)記,并存儲(chǔ)圖像。然后,晶片上裝載有面向顯微鏡物鏡的背面對(duì)準(zhǔn)標(biāo)記,并定位成使得這些標(biāo)記與存儲(chǔ)的圖像對(duì)準(zhǔn)。對(duì)準(zhǔn)后,以接近或接觸模式完成掩模在晶圓正面的曝光。典型的配準(zhǔn)誤差(或錯(cuò)位)小于2μm。

圖-SüSS雙面對(duì)準(zhǔn)曝光

三、刻蝕

在刻蝕中,目標(biāo)是使用光刻膠作為掩膜版選擇性地去除材料,這樣掩膜版的圖案可以直接刻蝕到硅基板或薄膜中。

MEMS制造的刻蝕工藝不同于IC行業(yè)的傳統(tǒng)刻蝕工藝,因?yàn)樗婕傲撕芏嗉?xì)分的刻蝕技術(shù),并根據(jù)刻蝕劑、各向同性、及相對(duì)其他材料的選擇性(刻蝕速率比)來進(jìn)行區(qū)分。

圖-SüSS雙面對(duì)準(zhǔn)曝光

三、刻蝕

在刻蝕中,目標(biāo)是使用光刻膠作為掩膜版選擇性地去除材料,這樣掩膜版的圖案可以直接刻蝕到硅基板或薄膜中。

MEMS制造的刻蝕工藝不同于IC行業(yè)的傳統(tǒng)刻蝕工藝,因?yàn)樗婕傲撕芏嗉?xì)分的刻蝕技術(shù),并根據(jù)刻蝕劑、各向同性、及相對(duì)其他材料的選擇性(刻蝕速率比)來進(jìn)行區(qū)分。 ?圖-MEMS工藝流程圖

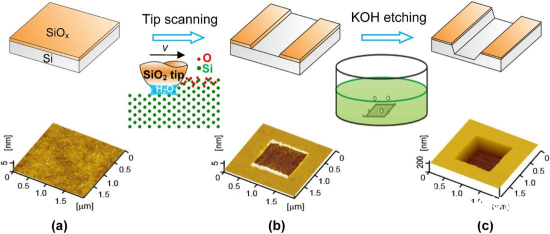

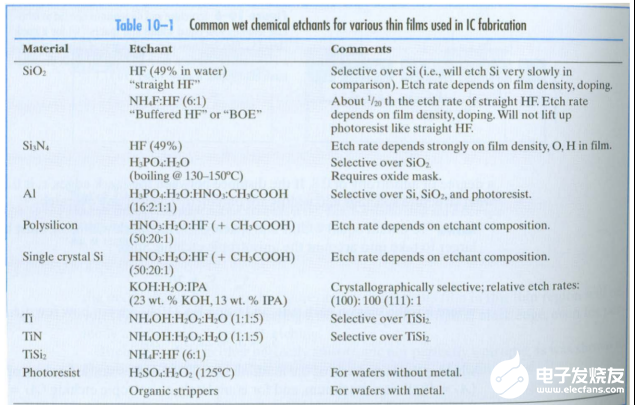

1、濕法刻蝕

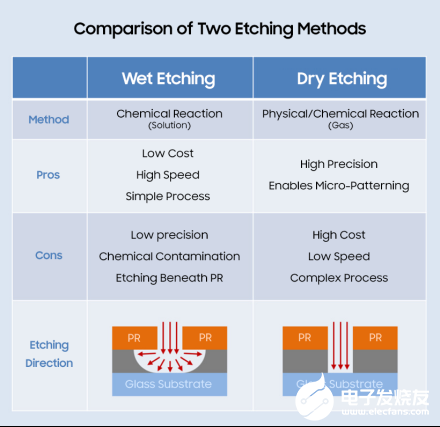

1)濕法與干法刻蝕

濕法(Wet)刻蝕是一種刻蝕方法,是將刻蝕介質(zhì)浸泡在刻蝕劑液體內(nèi)進(jìn)行刻蝕的技術(shù)。濕法刻蝕具有低成本批量制造的優(yōu)點(diǎn),可以同時(shí)刻蝕25至50個(gè)的晶圓。干法(Dry)刻蝕涉及使用反應(yīng)氣體,通常在低壓等離子體中,通常也需要超凈管道將高純度的反應(yīng)氣體帶入真空室等環(huán)境,所以設(shè)備比較復(fù)雜。

?圖-MEMS工藝流程圖

1、濕法刻蝕

1)濕法與干法刻蝕

濕法(Wet)刻蝕是一種刻蝕方法,是將刻蝕介質(zhì)浸泡在刻蝕劑液體內(nèi)進(jìn)行刻蝕的技術(shù)。濕法刻蝕具有低成本批量制造的優(yōu)點(diǎn),可以同時(shí)刻蝕25至50個(gè)的晶圓。干法(Dry)刻蝕涉及使用反應(yīng)氣體,通常在低壓等離子體中,通常也需要超凈管道將高純度的反應(yīng)氣體帶入真空室等環(huán)境,所以設(shè)備比較復(fù)雜。

圖-濕法刻蝕與干法刻蝕

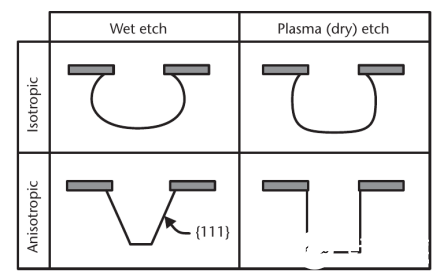

2)各向同性與各向異性

各向同性(Isotropic)刻蝕劑在所有方向上均勻刻蝕,產(chǎn)生圓形橫截面特征。相比之下,各向異性(Anisotropic)刻蝕劑在某些方向上優(yōu)先于其他方向進(jìn)行刻蝕,從而形成由平坦且輪廓分明的表面勾勒出的溝槽或空腔,這些表面甚至都不一定需要垂直于晶圓表面。

圖-濕法刻蝕與干法刻蝕

2)各向同性與各向異性

各向同性(Isotropic)刻蝕劑在所有方向上均勻刻蝕,產(chǎn)生圓形橫截面特征。相比之下,各向異性(Anisotropic)刻蝕劑在某些方向上優(yōu)先于其他方向進(jìn)行刻蝕,從而形成由平坦且輪廓分明的表面勾勒出的溝槽或空腔,這些表面甚至都不一定需要垂直于晶圓表面。

圖-四種不同類型刻蝕方法產(chǎn)生的橫截面溝槽輪廓示意圖

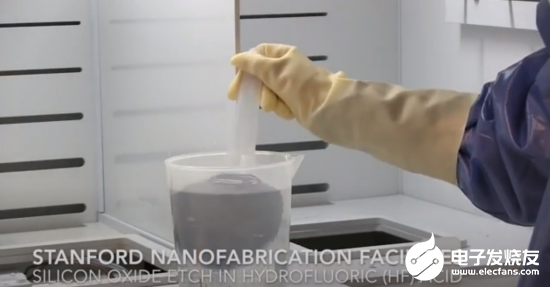

各向同性濕法刻蝕

常見的一種用于硅的各向同性濕法刻蝕劑是HNA,是氫氟酸(HF)、硝酸(HNO3)和乙酸(CH3COOH) 的混合物。在化學(xué)反應(yīng)中,硝酸氧化硅,然后用氫氟酸溶解硅。硅的刻蝕速率可以從0.1到超過100μm/min變化,具體取決于混合物中酸的比例。但刻蝕均勻性通常難以控制。

圖-四種不同類型刻蝕方法產(chǎn)生的橫截面溝槽輪廓示意圖

各向同性濕法刻蝕

常見的一種用于硅的各向同性濕法刻蝕劑是HNA,是氫氟酸(HF)、硝酸(HNO3)和乙酸(CH3COOH) 的混合物。在化學(xué)反應(yīng)中,硝酸氧化硅,然后用氫氟酸溶解硅。硅的刻蝕速率可以從0.1到超過100μm/min變化,具體取決于混合物中酸的比例。但刻蝕均勻性通常難以控制。

圖-各向同性濕法刻蝕劑-氫氟酸

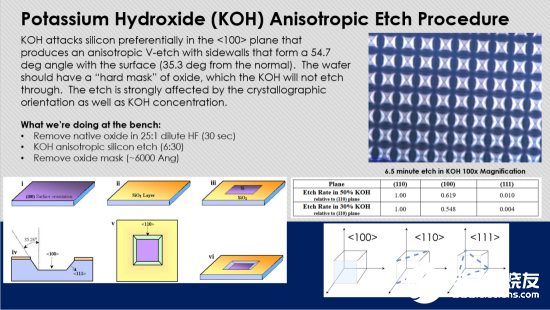

各向異性濕法刻蝕

各向異性濕法刻蝕劑也稱為 取向相關(guān)刻蝕劑(ODE,Orientation-Dependent Etchants),因?yàn)樗鼈兊目涛g速率與晶體方向相關(guān)。

各向異性濕法刻蝕劑包括堿金屬氫氧化物(例如 NaOH、KOH、CsOH)、氫氧化物和季銨氫氧化物(例如 NH4OH、N(CH3)4OH)、及與鄰苯二酚(EDP)在水中混合的乙二胺。通常將刻蝕劑溶液加熱至 70°C–100°C。

圖-各向同性濕法刻蝕劑-氫氟酸

各向異性濕法刻蝕

各向異性濕法刻蝕劑也稱為 取向相關(guān)刻蝕劑(ODE,Orientation-Dependent Etchants),因?yàn)樗鼈兊目涛g速率與晶體方向相關(guān)。

各向異性濕法刻蝕劑包括堿金屬氫氧化物(例如 NaOH、KOH、CsOH)、氫氧化物和季銨氫氧化物(例如 NH4OH、N(CH3)4OH)、及與鄰苯二酚(EDP)在水中混合的乙二胺。通常將刻蝕劑溶液加熱至 70°C–100°C。KOH是迄今為止最常見的ODE。刻蝕速率通常在[100]方向給出,對(duì)應(yīng)于刻蝕前沿為{110}平面。{110}面在KOH中的刻蝕速度大約是{100}面的兩倍,而{111}面的刻蝕速度比{100}面慢大約100倍。后一個(gè)特征通常用于在{100}硅片上制作V形凹槽和溝槽,這些凹槽和溝槽由{111}晶面精確描繪。

圖-各向異性濕法刻蝕劑-KOH

對(duì)于重?fù)诫sp型(p++)硅,KOH和其他堿性刻蝕劑的刻蝕速率也會(huì)大大減慢,因?yàn)檫M(jìn)行刻蝕反應(yīng)所需的電子濃度較低,會(huì)影響其刻蝕過程中氧化還原中的電子轉(zhuǎn)移。因此,P++ 硅通常用作刻蝕停止層。KOH 溶液中未摻雜或 n 型硅的刻蝕速率約為0.5至4μm/min,具體取決于溫度和KOH濃度,但在摻雜劑濃度高于1×10^20cm?3的p++硅中,刻蝕速率下降了500倍以上。

二氧化硅的刻蝕速度約為10nm/min,可用作極短刻蝕的掩模層。LPCVD氮化硅是一種優(yōu)異的抗KOH刻蝕掩模材料。而光刻膠在熱堿性溶液中會(huì)被快速刻蝕,因此不適合用于掩蓋這些刻蝕劑。

圖-各向異性濕法刻蝕劑-KOH

對(duì)于重?fù)诫sp型(p++)硅,KOH和其他堿性刻蝕劑的刻蝕速率也會(huì)大大減慢,因?yàn)檫M(jìn)行刻蝕反應(yīng)所需的電子濃度較低,會(huì)影響其刻蝕過程中氧化還原中的電子轉(zhuǎn)移。因此,P++ 硅通常用作刻蝕停止層。KOH 溶液中未摻雜或 n 型硅的刻蝕速率約為0.5至4μm/min,具體取決于溫度和KOH濃度,但在摻雜劑濃度高于1×10^20cm?3的p++硅中,刻蝕速率下降了500倍以上。

二氧化硅的刻蝕速度約為10nm/min,可用作極短刻蝕的掩模層。LPCVD氮化硅是一種優(yōu)異的抗KOH刻蝕掩模材料。而光刻膠在熱堿性溶液中會(huì)被快速刻蝕,因此不適合用于掩蓋這些刻蝕劑。

圖-KOH刻蝕硬膜hard mask

其他各向異性濕法刻蝕劑還有TMAH、EDP等。

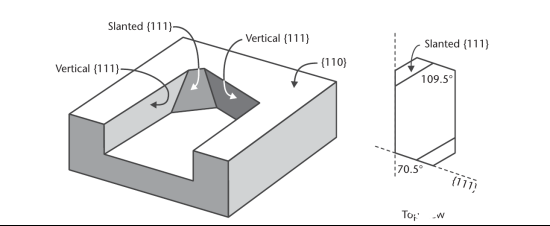

3)刻蝕的三維結(jié)構(gòu)

使用各向異性刻蝕會(huì)產(chǎn)生復(fù)雜的三維多面結(jié)構(gòu)。為此,刻蝕過程也有計(jì)算機(jī)模擬軟件進(jìn)行輔助設(shè)計(jì)。

最容易可視化的結(jié)構(gòu)是在{100}取向晶圓上刻蝕的V形腔。刻蝕前沿從掩模中的開口處開始,并沿<100>方向前進(jìn),該方向是{100}取向基板中的垂直方向,形成具有平坦底部和傾斜側(cè)面的空腔。

空腔的邊是{111}平面,與水平{111}表面成54.7°角。晶圓一側(cè)的定時(shí)刻蝕經(jīng)常用于形成空腔或薄膜。而在四個(gè)等效但相交的{111}平面上自我限制,形成V形凹坑(倒金字塔形)。通過從晶片兩側(cè)刻蝕對(duì)齊圖案并允許兩個(gè)垂直刻蝕前沿合并,并開始側(cè)面刻蝕,然后在預(yù)定時(shí)間后停止刻蝕,在{100}晶片中也可以形成沙漏形和傾斜形狀的端口。

圖-KOH刻蝕硬膜hard mask

其他各向異性濕法刻蝕劑還有TMAH、EDP等。

3)刻蝕的三維結(jié)構(gòu)

使用各向異性刻蝕會(huì)產(chǎn)生復(fù)雜的三維多面結(jié)構(gòu)。為此,刻蝕過程也有計(jì)算機(jī)模擬軟件進(jìn)行輔助設(shè)計(jì)。

最容易可視化的結(jié)構(gòu)是在{100}取向晶圓上刻蝕的V形腔。刻蝕前沿從掩模中的開口處開始,并沿<100>方向前進(jìn),該方向是{100}取向基板中的垂直方向,形成具有平坦底部和傾斜側(cè)面的空腔。

空腔的邊是{111}平面,與水平{111}表面成54.7°角。晶圓一側(cè)的定時(shí)刻蝕經(jīng)常用于形成空腔或薄膜。而在四個(gè)等效但相交的{111}平面上自我限制,形成V形凹坑(倒金字塔形)。通過從晶片兩側(cè)刻蝕對(duì)齊圖案并允許兩個(gè)垂直刻蝕前沿合并,并開始側(cè)面刻蝕,然后在預(yù)定時(shí)間后停止刻蝕,在{100}晶片中也可以形成沙漏形和傾斜形狀的端口。

圖-{100}取向硅中空腔的各向異性刻蝕示意圖:(a)空腔、V形凹坑以及薄膜;(b)從晶片的兩側(cè)進(jìn)行刻蝕可以產(chǎn)生多種不同的形狀,包括沙漏形和斜孔

{110}晶圓中刻蝕溝槽的形狀完全不同。在硅{110}晶片中,八個(gè)等效的{111}面中的四個(gè)垂直于{110}晶片表面。其余四個(gè){111}面相對(duì)于表面傾斜35.3°。四個(gè)垂直的{111}平面相交形成內(nèi)角為70.5°的平行四邊形。{110}晶片上刻蝕的凹槽具有由六個(gè){111}平面(四個(gè)垂直平面和兩個(gè)傾斜平面)描繪的復(fù)雜多邊形的外觀。在{110}晶圓上進(jìn)行刻蝕可用于形成具有垂直側(cè)壁的溝槽,彼此不正交。

圖-{100}取向硅中空腔的各向異性刻蝕示意圖:(a)空腔、V形凹坑以及薄膜;(b)從晶片的兩側(cè)進(jìn)行刻蝕可以產(chǎn)生多種不同的形狀,包括沙漏形和斜孔

{110}晶圓中刻蝕溝槽的形狀完全不同。在硅{110}晶片中,八個(gè)等效的{111}面中的四個(gè)垂直于{110}晶片表面。其余四個(gè){111}面相對(duì)于表面傾斜35.3°。四個(gè)垂直的{111}平面相交形成內(nèi)角為70.5°的平行四邊形。{110}晶片上刻蝕的凹槽具有由六個(gè){111}平面(四個(gè)垂直平面和兩個(gè)傾斜平面)描繪的復(fù)雜多邊形的外觀。在{110}晶圓上進(jìn)行刻蝕可用于形成具有垂直側(cè)壁的溝槽,彼此不正交。

圖-{110}取向硅中的各向異性刻蝕示意圖刻蝕結(jié)構(gòu)由四個(gè)垂直的{111}面和兩個(gè)傾斜的{111}面描繪。垂直的{111}平面相交的角度為70.5°

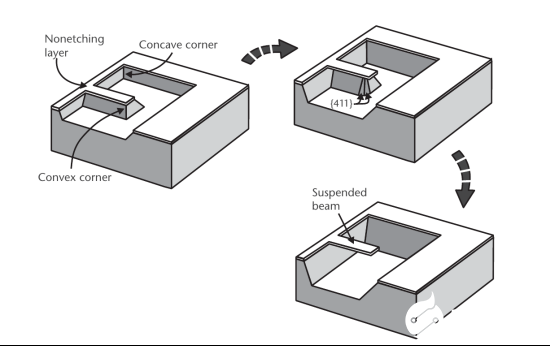

雖然以{111}面為界的凹角在刻蝕過程中保持完整,但凸角會(huì)立即受到攻擊。這是因?yàn)橥菇堑娜魏屋p微腐蝕都會(huì)暴露出{111}面以外的快速刻蝕面(尤其是{411}面),從而加速刻蝕。

因此,掩模布局中的凸角將在刻蝕過程中被底切;換句話說,刻蝕前沿將在掩模層下方進(jìn)行。這種效應(yīng)可以被有意用來形成懸掛在空腔上方的梁。

圖-{110}取向硅中的各向異性刻蝕示意圖刻蝕結(jié)構(gòu)由四個(gè)垂直的{111}面和兩個(gè)傾斜的{111}面描繪。垂直的{111}平面相交的角度為70.5°

雖然以{111}面為界的凹角在刻蝕過程中保持完整,但凸角會(huì)立即受到攻擊。這是因?yàn)橥菇堑娜魏屋p微腐蝕都會(huì)暴露出{111}面以外的快速刻蝕面(尤其是{411}面),從而加速刻蝕。

因此,掩模布局中的凸角將在刻蝕過程中被底切;換句話說,刻蝕前沿將在掩模層下方進(jìn)行。這種效應(yīng)可以被有意用來形成懸掛在空腔上方的梁。 圖-凸角處的刻蝕以及未刻蝕材料(例如氮化硅、p++ 硅)的懸梁形成的圖示。{411}面通常是最快的刻蝕并且出現(xiàn)在凸角處

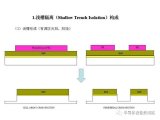

4)小結(jié)

下表給出了各種硅刻蝕劑的比較。

圖-凸角處的刻蝕以及未刻蝕材料(例如氮化硅、p++ 硅)的懸梁形成的圖示。{411}面通常是最快的刻蝕并且出現(xiàn)在凸角處

4)小結(jié)

下表給出了各種硅刻蝕劑的比較。

?2、干法刻蝕

主要涉及電化學(xué)蝕刻(Electrochemical Etching)、等離子蝕刻(Plasma Etching)與反應(yīng)離子刻蝕(RIE)、深度反應(yīng)離子蝕刻(Deep reactive ion etching)。

?2、干法刻蝕

主要涉及電化學(xué)蝕刻(Electrochemical Etching)、等離子蝕刻(Plasma Etching)與反應(yīng)離子刻蝕(RIE)、深度反應(yīng)離子蝕刻(Deep reactive ion etching)。

圖-MEMS工藝流程圖

1)電化學(xué)蝕刻

采用各向異性濕法蝕刻劑具有相對(duì)較大的蝕刻速率(>0.5μm/min),但難以實(shí)現(xiàn)均勻且受控的蝕刻深度。例如在MEMS壓力傳感器的加工中,需要厚度5至20μm、其均勻性控制在0.2μm的薄硅膜,使用定時(shí)蝕刻就很難實(shí)現(xiàn)這一點(diǎn)。

在這種場景中可采用電化學(xué)蝕刻(Electrochemical Etching),其厚度的均勻性控制是通過精確生長的外延層并通過外部施加的電勢控制蝕刻反應(yīng)來實(shí)現(xiàn)的。

圖-MEMS工藝流程圖

1)電化學(xué)蝕刻

采用各向異性濕法蝕刻劑具有相對(duì)較大的蝕刻速率(>0.5μm/min),但難以實(shí)現(xiàn)均勻且受控的蝕刻深度。例如在MEMS壓力傳感器的加工中,需要厚度5至20μm、其均勻性控制在0.2μm的薄硅膜,使用定時(shí)蝕刻就很難實(shí)現(xiàn)這一點(diǎn)。

在這種場景中可采用電化學(xué)蝕刻(Electrochemical Etching),其厚度的均勻性控制是通過精確生長的外延層并通過外部施加的電勢控制蝕刻反應(yīng)來實(shí)現(xiàn)的。

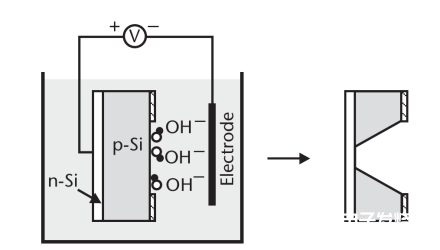

圖-電化學(xué)蝕刻原理示意圖

比如,在p型晶圓上生長的n型外延層形成p-n結(jié)二極管,只有當(dāng)p型側(cè)的電壓高于n型時(shí)才允許導(dǎo)通,稱為正向偏執(zhí);否則,沒有電流通過,稱為反向偏置。

在電化學(xué)蝕刻期間,所施加的電勢使得p-n二極管處于反向偏壓,采用KOH刻蝕劑溶液,n型外延層不會(huì)被蝕刻,p型基板允許被蝕刻。一旦p型襯底被完全去除,蝕刻反應(yīng)就會(huì)在結(jié)處停止,留下一層具有精確厚度的n型硅。

下述是基于電化學(xué)蝕刻實(shí)現(xiàn)MEMS壓力傳感器薄硅膜(為n型外延硅)的示意圖:

圖-電化學(xué)蝕刻原理示意圖

比如,在p型晶圓上生長的n型外延層形成p-n結(jié)二極管,只有當(dāng)p型側(cè)的電壓高于n型時(shí)才允許導(dǎo)通,稱為正向偏執(zhí);否則,沒有電流通過,稱為反向偏置。

在電化學(xué)蝕刻期間,所施加的電勢使得p-n二極管處于反向偏壓,采用KOH刻蝕劑溶液,n型外延層不會(huì)被蝕刻,p型基板允許被蝕刻。一旦p型襯底被完全去除,蝕刻反應(yīng)就會(huì)在結(jié)處停止,留下一層具有精確厚度的n型硅。

下述是基于電化學(xué)蝕刻實(shí)現(xiàn)MEMS壓力傳感器薄硅膜(為n型外延硅)的示意圖:

圖-電化學(xué)蝕刻實(shí)現(xiàn)MEMS壓力傳感器薄硅膜(為n型外延硅)

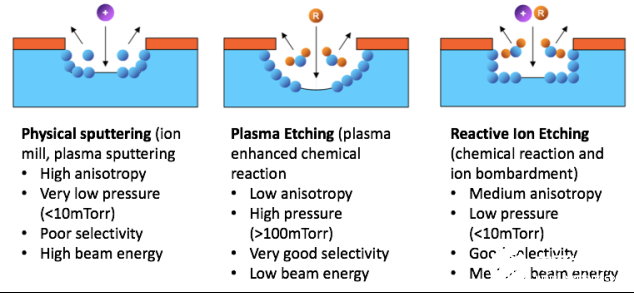

2)等離子蝕刻與反應(yīng)離子刻蝕

等離子蝕刻,是半導(dǎo)體行業(yè)的關(guān)鍵工藝。其中,Applied Materials、Lam Research、SPTS、TEL等公司是硅、二氧化硅、氮化硅、一些金屬材料的等離子蝕刻設(shè)備系統(tǒng)的領(lǐng)先開發(fā)商。

在等離子環(huán)境中,有高度化學(xué)活性的中性原子、分子及自由基的等離子體,這些處于等離子體狀態(tài)的物質(zhì)在電場作用下向基板加速運(yùn)動(dòng),再加上反應(yīng)氣體(例如 SF6、CF4、Cl2、CClF3、NF3等)碰撞,可以對(duì)目標(biāo)進(jìn)行蝕刻。如果這個(gè)過程是純粹的化學(xué)反應(yīng),稱為等離子體蝕刻(Plasma Etching)。

如果化學(xué)反應(yīng)過程中,硅的表面還受到高能粒子轟擊(ion bombardment),兩者發(fā)揮協(xié)同作用,則該過程被稱為反應(yīng)離子蝕刻(Reactive ion etching,RIE)。在RIE中,離子(例如 SFx+)朝向基板的運(yùn)動(dòng)幾乎是垂直的,這使得RIE具有垂直的方向特性。RIE通常用于表面刻蝕加工。

還有一種純粹的物理蝕刻方法是離子銑削(Ion milling),其中先要產(chǎn)生惰性氣體(通常是氬氣)離子,然后通過1kV量級(jí)的電勢在基板上加速。離子的方向性導(dǎo)致非常垂直的蝕刻輪廓。由于不需要化學(xué)反應(yīng),任何材料都可以通過離子銑削進(jìn)行蝕刻。離子銑削速率通常比 RIE 慢得多,并且隨材料的不同而變化很大。

以上三種同屬干法刻蝕,是不是很繞?看下面這個(gè)圖示也許會(huì)清楚一些:

圖-電化學(xué)蝕刻實(shí)現(xiàn)MEMS壓力傳感器薄硅膜(為n型外延硅)

2)等離子蝕刻與反應(yīng)離子刻蝕

等離子蝕刻,是半導(dǎo)體行業(yè)的關(guān)鍵工藝。其中,Applied Materials、Lam Research、SPTS、TEL等公司是硅、二氧化硅、氮化硅、一些金屬材料的等離子蝕刻設(shè)備系統(tǒng)的領(lǐng)先開發(fā)商。

在等離子環(huán)境中,有高度化學(xué)活性的中性原子、分子及自由基的等離子體,這些處于等離子體狀態(tài)的物質(zhì)在電場作用下向基板加速運(yùn)動(dòng),再加上反應(yīng)氣體(例如 SF6、CF4、Cl2、CClF3、NF3等)碰撞,可以對(duì)目標(biāo)進(jìn)行蝕刻。如果這個(gè)過程是純粹的化學(xué)反應(yīng),稱為等離子體蝕刻(Plasma Etching)。

如果化學(xué)反應(yīng)過程中,硅的表面還受到高能粒子轟擊(ion bombardment),兩者發(fā)揮協(xié)同作用,則該過程被稱為反應(yīng)離子蝕刻(Reactive ion etching,RIE)。在RIE中,離子(例如 SFx+)朝向基板的運(yùn)動(dòng)幾乎是垂直的,這使得RIE具有垂直的方向特性。RIE通常用于表面刻蝕加工。

還有一種純粹的物理蝕刻方法是離子銑削(Ion milling),其中先要產(chǎn)生惰性氣體(通常是氬氣)離子,然后通過1kV量級(jí)的電勢在基板上加速。離子的方向性導(dǎo)致非常垂直的蝕刻輪廓。由于不需要化學(xué)反應(yīng),任何材料都可以通過離子銑削進(jìn)行蝕刻。離子銑削速率通常比 RIE 慢得多,并且隨材料的不同而變化很大。

以上三種同屬干法刻蝕,是不是很繞?看下面這個(gè)圖示也許會(huì)清楚一些:

圖-等離子刻蝕、RIE、離子銑削工藝原理示意圖

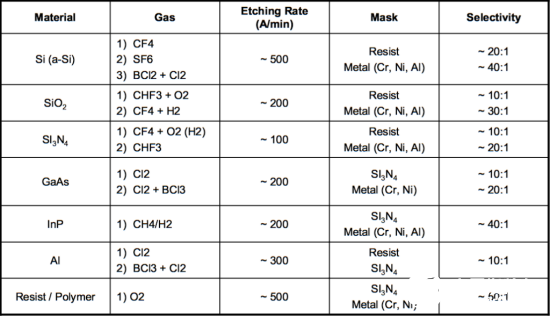

特別對(duì)于RIE來說,化學(xué)反應(yīng)形成的副產(chǎn)物必須具有足夠的揮發(fā)性,以便可以從真空室中排出,這一點(diǎn)至關(guān)重要。例如,在銅蝕刻中,產(chǎn)物CuCl2的揮發(fā)性不夠,因此銅的RIE在實(shí)際應(yīng)用中相當(dāng)困難。下圖總結(jié)了刻蝕不同材料的 RIE 的典型氣體:

圖-等離子刻蝕、RIE、離子銑削工藝原理示意圖

特別對(duì)于RIE來說,化學(xué)反應(yīng)形成的副產(chǎn)物必須具有足夠的揮發(fā)性,以便可以從真空室中排出,這一點(diǎn)至關(guān)重要。例如,在銅蝕刻中,產(chǎn)物CuCl2的揮發(fā)性不夠,因此銅的RIE在實(shí)際應(yīng)用中相當(dāng)困難。下圖總結(jié)了刻蝕不同材料的 RIE 的典型氣體:

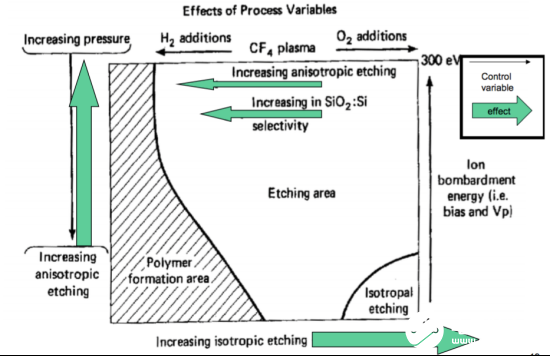

?當(dāng)然,以上刻蝕反應(yīng)都會(huì)隨著具體工藝參數(shù)配方的影響很大,下圖列舉了一些參數(shù)中的變量,上述的3種(等離子刻蝕、RIE、離子銑削)可能相互過渡,所以放在一起介紹:

?當(dāng)然,以上刻蝕反應(yīng)都會(huì)隨著具體工藝參數(shù)配方的影響很大,下圖列舉了一些參數(shù)中的變量,上述的3種(等離子刻蝕、RIE、離子銑削)可能相互過渡,所以放在一起介紹:

圖-等離子刻蝕參數(shù)變量

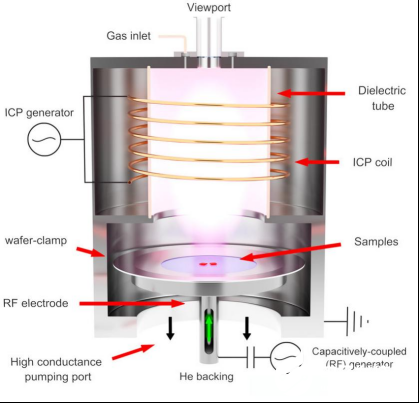

特別的,還有一種電感耦合等離子體反應(yīng)離子蝕刻(Inductively coupled plasma,ICP-RIE)通過外部施加射頻電磁場為電子云提供更大的激發(fā)。電感耦合等離子體增加了離子和中性粒子的密度,從而提高了蝕刻速率。ICP也可以用于體硅刻蝕加工。

圖-等離子刻蝕參數(shù)變量

特別的,還有一種電感耦合等離子體反應(yīng)離子蝕刻(Inductively coupled plasma,ICP-RIE)通過外部施加射頻電磁場為電子云提供更大的激發(fā)。電感耦合等離子體增加了離子和中性粒子的密度,從而提高了蝕刻速率。ICP也可以用于體硅刻蝕加工。

圖-ICP-RIE示意圖,其中金屬線圈就是用于射頻耦合產(chǎn)生射頻電磁場

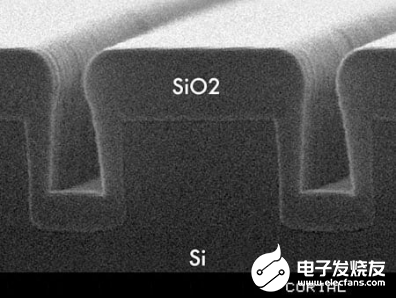

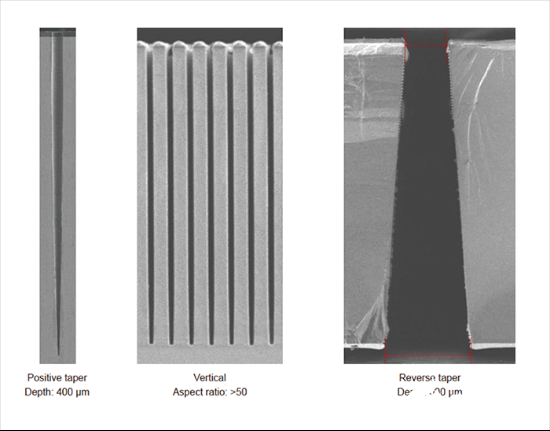

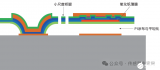

3)深度反應(yīng)離子蝕刻(博世工藝)

傳統(tǒng)的等離子體蝕刻工藝通常用于MEMS加工中形成淺腔。后來20世紀(jì)90年代中期,科學(xué)家們推出了深度反應(yīng)離子蝕刻(Deep reactive ion etching,DRIE)系統(tǒng),可以蝕刻具有幾乎垂直側(cè)壁的高深寬比溝槽,其深度超過可達(dá)500μm。

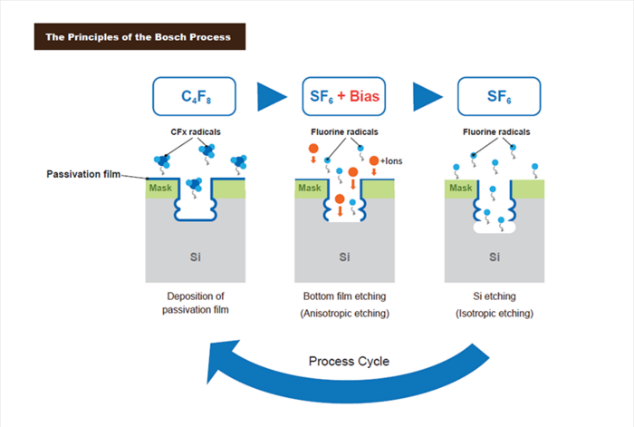

德國斯圖加特的Robert Bosch GmbH的有一種DRIE專利方法,其中蝕刻和沉積步驟在ICP-RIE系統(tǒng)中交替進(jìn)行,具體過程為:薄膜沉積、底部薄膜蝕刻和硅蝕刻。在沉積工藝中,在溝槽的側(cè)壁和底面上沉積鈍化膜。在底部膜蝕刻步驟中,選擇性地蝕刻溝槽底部上的鈍化膜。在硅蝕刻步驟中,僅蝕刻已去除鈍化膜的溝槽底部的硅。

圖-ICP-RIE示意圖,其中金屬線圈就是用于射頻耦合產(chǎn)生射頻電磁場

3)深度反應(yīng)離子蝕刻(博世工藝)

傳統(tǒng)的等離子體蝕刻工藝通常用于MEMS加工中形成淺腔。后來20世紀(jì)90年代中期,科學(xué)家們推出了深度反應(yīng)離子蝕刻(Deep reactive ion etching,DRIE)系統(tǒng),可以蝕刻具有幾乎垂直側(cè)壁的高深寬比溝槽,其深度超過可達(dá)500μm。

德國斯圖加特的Robert Bosch GmbH的有一種DRIE專利方法,其中蝕刻和沉積步驟在ICP-RIE系統(tǒng)中交替進(jìn)行,具體過程為:薄膜沉積、底部薄膜蝕刻和硅蝕刻。在沉積工藝中,在溝槽的側(cè)壁和底面上沉積鈍化膜。在底部膜蝕刻步驟中,選擇性地蝕刻溝槽底部上的鈍化膜。在硅蝕刻步驟中,僅蝕刻已去除鈍化膜的溝槽底部的硅。

圖-Bosch DRIE工藝示意圖

在蝕刻過程中,垂直取向的離子(SFx+)增強(qiáng)了氟自由基,去除溝槽底部沉積而成的鈍化膜,同時(shí)薄膜沿側(cè)壁保持相對(duì)完整。扇形的程度(由于蝕刻的各向同性成分而產(chǎn)生的側(cè)壁紋理)隨配方的不同而變化。

此外,DRIE蝕刻速率會(huì)隨著溝槽深寬比的增加而降低。對(duì)二氧化硅的高選擇性使得蝕刻深溝槽并停止在二氧化硅埋層上成為可能,例如適用于SOI(絕緣體上硅)晶圓。以下是一些Bosch 工藝的效果圖:

圖-Bosch DRIE工藝示意圖

在蝕刻過程中,垂直取向的離子(SFx+)增強(qiáng)了氟自由基,去除溝槽底部沉積而成的鈍化膜,同時(shí)薄膜沿側(cè)壁保持相對(duì)完整。扇形的程度(由于蝕刻的各向同性成分而產(chǎn)生的側(cè)壁紋理)隨配方的不同而變化。

此外,DRIE蝕刻速率會(huì)隨著溝槽深寬比的增加而降低。對(duì)二氧化硅的高選擇性使得蝕刻深溝槽并停止在二氧化硅埋層上成為可能,例如適用于SOI(絕緣體上硅)晶圓。以下是一些Bosch 工藝的效果圖:

圖-Bosch 工藝效果圖

總之,DRIE是形成具有接近垂直側(cè)壁的深溝槽的強(qiáng)大工具,可調(diào)參數(shù)多,結(jié)果要求也多,所以蝕工藝難度大,如以刻蝕的溝槽縱橫比vs速率、良好的均勻性、高垂直度、小扇形等作為優(yōu)化目的,但一般來說所有的優(yōu)化不能同時(shí)進(jìn)行,所以每種掩模圖案和深度都需要刻蝕工藝工程師進(jìn)行工藝開發(fā)。

(全文完)

圖-Bosch 工藝效果圖

總之,DRIE是形成具有接近垂直側(cè)壁的深溝槽的強(qiáng)大工具,可調(diào)參數(shù)多,結(jié)果要求也多,所以蝕工藝難度大,如以刻蝕的溝槽縱橫比vs速率、良好的均勻性、高垂直度、小扇形等作為優(yōu)化目的,但一般來說所有的優(yōu)化不能同時(shí)進(jìn)行,所以每種掩模圖案和深度都需要刻蝕工藝工程師進(jìn)行工藝開發(fā)。

(全文完)審核編輯 黃宇

-

傳感器

+關(guān)注

關(guān)注

2548文章

50668瀏覽量

751951 -

芯片

+關(guān)注

關(guān)注

453文章

50396瀏覽量

421789 -

mems

+關(guān)注

關(guān)注

129文章

3896瀏覽量

190340

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

SMT工藝流程詳解

mems傳感器是什么意思_mems傳感器原理是什么

簡述連接器的工藝流程

芯片底部填充工藝流程有哪些?

上海工研院MEMS取得重大突破,智能傳感器工藝從定制化向標(biāo)準(zhǔn)化持續(xù)邁進(jìn)

一文解析DARM工藝流程

你可能看不懂的硬核傳感器知識(shí):MEMS芯片制造工藝流程

你可能看不懂的硬核傳感器知識(shí):MEMS芯片制造工藝流程

評(píng)論