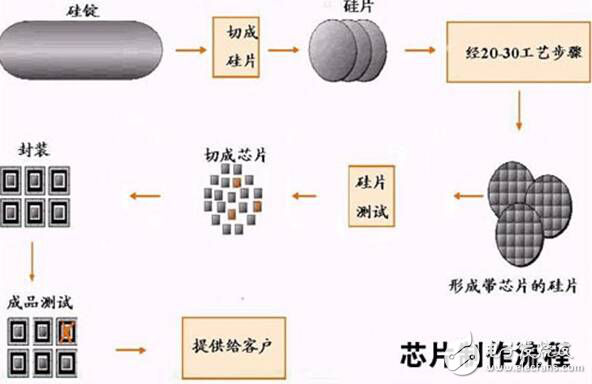

芯片不是天然長出來的,也不是宅男用電腦打印出來的。它的誕生,是個復雜漫長的旅行。簡單來分,芯片制造過程有這么幾個階段:材料制備——單晶硅制造→晶圓片生成芯片前端——芯片構建(Wafer Fabrication)

芯片后端——封裝(Package)→完整測試(Initial Test and Final Test)

備料——硅片制作芯片的制作離不開硅,作為最主要的原料,硅的處理工作至關重要。首先,硅原料要進行化學提純,這一步驟使其達到可供半導體工業使用的原料級別。為了使這些硅原料能夠滿足集成電路制造的加工需要,還必須將其整形,這一步是通過溶化硅原料,然后將液態硅注入大型高溫石英容器來完成的。

而后,將原料進行高溫溶化,然后從高溫容器中采用旋轉拉伸的方式將硅原料取出,此時一個圓柱體的硅單晶錠就產生了。目前,業界最領先工藝生產的是300mm的硅錠,也就是12寸晶圓。

在制成硅錠并確保其是一個絕對的圓柱體之后,下一個步驟就是將這個圓柱體硅錠切片,切片越薄,用料越省,自然可以生產的處理器芯片就更多。切片還要鏡面精加工的處理來確保表面絕對光滑,之后檢查是否有扭曲或其它問題。這一步的質量檢驗尤為重要,它直接決定了成品芯片的質量。

新的切片中要摻入一些物質,使之成為真正的半導體材料,然后在其上刻劃代表著各種邏輯功能的電路。摻入的物質原子進入硅原子之間的空隙,彼此之間發生原子力的作用,從而使得硅原料具有半導體的特性。今天的半導體制造多選擇CMOS工藝(互補型金屬氧化物半導體)。其中,互補一詞表示半導體中N型MOS管和P型MOS管之間的交互作用。N和P在電子工藝中分別代表負極和正極。多數情況下,切片被摻入化學物質形成P型襯底,在其上刻劃的邏輯電路要遵循nMOS電路的特性來設計,這種類型的晶體管空間利用率更高也更加節能。同時在多數情況下,必須盡量限制pMOS型晶體管的出現,因為在制造過程的后期,需要將N型材料植入P型襯底當中,這一過程會導致pMOS管的形成。

在摻入化學物質的工作完成之后,標準的切片就完成了。然后將每一個切片放入高溫爐中加熱,通過控制加溫時間使得切片表面生成一層二氧化硅膜。通過密切監測溫度,空氣成分和加溫時間,該二氧化硅層的厚度是可以控制的。準備工作的最后一道工序是在二氧化硅層上覆蓋一個感光層。這一層物質用于同一層中的其它控制應用。這層物質在干燥時具有很好的感光效果,而且在光刻蝕過程結束之后,能夠通過化學方法將其溶解并除去。光刻(Photolithography)

光刻是在晶圓上印制芯片電路圖形的工藝,是集成電路制造的最關鍵步驟,在整個芯片的制造過程中約占據了整體制造成本的35%。

光刻也是決定了集成電路按照摩爾定律發展的一個重要原因,如果沒有光刻技術的進步,集成電路就不可能從微米進入深亞微米再進入納米時代。

光刻工藝將掩膜圖形轉移到晶片表面的光刻膠上,首先光刻膠處理設備把光刻膠旋涂到晶圓表面,再經過分步重復曝光和顯影處理之后,在晶圓上形成需要的圖形。

通常以一個制程所需要經過掩膜數量來表示這個制程的難易。根據曝光方式不同,光刻可分為接觸式、接近式和投影式;根據光刻面數的不同,有單面對準光刻和雙面對準光刻;根據光刻膠類型不同,有薄膠光刻和厚膠光刻。一般的光刻流程包括前處理、勻膠、前烘、對準曝光、顯影、后烘,可以根據實際情況調整流程中的操作。

刻蝕(Etching)

在集成電路制造過程中,經過掩模套準、曝光和顯影,在抗蝕劑膜上復印出所需的圖形,或者用電子束直接描繪在抗蝕劑膜上產生圖形,然后把此圖形精確地轉移到抗蝕劑下面的介質薄膜(如氧化硅、氮化硅、多晶硅)或金屬薄膜上去,制造出所需的薄層圖案。

刻蝕就是用化學的、物理的或同時使用化學和物理的方法,有選擇地把沒有被抗蝕劑掩蔽的那一部分薄膜層除去,從而在薄膜上得到和抗蝕劑膜上完全一致的圖形。

等離子刻蝕(plasma etch)是在特定的條件下將反應氣體電離形成等離子體,等離子體選擇性地從晶圓上除去物質,剩下的物質在晶圓上形成芯片圖形。 離子注入 Ion Implantation

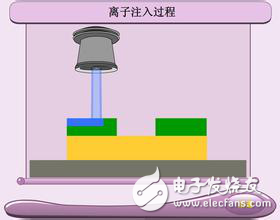

晶圓襯底是純硅材料,不導電或導電性極弱。為了在芯片內具有導電性,必須在晶圓里摻入微量的不純物質,通常是砷、硼、磷。摻雜可以在擴散爐中進行,也可以采用離子注入實現。一些先進的應用都是采用離子注入摻雜的。其實,最主要的目的是生成N溝道或P溝道。這個摻雜過程創建了全部的晶體管及彼此間的電路連接,沒個晶體管都有輸入端和輸出端,兩端之間被稱作端口。

離子注入有中電流離子注入、大電流/低能量離子注入、高能量離子注入三種,適于不同的應用需求。

化學機械研磨

化學機械研磨(化學機器磨光,CMP)兼具有研磨性物質的機械式研磨與酸堿溶液的化學式研磨兩種作用,可以使晶圓表面達到全面性的平坦化,以利后續薄膜沉積之進行。在CMP制程的硬設備中,研磨頭被用來將晶圓壓在研磨墊上并帶動晶圓旋轉,至于研磨墊則以相反的方向旋轉。在進行研磨時,由研磨顆粒所構成的研漿會被置于晶圓與研磨墊間。

一而再再而三從這一步起,將持續添加層級,加入一個二氧化硅層,然后光刻一次。重復這些步驟,然后就出現了一個多層立體架構,這就是你目前使用的處理器的萌芽狀態了。在每層之間采用金屬涂膜的技術進行層間的導電連接。

這就是芯片的內部結構,看著是不是很像一座大廈。晶圓度量檢測 Wafer Metrology在芯片制造過程中,為了保證晶圓按照預定的設計要求被加工必須進行大量的檢測和量測,包括芯片上線寬度的測量、各層厚度的測量、各層表面形貌測量,以及各個層的一些電子性能的測量。

隨著半導體工藝和制造技術的不斷發展,這些檢測已經成為提高量產和良率的不可缺少的部分。在銅互連工藝中,由于采用更精細的線寬技術和低k介電材料,需要開發更精密的測試設備和新的測試方法。

檢測主要包括三類:光學檢測、薄膜檢測、關鍵尺寸掃描電子檢測(CD-SEM)。晶圓檢測的一個重要發展趨勢是將多種測量方法融合于一個工藝設備中。

晶圓探針測試(Wafer Probe Test)這個檢測是用來判別芯片好壞的。晶圓探針測試是對制造完成的晶圓上的每個芯片(Die)進行針測,測試時,晶圓被固定在真空吸力的卡盤上,并與很薄的探針電測器對準,細如毛發的探針與芯片的每一個焊接點相接觸。在測試過程中,每一個芯片的電性能和電路機能都被檢測到,不合格的晶粒會被標上記號,而后當芯片切割成獨立的芯片顆粒時,標有記號的不合格芯片顆粒會被淘汰。探針檢測的相關數據,現在已經可以用來對晶圓制造中的良率提升提供幫助。

芯片封裝(Assembly & Packaging)

晶圓上的芯片在這里被切割成單個芯片,然后進行封裝,這樣才能使芯片最終安放在PCB板上。這里需要用的設備包括晶圓切割機,粘片機(將芯片封裝到引線框架中)、線焊機(負責將芯片和引線框架的連接,如金絲焊和銅絲焊)等。在引線鍵合工藝中使用不同類型的引線:金(Au)、鋁(Al)、銅(Cu),每一種材料都有其優點和缺點,通過不同的方法來鍵合。隨著多層封裝乃至3D封裝的應用的出現,超薄晶圓的需求也在不斷增強。芯片做好了,到了電工手里,經過熟練地焊接工藝,鑲嵌在PCB上,最終變成了電子產品的心臟。

-

半導體產業

+關注

關注

6文章

509瀏覽量

34299 -

IC設計

+關注

關注

37文章

1291瀏覽量

103758 -

半導體芯片

+關注

關注

60文章

915瀏覽量

70573

發布評論請先 登錄

相關推薦

開關電源PCB板設計的七步絕招

七步diy完成復古藍牙無繩電話

分析講解PCB制作七步流程

【轉】畫板經驗——七步教你輕松畫出完美PCB電路板

PCB抄板七步概述!

七步法則打造能落地的汽車體驗設計策略

5G下行速率低問題,七步法分析解決資料下載

七步入門深度神經網絡資料下載

芯片制造工藝真的很難嗎,七步走輕松搞定!

芯片制造工藝真的很難嗎,七步走輕松搞定!

評論