準備工作

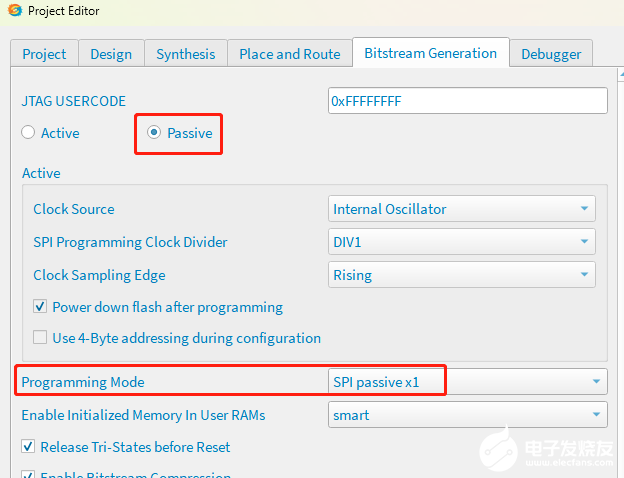

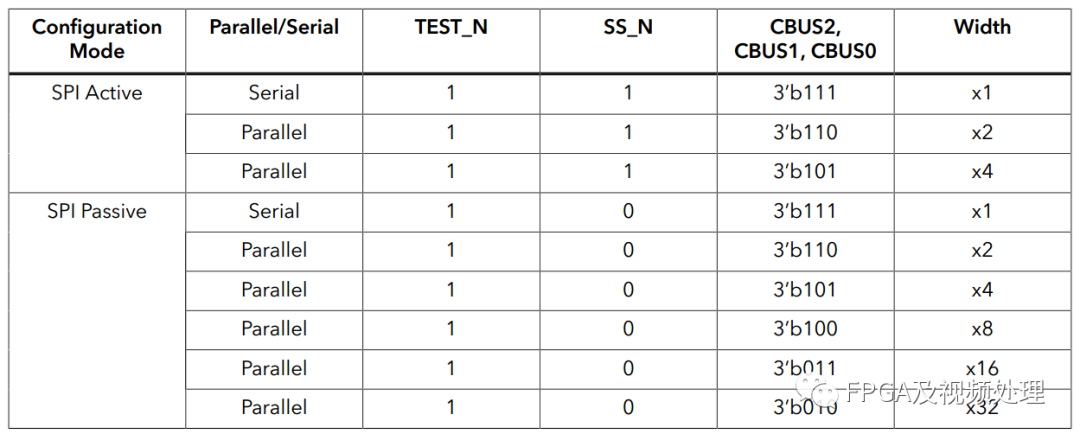

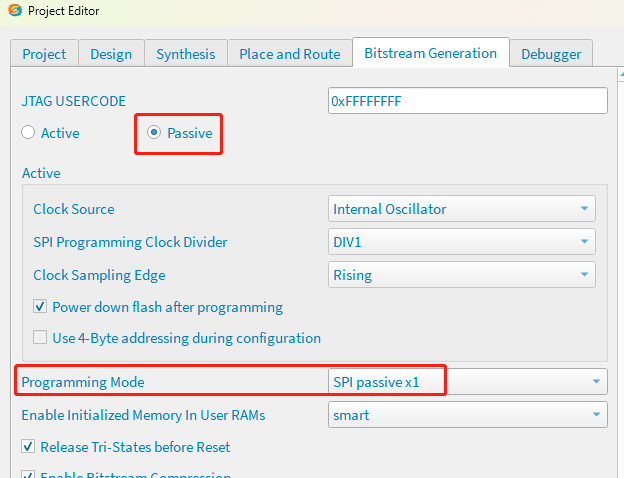

PS模式首先要把Bitstream Generation中的

(1)JTAG模式選擇為Passive

(2)根據PS的位寬選擇相應的Programming Mode.

(3)生成相應的下載文件。注意修改Bitstream生成模式時,不需要進行工程的全編譯,只需運行最后一步數據流生成即可。

PS配置啟動過程

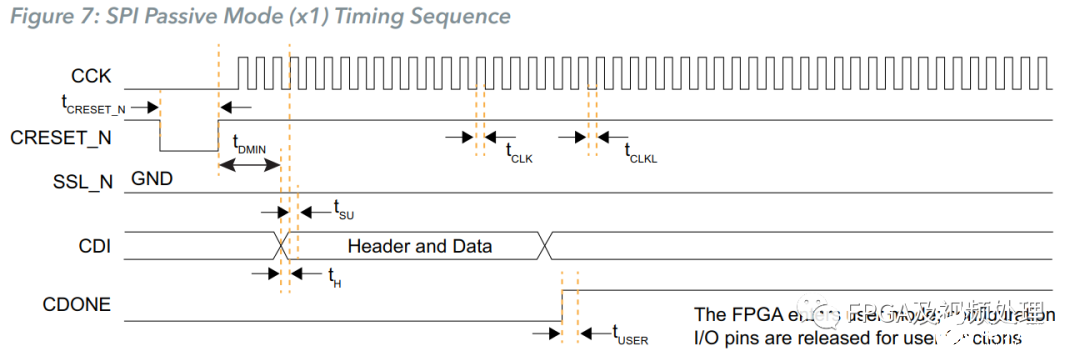

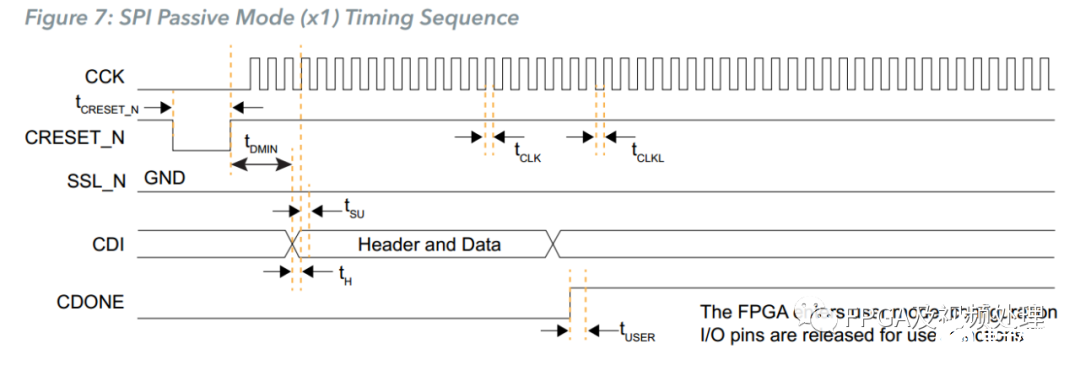

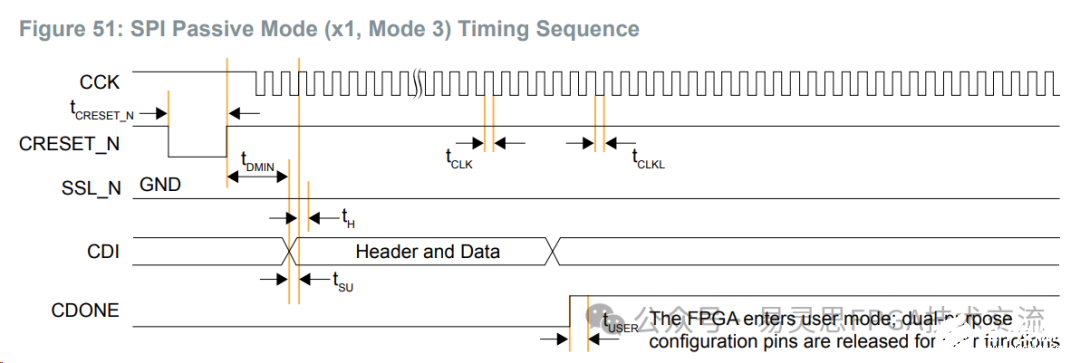

這里以X1模式為例,PS的配置過程如下:

(1)在啟動配置之前要先把CRESET_N拉低tCRESET_N,然后拉高;

(2)在CRESET_N拉高之后,要等待tDMIN,才可以發送同步碼,這期間可以翻轉CCK;下面就是同步碼。

(3)發送同步碼,數據與時鐘為上升沿觸發;要求外部處理器連續發送數據直到數據完成,發送每個字節中間要有等待時間;

(4)數據發送完成后,繼續發送CCK時鐘100周期,或者一邊發送一邊檢測CDONE,直到CDONE為高。實際上也確實有客戶因為沒有拉時鐘而啟動不了的情況。

控制信號處理

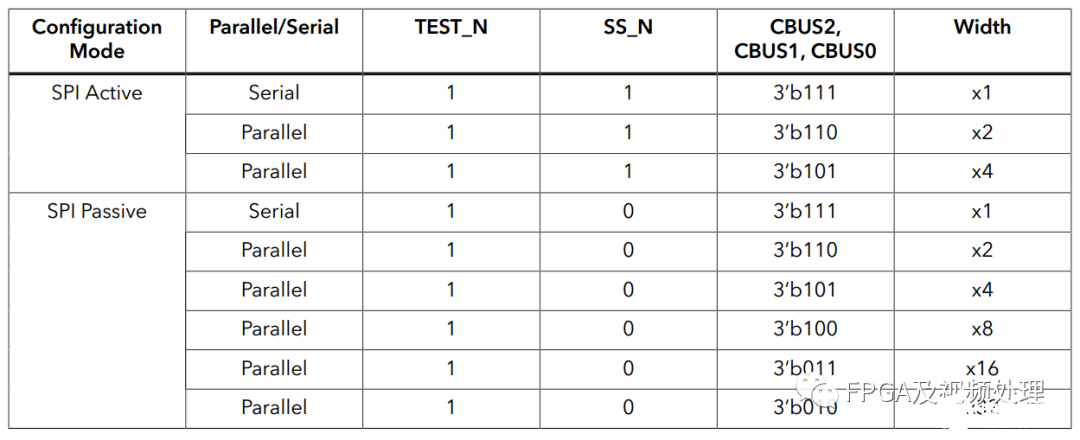

易靈思Trion FPGA的配置模塊主要由CBUS[2:0]、SS_N和TEST_N,CSI幾個信號控制。FPGA進入用戶模式前不要對這幾個信號進行翻轉。

目前易靈思的Programmer工具只支持PS x1模式,所以如果實在找不配置失敗的原因,可以通過邏輯分析儀來分析數據差異。x2和更高位寬需要通過外部微處理器,如MCU來操作。

這里需要注意的是在配置過程中,控制信號不要進行翻轉,目前看到的現象是在多次配置過程中,在連續兩次配置過程中,由于CSI翻轉造成第二次配置失敗。

應用案例

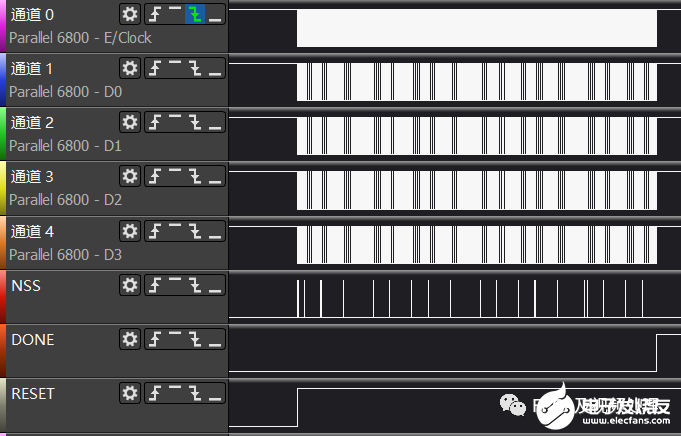

目前T20F169測試PS x4模式。時鐘為30MHz,tCRESET_N拉低790ns,tDMIN為2us,數據配置完成后又繼續發送時鐘100個以上。可以啟動。用時104ms

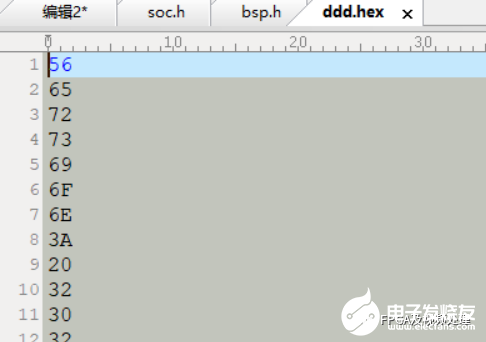

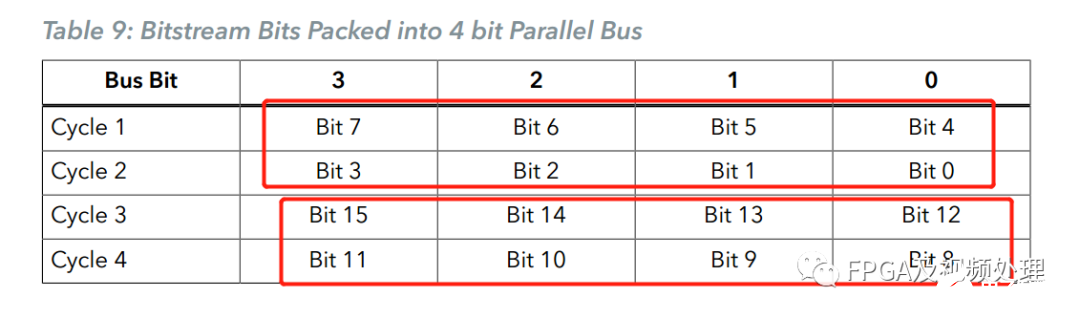

另外要提下數據順序問題,實際在發送過程是依次發送的。且第個字節從高位先發送。

整體配置過程波形如下,SS_N有時會有很多毛刺,時鐘之間也會有一些持續拉高的時間,但都不影響。

在發送數據每個字節間要加點延時。

Ti180注意事項

上電要求SPI為Mode3模式,也就是CCK上電要為高。其余注意事項請參考相關文檔。

審核編輯 黃宇

-

FPGA

+關注

關注

1620文章

21468瀏覽量

597911 -

易靈思

+關注

關注

5文章

41瀏覽量

4758

發布評論請先 登錄

相關推薦

易靈思(Elitestek)FPGA編程器功能特點及驅動安裝方法

易靈思Trion FPGA PS配置模式--update

三星電子和賽靈思宣布45nm Spartan-6 FPGA全

易靈思推Trion Titanium FPGA,采用 “Quantum? 計算架構”

FPGA JTAG的配置模式詳細說明

易靈思16nm FPGA助力汽車市場發展 天璣智慧監管解決方案亮相推進會

易靈思FPGA軟件更新的節奏,也許能磨出一個好產品

易靈思RAM使用--Update3

易靈思Trion FPGA PS配置模式--update(6)

易靈思Trion FPGA PS配置模式--update(6)

評論