JK觸發器是一種二進制觸發器,它在數字電路中具有廣泛的應用。了解JK觸發器的上升沿和下降沿對于設計和分析數字電路至關重要。

1. 引言

在數字電路中,觸發器是存儲一位二進制信息的基本單元。JK觸發器是一種具有兩個穩定狀態的觸發器,它可以通過輸入信號的變化來改變其輸出狀態。JK觸發器的特點是具有兩個輸入端,分別標記為J和K,以及一個輸出端,標記為Q。JK觸發器的工作原理和特性使其在各種數字電路設計中非常實用。

2. JK觸發器的工作原理

JK觸發器的基本工作原理是通過輸入信號J和K的變化來改變其輸出Q的狀態。JK觸發器的邏輯功能如下:

- 當J=1且K=0時,輸出Q將被置為1。

- 當J=0且K=1時,輸出Q將被置為0。

- 當J=1且K=1時,輸出Q的值將翻轉(即從0變為1,或從1變為0)。

- 當J=0且K=0時,輸出Q保持不變。

3. JK觸發器的電路實現

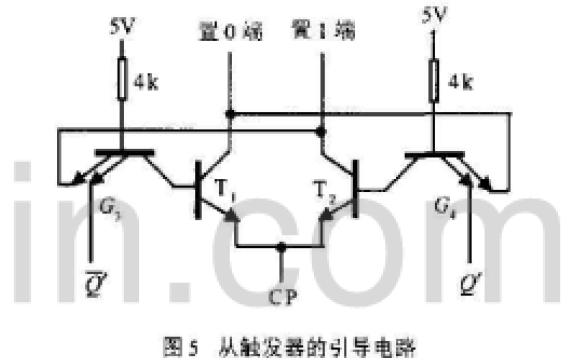

JK觸發器可以通過多種方式實現,包括使用邏輯門、雙穩態電路等。以下是使用邏輯門實現的JK觸發器電路:

- 使用兩個NAND門和兩個反相器(NOT門)可以實現JK觸發器。其中,NAND門的輸出連接到反相器的輸入,反相器的輸出再連接到NAND門的輸入,形成一個反饋回路。

4. JK觸發器的特性

JK觸發器具有以下特性:

- 雙穩態:JK觸發器有兩個穩定狀態,即輸出Q為0或1。

- 邊沿觸發:JK觸發器的輸出狀態在輸入信號的上升沿或下降沿發生變化。

- 透明窗口:在某些條件下,JK觸發器的輸出可以直接反映輸入信號的狀態,這被稱為透明窗口。

5. 判斷上升沿和下降沿

在數字電路中,上升沿和下降沿是描述信號變化的術語。上升沿是指信號從低電平變為高電平的瞬間,而下降沿是指信號從高電平變為低電平的瞬間。對于JK觸發器來說,上升沿和下降沿的判斷至關重要,因為它們決定了觸發器的輸出狀態。

5.1 上升沿

上升沿是指輸入信號從0變為1的瞬間。對于JK觸發器來說,上升沿的判斷可以通過以下步驟進行:

- 觀察輸入信號J和K的變化。

- 當J從0變為1時,觸發器的輸出Q將被置為1。

- 當K從0變為1時,觸發器的輸出Q將被置為0。

- 當J和K同時從0變為1時,觸發器的輸出Q將翻轉。

5.2 下降沿

下降沿是指輸入信號從1變為0的瞬間。對于JK觸發器來說,下降沿的判斷可以通過以下步驟進行:

- 觀察輸入信號J和K的變化。

- 當J從1變為0時,觸發器的輸出Q保持不變。

- 當K從1變為0時,觸發器的輸出Q保持不變。

- 當J和K同時從1變為0時,觸發器的輸出Q保持不變。

6. JK觸發器的應用

JK觸發器在數字電路設計中具有廣泛的應用,包括:

- 寄存器:用于存儲數據。

- 計數器:用于實現數字計數功能。

- 移位寄存器:用于實現數據的串行傳輸。

- 同步電路:用于實現數據的同步傳輸。

7. JK觸發器的優缺點

7.1 優點

- 靈活性:JK觸發器可以通過不同的輸入信號組合實現多種邏輯功能。

- 簡單性:JK觸發器的電路實現相對簡單,易于設計和分析。

- 穩定性:JK觸發器具有雙穩態特性,使其在數字電路中具有較高的穩定性。

7.2 缺點

- 復雜性:在某些情況下,JK觸發器的邏輯功能可能較為復雜,需要仔細設計和分析。

- 透明窗口:在某些條件下,JK觸發器的輸出可能會直接反映輸入信號的狀態,這可能會影響電路的性能。

-

JK觸發器

+關注

關注

1文章

43瀏覽量

15875 -

數字電路

+關注

關注

193文章

1600瀏覽量

80497 -

雙穩態電路

+關注

關注

1文章

29瀏覽量

14957 -

輸入信號

+關注

關注

0文章

446瀏覽量

12536

發布評論請先 登錄

相關推薦

具有置位和復位功能的雙 JK 觸發器;上升沿觸發-74HC_HCT109_Q100

jk觸發器上升沿和下降沿怎么判斷

jk觸發器上升沿和下降沿怎么判斷

評論