鎖存器電路概述

定義與功能

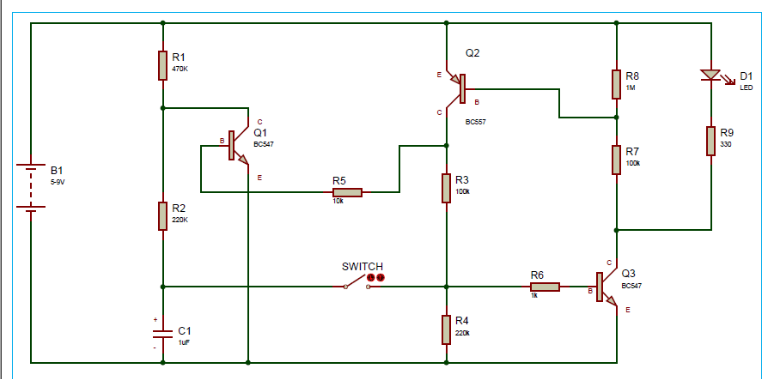

鎖存器(Latch)是數(shù)字電路中的一種基本存儲元件,用于存儲一個位(1或0)的狀態(tài)。它能夠在特定輸入脈沖電平作用下改變狀態(tài),并保持該狀態(tài)直到下一個脈沖電平到來。鎖存器的主要作用是緩存數(shù)據(jù),解決高速控制器與慢速外設之間的不同步問題,以及解決驅動和I/O口的輸入輸出問題。

類型

鎖存器有多種類型,包括RS鎖存器、D鎖存器、JK鎖存器和T鎖存器等。每種類型都有其特定的輸入/輸出特性和應用場景。

中間元件詳解

在鎖存器電路中,中間元件通常指的是構成鎖存器核心功能的電路組件,這些組件共同協(xié)作以實現(xiàn)數(shù)據(jù)的鎖存和保持。

1. 基本雙穩(wěn)態(tài)電路

構成 :雙穩(wěn)態(tài)電路是鎖存器的基礎,通常由兩個首尾相接的非門(或反相器)構成交叉耦合結構。這種結構能夠產(chǎn)生兩個穩(wěn)定的狀態(tài),分別代表二進制的0和1。

工作原理 :當Q=0時,經(jīng)非門反相后Q'=1,Q'反饋到另一非門的輸入端,保證Q=0。反之亦然,形成兩個互補的穩(wěn)定狀態(tài)。

中間元件 :非門(反相器)是構成雙穩(wěn)態(tài)電路的中間元件,它們通過互相反饋維持電路的穩(wěn)定狀態(tài)。

2. RS鎖存器

構成 :RS鎖存器由兩個與非門(NOR)構成,具有兩個輸入端S(置位)和R(復位)以及兩個輸出端Q和Q'。

工作原理 :

- 當S=1, R=0時,Q=1, Q'=0(置位狀態(tài))。

- 當S=0, R=1時,Q=0, Q'=1(復位狀態(tài))。

- 當S=R=0時,鎖存器保持原狀態(tài)。

- 當S=R=1時,鎖存器進入不穩(wěn)定狀態(tài),應避免此情況。

中間元件 :與非門是RS鎖存器的核心元件,它們通過邏輯運算控制輸出狀態(tài)。

3. D鎖存器

構成 :D鎖存器是RS鎖存器的簡化版本,只有一個輸入端D和一個時鐘信號控制端。

工作原理 :在時鐘信號的有效邊沿(如上升沿或下降沿),D鎖存器將輸入D的狀態(tài)鎖存到輸出Q。

中間元件 :除了基本的雙穩(wěn)態(tài)電路元件外,D鎖存器還包括時鐘控制邏輯,用于在特定時刻捕獲輸入信號。

4. JK鎖存器與T鎖存器

構成與工作原理 :

- JK鎖存器 :具有J、K輸入端和時鐘信號控制端。根據(jù)J、K的值和時鐘信號的變化,JK鎖存器可以實現(xiàn)置位、復位、保持和翻轉功能。

- T鎖存器 :是JK鎖存器的特例,只有一個輸入端T。當T=1時,輸出Q翻轉;當T=0時,輸出Q保持不變。

中間元件 :JK鎖存器和T鎖存器中的中間元件包括邏輯門(如與非門、或門等)和時鐘控制邏輯,它們共同實現(xiàn)復雜的邏輯功能。

電路設計與應用

電路設計 :

- 鎖存器的設計需要考慮輸入/輸出特性、時序要求、功耗和穩(wěn)定性等因素。

- 在實際應用中,鎖存器通常與其他邏輯元件(如觸發(fā)器、寄存器等)組合使用,以構建更復雜的電路系統(tǒng)。

應用場景 :

-

電路

+關注

關注

172文章

5846瀏覽量

171904 -

控制器

+關注

關注

112文章

16198瀏覽量

177398 -

元件

+關注

關注

4文章

888瀏覽量

36654 -

鎖存器

+關注

關注

8文章

904瀏覽量

41444

發(fā)布評論請先 登錄

相關推薦

鎖存器電路中的中間是什么元件

鎖存器電路中的中間是什么元件

評論