MOSFET(金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管)是現(xiàn)代電子學(xué)中極為重要的器件之一,廣泛應(yīng)用于集成電路、電源管理、信號(hào)處理等多個(gè)領(lǐng)域。其核心特性之一便是其閾值電壓(Threshold Voltage, 通常表示為V th ),這一參數(shù)直接決定了MOSFET的開(kāi)關(guān)行為和工作模式。下面,我們將深入探討MOSFET閾值電壓的概念、影響因素,并嘗試在有限的篇幅內(nèi)盡可能詳盡地闡述這些內(nèi)容。

一、MOSFET閾值電壓的定義

MOSFET的閾值電壓是指使MOSFET從截止?fàn)顟B(tài)(即溝道不導(dǎo)電)轉(zhuǎn)變?yōu)閷?dǎo)通狀態(tài)(即溝道開(kāi)始導(dǎo)電)所需的最小柵極-源極電壓(VGS)。在這個(gè)電壓點(diǎn),溝道中的載流子濃度足夠高,以至于能夠形成連續(xù)的導(dǎo)電通道,允許電流在源極和漏極之間流動(dòng)。閾值電壓是MOSFET的關(guān)鍵參數(shù)之一,它不僅決定了器件的開(kāi)關(guān)特性,還影響著電路的整體性能、功耗和穩(wěn)定性。

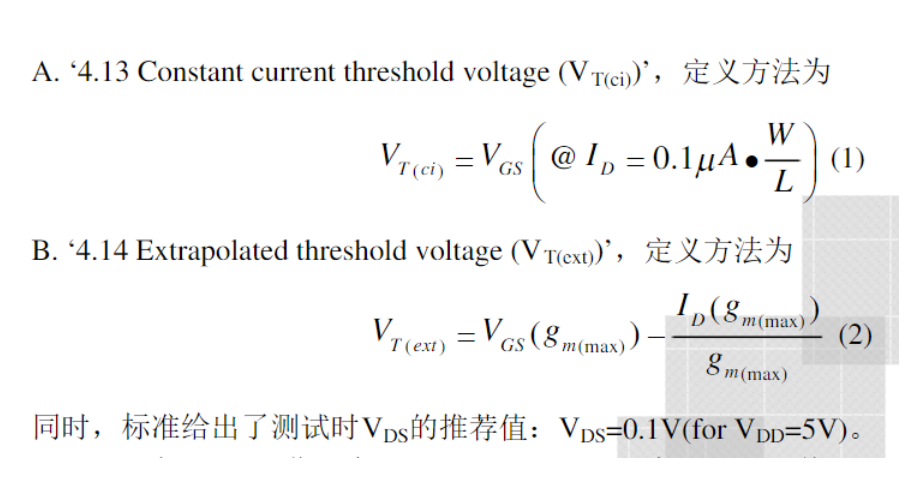

二、MOSFET閾值電壓測(cè)試方法

對(duì)于功率MOSFET,通常在250uA的漏源電流下測(cè)量。Vth主要取決于柵極氧化層厚度和溝道摻雜濃度。

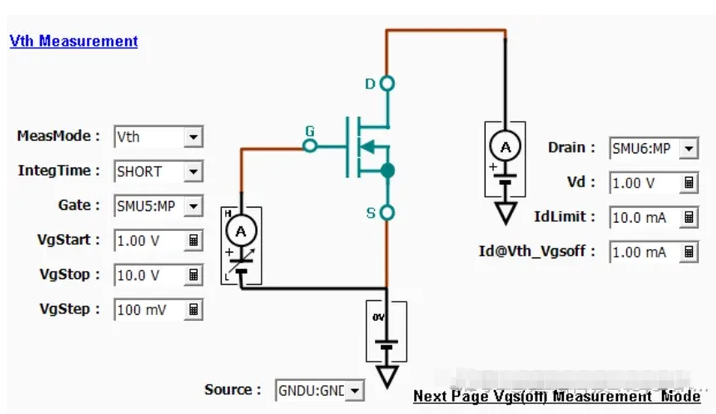

不同的廠家定義Vth參數(shù)的測(cè)試條件略有不同,有的廠家會(huì)固定漏極電壓,掃描柵源電壓,當(dāng)漏極電流達(dá)到某一值時(shí)提取Vth。針對(duì)這種測(cè)試可以使用easyexpert軟件中application test下已經(jīng)內(nèi)置的測(cè)試案例完成。

但是有的客戶需要同時(shí)對(duì)VGS和VDS進(jìn)行sweep,相當(dāng)于VGS=VDS,然后觀察特定Id下的vth的值,這也是非常簡(jiǎn)單,只需要在上面的應(yīng)用中將測(cè)試模式改為Vgsoff就可以了。

對(duì)于小功率mosfet,提取Vth的方法是采用最大跨導(dǎo)法,也可以直接調(diào)用easyexpert軟件中CMOS案例下的VthgmMax應(yīng)用來(lái)測(cè)試。

三、影響MOSFET閾值電壓的因素

MOSFET的閾值電壓受多種因素的共同影響,這些因素大致可以分為工藝參數(shù)、物理效應(yīng)和外部環(huán)境三大類。

1. 工藝參數(shù)

(1)溝道摻雜濃度

- 溝道區(qū)的摻雜濃度直接影響閾值電壓。在N型MOSFET中,溝道區(qū)為P型摻雜,若摻雜濃度增加,意味著需要更高的柵極電壓來(lái)耗盡溝道中的空穴并吸引電子形成導(dǎo)電溝道,因此閾值電壓會(huì)上升。反之,對(duì)于P型MOSFET,溝道區(qū)為N型摻雜,摻雜濃度增加會(huì)導(dǎo)致閾值電壓下降。

(2)柵氧化層厚度

- 柵氧化層(即絕緣層)的厚度是影響閾值電壓的另一重要因素。較厚的柵氧化層需要更高的柵極電壓才能在溝道中產(chǎn)生足夠的電場(chǎng)以吸引或排斥載流子,因此閾值電壓會(huì)增大。隨著半導(dǎo)體工藝技術(shù)的進(jìn)步,柵氧化層厚度不斷減小,這有助于降低閾值電壓并提高器件性能。

(3)柵極材料與工作函數(shù)

- 柵極材料的功函數(shù)(即電子從金屬轉(zhuǎn)移到半導(dǎo)體所需的最小能量)也會(huì)影響閾值電壓。功函數(shù)差異較大的柵極和溝道材料組合需要更高的柵極電壓來(lái)克服能壘,形成導(dǎo)電溝道,因此會(huì)導(dǎo)致閾值電壓的變化。

(4)制造工藝中的應(yīng)力

- 制造過(guò)程中的機(jī)械或熱應(yīng)力可能會(huì)影響晶體管的晶格結(jié)構(gòu)和材料特性,進(jìn)而改變閾值電壓。例如,溝道區(qū)的應(yīng)變可能會(huì)改變載流子的有效質(zhì)量和遷移率,從而影響閾值電壓。

2. 物理效應(yīng)

(1)短溝道效應(yīng)

- 隨著MOSFET尺寸的縮小,特別是溝道長(zhǎng)度的縮短,短溝道效應(yīng)變得顯著。這種效應(yīng)包括直接隧穿、熱載流子注入等,它們會(huì)改變溝道中的電荷分布和電場(chǎng)分布,進(jìn)而影響閾值電壓。短溝道效應(yīng)通常導(dǎo)致閾值電壓的降低和亞閾值擺幅的增大。

(2)量子效應(yīng)

- 在極小的MOSFET結(jié)構(gòu)中,量子效應(yīng)開(kāi)始顯現(xiàn),如量子隧穿、量子化能級(jí)等。這些效應(yīng)會(huì)改變載流子的輸運(yùn)特性,影響閾值電壓的精確計(jì)算和控制。

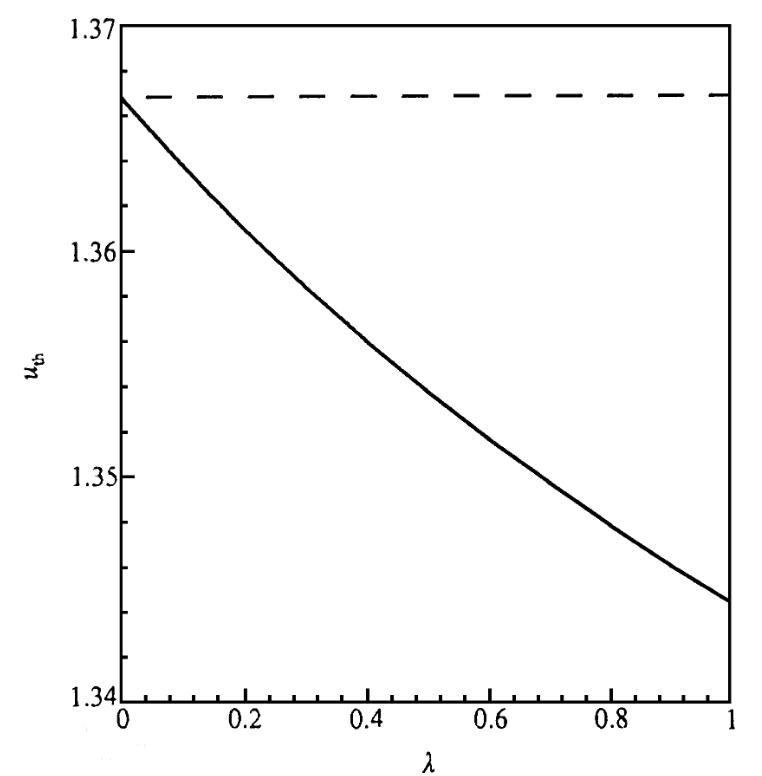

(3)體效應(yīng)(也稱背柵效應(yīng))

- 體效應(yīng)是指源極、漏極和體(或襯底)之間的相互作用對(duì)閾值電壓的影響。當(dāng)體電位改變時(shí),溝道中的電荷分布會(huì)發(fā)生變化,從而影響閾值電壓。這種效應(yīng)在SOI(絕緣體上硅)MOSFET中尤為顯著。

3. 外部環(huán)境

(1)溫度

- 溫度是影響MOSFET性能的重要外部環(huán)境因素之一。隨著溫度的升高,半導(dǎo)體材料的禁帶寬度減小,載流子濃度增加,遷移率變化,這些因素共同作用于閾值電壓。一般來(lái)說(shuō),溫度升高會(huì)導(dǎo)致閾值電壓降低,但具體變化還受其他因素如摻雜濃度、氧化層質(zhì)量等的影響。

(2)輻射

- 輻射(如X射線、γ射線、中子輻射等)會(huì)對(duì)半導(dǎo)體材料造成損傷,改變其電學(xué)特性,包括閾值電壓。輻射誘導(dǎo)的缺陷和陷阱會(huì)捕獲載流子,影響溝道中的電荷分布和電場(chǎng)分布,從而導(dǎo)致閾值電壓的偏移。

(3)電源電壓

- 電源電壓(VDD)雖然不直接改變MOSFET的閾值電壓,但它通過(guò)影響MOSFET的工作狀態(tài)間接地對(duì)閾值電壓的感知產(chǎn)生影響。在數(shù)字電路中,當(dāng)電源電壓降低時(shí),為了保證邏輯電平的正確識(shí)別,MOSFET的閾值電壓相對(duì)于電源電壓的比例變得更為重要。此外,低電源電壓工作(如低功耗設(shè)計(jì))通常要求MOSFET具有較低的閾值電壓以減少靜態(tài)功耗。

(4)機(jī)械應(yīng)力

- 在某些應(yīng)用場(chǎng)景中,如柔性電子或可穿戴設(shè)備,MOSFET可能會(huì)受到機(jī)械應(yīng)力的影響。這些應(yīng)力可能導(dǎo)致晶體結(jié)構(gòu)的變化,從而影響載流子的遷移率和溝道電阻,間接影響閾值電壓。因此,在設(shè)計(jì)這些特殊應(yīng)用時(shí),需要特別考慮材料的機(jī)械穩(wěn)定性和應(yīng)力對(duì)閾值電壓的影響。

4. 設(shè)計(jì)與優(yōu)化

為了獲得理想的閾值電壓,設(shè)計(jì)者和工程師需要在多個(gè)方面進(jìn)行優(yōu)化:

- 精確控制摻雜濃度和分布 :通過(guò)精確的摻雜工藝控制溝道區(qū)的摻雜濃度和分布,可以精確調(diào)整閾值電壓。

- 優(yōu)化柵氧化層 :采用高質(zhì)量的柵氧化層材料和工藝,以減小厚度并降低泄漏電流,同時(shí)保持穩(wěn)定的閾值電壓。

- 考慮短溝道效應(yīng) :在先進(jìn)工藝節(jié)點(diǎn)下,需要采用特殊的設(shè)計(jì)技術(shù)(如多柵結(jié)構(gòu)、應(yīng)變工程等)來(lái)減輕短溝道效應(yīng)對(duì)閾值電壓的影響。

- 環(huán)境適應(yīng)性設(shè)計(jì) :針對(duì)特定的應(yīng)用環(huán)境(如高溫、輻射環(huán)境),設(shè)計(jì)具有更好環(huán)境適應(yīng)性的MOSFET結(jié)構(gòu),以減少外部環(huán)境對(duì)閾值電壓的干擾。

5. 未來(lái)發(fā)展趨勢(shì)

隨著半導(dǎo)體技術(shù)的不斷進(jìn)步,MOSFET的閾值電壓控制將變得更加精確和靈活。以下是一些未來(lái)可能的發(fā)展趨勢(shì):

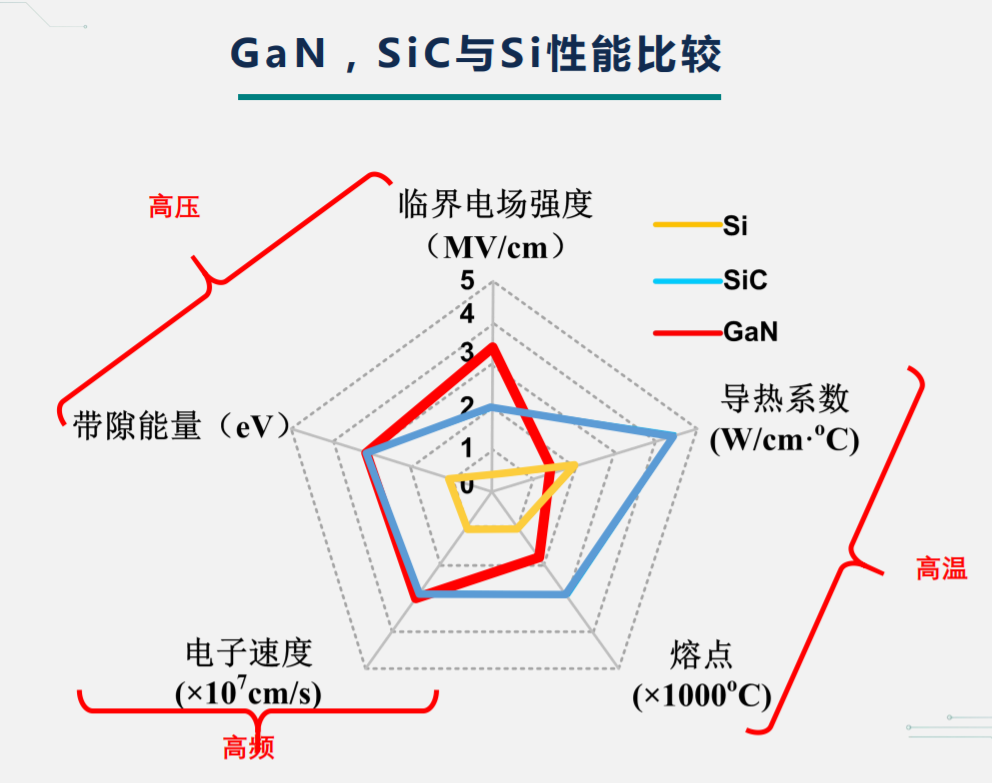

- 新材料的應(yīng)用 :新型材料(如二維材料、高遷移率溝道材料)的引入可能帶來(lái)更低的閾值電壓和更高的性能。

- 三維集成技術(shù) :三維集成技術(shù)(如TSV)可能通過(guò)改變器件之間的互連方式,進(jìn)一步降低功耗并提高性能,從而對(duì)閾值電壓的優(yōu)化提出新的要求。

- 自適應(yīng)閾值電壓技術(shù) :隨著智能電路和系統(tǒng)的發(fā)展,自適應(yīng)閾值電壓技術(shù)可能成為未來(lái)的研究方向。這種技術(shù)可以根據(jù)電路的工作狀態(tài)和外部環(huán)境自動(dòng)調(diào)整閾值電壓,以實(shí)現(xiàn)更低的功耗和更高的性能。

總之,MOSFET的閾值電壓是一個(gè)復(fù)雜而重要的參數(shù),它受到多種因素的共同影響。通過(guò)精確控制工藝參數(shù)、優(yōu)化物理設(shè)計(jì)以及考慮外部環(huán)境因素,可以實(shí)現(xiàn)對(duì)閾值電壓的精確控制和優(yōu)化。隨著半導(dǎo)體技術(shù)的不斷發(fā)展,我們有理由相信未來(lái)的MOSFET將具有更低的閾值電壓、更高的性能和更好的環(huán)境適應(yīng)性。這將為電子設(shè)備的性能提升、功耗降低以及新應(yīng)用的開(kāi)發(fā)提供強(qiáng)有力的支持。

-

MOSFET

+關(guān)注

關(guān)注

142文章

6937瀏覽量

211760 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

26326瀏覽量

210100 -

晶體管

+關(guān)注

關(guān)注

77文章

9505瀏覽量

136956

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

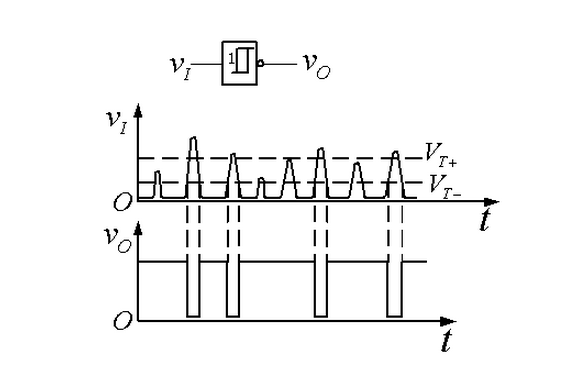

解答74HC14中正向閾值電壓和負(fù)向閾值電壓是什么/電壓為多少

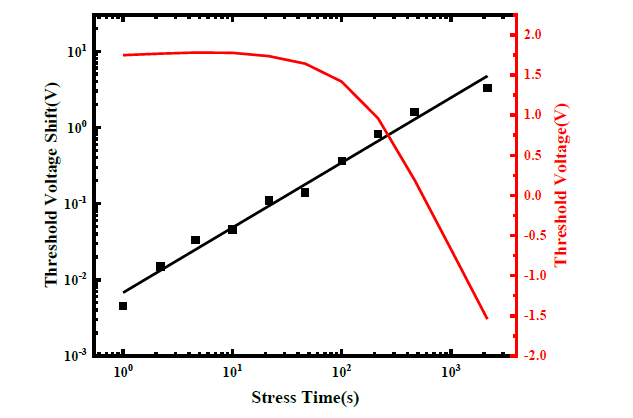

碳化硅的閾值電壓穩(wěn)定性

MOS管閾值電壓的問(wèn)題

MOSFET的重要特性–柵極閾值電壓

閾值電壓的計(jì)算

MOS管閾值電壓與溝長(zhǎng)和溝寬的關(guān)系

EDA探索之控制閾值電壓

控制閾值電壓

NMOS晶體管的閾值電壓公式 nmos晶體管的閾值電壓與哪些因素有關(guān)

不同Vt cell工藝是怎么實(shí)現(xiàn)的?閾值電壓和哪些因素有關(guān)系?

影響第三代半導(dǎo)體SiC MOS閾值電壓不穩(wěn)定的因素有哪些?如何應(yīng)對(duì)?

MOSFET閾值電壓是什么?影響MOSFET閾值電壓的因素有哪些?

MOSFET閾值電壓是什么?影響MOSFET閾值電壓的因素有哪些?

評(píng)論