在高速模擬信號鏈設(shè)計(jì)中,印刷電路板(PCB)布局布線需要考慮許多選項(xiàng),有些選項(xiàng)比其它選項(xiàng)更重要,有些選項(xiàng)則取決于應(yīng)用。最終的答案各不相同,但在所有情況下,設(shè)計(jì)工程師都應(yīng)盡量消除最佳做法的誤差,而不要過分計(jì)較布局布線的每一個(gè)細(xì)節(jié)。

裸露焊盤

裸露焊盤(EPAD)有時(shí)會被忽視,但它對充分發(fā)揮信號鏈的性能以及器件充分散熱非常重要。

裸露焊盤,ADI公司稱之為引腳0,是目前大多數(shù)器件下方的焊盤。它是一個(gè)重要的連接,芯片的所有內(nèi)部接地都是通過它連接到器件下方的中心點(diǎn)。不知您是否注意到,目前許多轉(zhuǎn)換器和放大器中缺少接地引腳,原因就在于裸露焊盤。

關(guān)鍵是將此引腳妥善固定(即焊接)至PCB,實(shí)現(xiàn)牢靠的電氣和熱連接。如果此連接不牢固,就會發(fā)生混亂,換言之,設(shè)計(jì)可能無效。

實(shí)現(xiàn)最佳連接

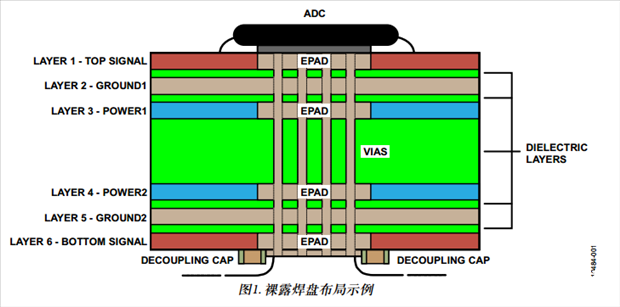

利用裸露焊盤實(shí)現(xiàn)最佳電氣和熱連接有三個(gè)步驟。首先,在可能的情況下,應(yīng)在各PCB層上復(fù)制裸露焊盤,這樣做的目的是為了與所有接地和接地層形成密集的熱連接,從而快速散熱。此步驟與高功耗器件及具有高通道數(shù)的應(yīng)用相關(guān)。在電氣方面,這將為所有接地層提供良好的等電位連接。

甚至可以在底層復(fù)制裸露焊盤(見圖1),它可以用作去耦散熱接地點(diǎn)和安裝底側(cè)散熱器的地方。

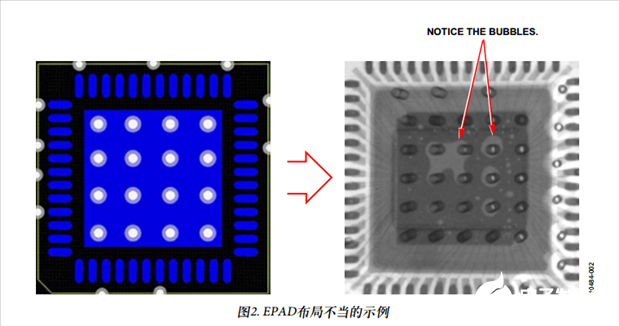

其次,將裸露焊盤分割成多個(gè)相同的部分,如同棋盤。在打開的裸露焊盤上使用絲網(wǎng)交叉格柵,或使用阻焊層。此步驟可以確保器件與PCB之間的穩(wěn)固連接。在回流焊組裝過程中,無法決定焊膏如何流動并最終連接器件與PCB。

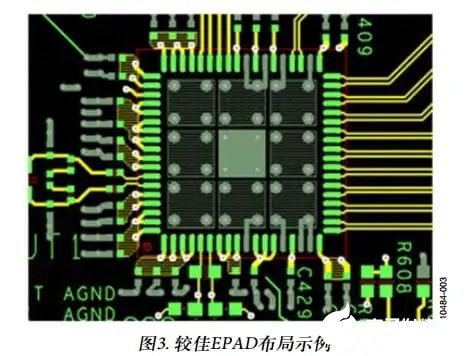

連接可能存在,但分布不均。可能只得到一個(gè)連接,并且連接很小,或者更糟糕,位于拐角處。將裸露焊盤分割為較小的部分可以確保各個(gè)區(qū)域都有一個(gè)連接點(diǎn),實(shí)現(xiàn)更牢靠、均勻連接的裸露焊盤(見圖2和圖3)。

最后,應(yīng)當(dāng)確保各部分都有過孔連接到地。各區(qū)域通常都很大,足以放置多個(gè)過孔。組裝之前,務(wù)必用焊膏或環(huán)氧樹脂填充每個(gè)過孔,這一步非常重要,可以確保裸露焊盤焊膏不會回流到這些過孔空洞中,影響正確連接。最后,應(yīng)當(dāng)確保各部分都有過孔連接到地。各區(qū)域通常都很大,足以放置多個(gè)過孔。組裝之前,務(wù)必用焊膏或環(huán)氧樹脂填充每個(gè)過孔,這一步非常重要,可以確保裸露焊盤焊膏不會回流到這些過孔空洞中,影響正確連接。

去耦和層電容

有時(shí)工程師會忽略使用去耦的目的,僅僅在電路板上分散大小不同的許多電容,使較低阻抗電源連接到地。但問題依舊:需要多少電容?許多相關(guān)文獻(xiàn)表明,必須使用大小不同的許多電容來降低功率傳輸系統(tǒng)(PDS)的阻抗,但這并不完全正確。相反,僅需選擇正確大小和正確種類的電容就能降低PDS阻抗。

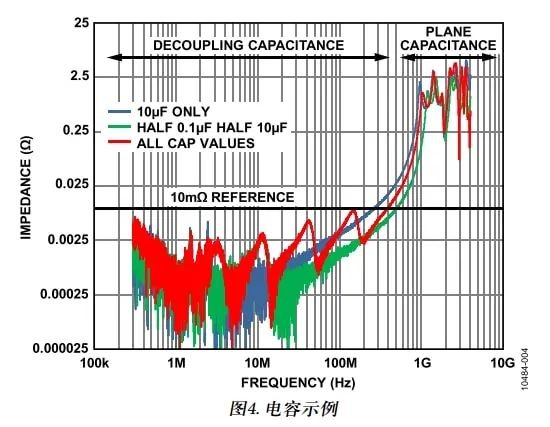

例如,考慮設(shè)計(jì)一個(gè)10 mΩ參考層,如圖4所示。如紅色曲線所示,系統(tǒng)電路板上使用許多不同值的電容,0.001 μF、0.01 μF、0.1 μF等等。這當(dāng)然可以降低500 MHz頻率范圍內(nèi)的阻抗,但是,請看綠色曲線,同樣的設(shè)計(jì)僅使用0.1 μF和10 μF 電容。這證明,如果使用正確的電容,則不需要如此多的電容。這也有助于節(jié)省空間和物料(BOM)成本。

注意,并非所有電容“生而平等”,即使同一供應(yīng)商,工藝、尺寸和樣式也有差別。如果未使用正確的電容,不論是多個(gè)電容還是幾個(gè)不同類型,都會給PDS帶來反作用。

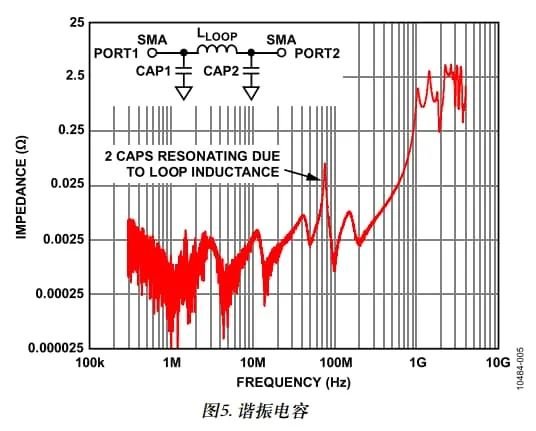

結(jié)果可能是形成電感環(huán)路。電容放置不當(dāng)或者使用不同工藝和型號的電容(因而對系統(tǒng)內(nèi)的頻率做出不同響應(yīng)),彼此之間可能會發(fā)生諧振(見圖5)。

了解系統(tǒng)所用電容類型的頻率響應(yīng)很重要。隨便選用電容,會讓設(shè)計(jì)低阻抗PDS系統(tǒng)的努力付之東流。

PDS的高頻層電容

要設(shè)計(jì)出合格的PDS,需要使用各種電容(見圖4)。PCB上使用的典型電容值只能將直流或接近直流頻率至約500 MHz范圍的阻抗降低。高于500 MHz頻率時(shí),電容取決于PCB形成的內(nèi)部電容。注意,電源層和接地層緊密疊置會有幫助。

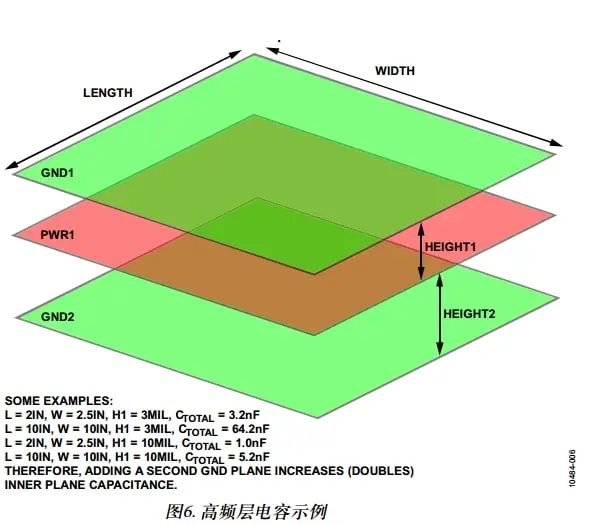

應(yīng)當(dāng)設(shè)計(jì)一個(gè)支持較大層電容的PCB層疊結(jié)構(gòu)。例如,六層堆疊可能包含頂部信號層、第一接地層、第一電源層、第二電源層、第二接地層和底部信號層。規(guī)定第一接地層和第一電源層在層疊結(jié)構(gòu)中彼此靠近,這兩層間距為2到4密爾,形成一個(gè)固有高頻層電容。此電容的最大優(yōu)點(diǎn)是它是免費(fèi)的,只需在PCB制造筆記中注明。如果必須分割電源層,同一層上有多個(gè)VDD電源軌,則應(yīng)使用盡可能大的電源層。不要留下空洞,同時(shí)應(yīng)注意敏感電路。這將使該VDD層的電容最大。

如果設(shè)計(jì)允許存在額外的層(上例中,從六層變?yōu)榘藢?,則應(yīng)將兩個(gè)額外的接地層放在第一和第二電源層之間。在核心間距同樣為2到3密爾的情況下,此時(shí)層疊結(jié)構(gòu)的固有電容將加倍(示例見圖6)。

與添加更多分立高頻電容以在高頻時(shí)保持低阻抗相比,此結(jié)構(gòu)更易于設(shè)計(jì)。

PDS的任務(wù)是將響應(yīng)電源電流需求而產(chǎn)生的電壓紋波降至最低,這點(diǎn)很重要但常被忽略。所有電路都需要電流,有些電路需求量較大,有些電路則需要以較快的速率提供電流。采用充分去耦的低阻抗電源層或接地層以及良好的 PCB層疊,有助于將因電路的電流需求而產(chǎn)生的電壓紋波降至最低。例如,根據(jù)所用的去耦策略,如果系統(tǒng)設(shè)計(jì)的開關(guān)電流為1 A,PDS的阻抗為10 mΩ,則最大電壓紋波為 10 mV。計(jì)算很簡單:V = IR。

憑借完美的PCB堆疊,可覆蓋高頻范圍,同時(shí)在電源層起始入口點(diǎn)和高功率或浪涌電流器件周圍使用傳統(tǒng)去耦,可覆蓋低頻范圍(<500 MHz)。這可確保PDS阻抗在整個(gè)頻率范圍??內(nèi)均最低。沒有必要各處都配置電容;電容正對著每個(gè)IC ?放置會破壞許多制造規(guī)則。如果需要這種嚴(yán)厲的措施,則??說明電路存在其它問題。

層耦合

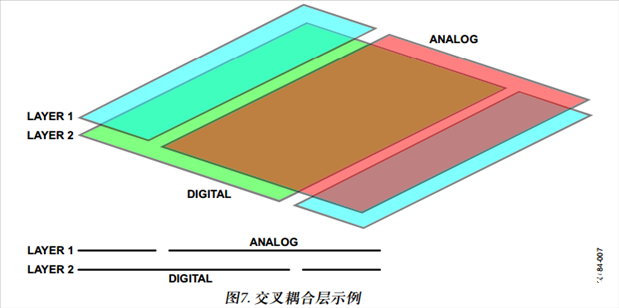

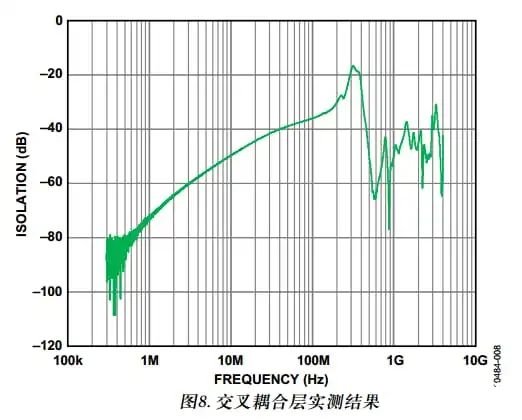

一些布局不可避免地具有重疊電路層(見圖8)。有些情況下,可能是敏感模擬層(例如電源、接地或信號),下方的一層是高噪聲數(shù)字層。

這常常被忽略,因?yàn)楦咴肼晫邮窃诹硪粚印诿舾械哪M層下方。然而,一個(gè)簡單的實(shí)驗(yàn)就可以證明事實(shí)并非如此。以某一層面為例,在任一層注入信號。接著連接另一層,將該相鄰層交叉耦合至頻譜分析儀。耦合到相鄰層的信號量如圖8所示。即使間距40密爾,某種意義上它仍是電容,因此在某些頻率下仍會耦合信號至相鄰層。

圖8顯示了這樣的一個(gè)例子。舉例來說,假設(shè)一個(gè)層面上的高噪聲數(shù)字層具有高速開關(guān)的1 V信號。這意味著,另一層將看到1 mV的耦合(約60 dB隔離)。對具有2-V p-p滿量程擺幅的12位ADC,這是2 LSB的耦合。對于特定的系統(tǒng)這可能不成問題,但應(yīng)注意,如果系統(tǒng)的靈敏度提升兩位,從12位增至14位,此耦合的靈敏度只會提高四倍,即8 LSB。

忽略此類型的交叉層耦合可能使系統(tǒng)失效,或者削弱設(shè)計(jì)。必須注意,兩層之間存在的耦合可能超出想象。

在目標(biāo)頻譜內(nèi)發(fā)現(xiàn)噪聲雜散耦合時(shí)應(yīng)注意這一點(diǎn)。有時(shí)布局決定了非預(yù)期信號或?qū)討?yīng)交叉耦合至不同層。同樣,調(diào)試敏感系統(tǒng)時(shí)應(yīng)注意這一點(diǎn)。該問題可能出現(xiàn)在下面一層。

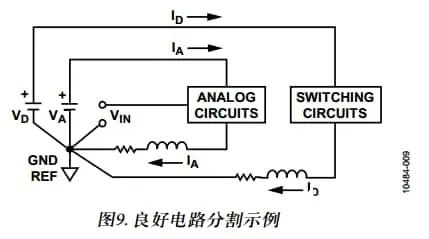

分離接地

模擬信號鏈設(shè)計(jì)人員最常提出的問題是:使用ADC時(shí)是否應(yīng)將接地層分為AGND和DGND接地層?簡單回答是:視情況而定。

詳細(xì)回答則是:通常不分離。為什么不呢?因?yàn)樵诖蠖鄶?shù)情況下,盲目分離接地層只會增加返回路徑的電感,它所帶來的壞處大于好處。

從公式V = L(di/dt)可以看出,隨著電感增加,電壓噪聲會提高。隨著電感增加,設(shè)計(jì)人員一直努力壓低的PDS阻抗也會增加。隨著提高ADC采樣速率的需求繼續(xù)增長,降低開關(guān)電流(di/dt)的方式卻很有限。因此,除非需要分離接地層,否則請保持這些接地連接。

關(guān)鍵是電路分割要合理,這樣就不必分離接地層,如圖9所示。注意,如果布局允許您將電路保持在各自區(qū)域內(nèi),便不需要分離接地層。如此分割可提供星型接地,從而將返回電流局限在特定電路部分。

例如,受尺寸限制的影響,電路板無法實(shí)現(xiàn)良好的布局分割時(shí),就需要分離接地層。這可能是為了符合傳統(tǒng)設(shè)計(jì)要求或尺寸,必須將臟亂的總線電源或高噪聲數(shù)字電路放在某些區(qū)域。這種情況下,分離接地層是實(shí)現(xiàn)良好性能的關(guān)鍵。然而,為使整體設(shè)計(jì)有效,必須在電路板的某個(gè)地方通過一個(gè)電橋或連接點(diǎn)將這些接地層連在一起。因此,應(yīng)將連接點(diǎn)均勻地分布在分離的接地層上。

最終,PCB上往往會有一個(gè)連接點(diǎn)成為返回電流通過而不會導(dǎo)致性能降低或強(qiáng)行將返回電流耦合至敏感電路的最佳位置。如果此連接點(diǎn)位于轉(zhuǎn)換器、其附近或下方,則不需要分離接地。

結(jié)束語

由于最佳選項(xiàng)太多,布局考慮總是令人困惑。技術(shù)和原則一直是公司設(shè)計(jì)文化的一部分。工程師喜歡借鑒以前設(shè)計(jì)中的經(jīng)驗(yàn),同時(shí)產(chǎn)品上市壓力使設(shè)計(jì)人員不愿更改或嘗試新技術(shù)。他們拘泥于風(fēng)險(xiǎn)權(quán)衡,直至系統(tǒng)內(nèi)出現(xiàn)重大問題。

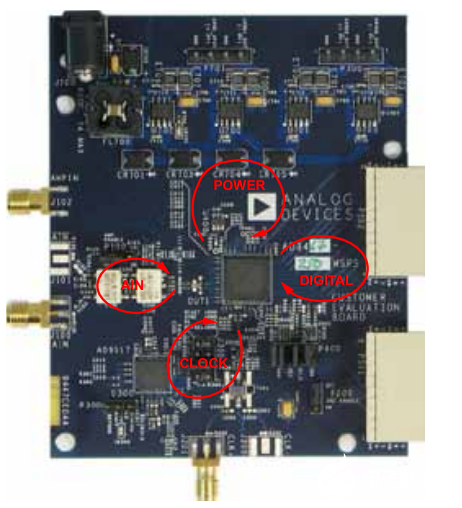

在評估板、模塊和系統(tǒng)級別,簡單的單一接地最佳。良好的電路分割是關(guān)鍵。這也影響到層和相鄰層布局。如果敏感層在高噪聲數(shù)字層以上,請注意可能會發(fā)生交叉耦合。組裝也很重要;提供給PCB車間或組裝車間的制造筆記應(yīng)善加利用,確保IC裸露焊盤和PCB之間具有可靠連接。

組裝不良常常導(dǎo)致系統(tǒng)性能欠佳。靠近電源層入口點(diǎn)和轉(zhuǎn)換器或IC的VDD引腳的去耦總是有利的。然而,為了增加固有高頻去耦電容,應(yīng)使用緊密疊置的電源和接地層(間距≤4密爾)。此方法不會帶來額外成本,只需花幾分鐘更新 PCB制造筆記。

設(shè)計(jì)高速、高分辨率轉(zhuǎn)換器布局時(shí),很難照顧到所有的具體特性。每個(gè)應(yīng)用都是獨(dú)一無二的。希望本應(yīng)用筆記所述的幾個(gè)要點(diǎn)有助于設(shè)計(jì)工程師更好地了解未來的系統(tǒng)設(shè)計(jì)。

審核編輯 黃宇

-

pcb

+關(guān)注

關(guān)注

4292文章

22768瀏覽量

393174 -

adc

+關(guān)注

關(guān)注

97文章

6296瀏覽量

542403 -

布局布線

+關(guān)注

關(guān)注

1文章

84瀏覽量

15141

發(fā)布評論請先 登錄

相關(guān)推薦

高速ADC PCB的布局布線技巧

ADI最受歡迎的《應(yīng)用筆記》,都進(jìn)來看看吧

PCB設(shè)計(jì)吐槽有理/禮,老司機(jī)帶你成長帶你飛

高速ADC PCB的布局布線技巧

高速ADC PCB布局布線技巧分享

高速ADC設(shè)計(jì)中的PCB布局布線技巧有哪些?

高速ADC PCB布局布線技巧

高速ADC PCB布局布線技巧

高速ADC PCB布局布線技巧分享

高速PCB的布局布線優(yōu)化

高速ADC PCB布局布線技巧

高速ADC、PCB布局布線技巧

高速ADC PCB布局布線技巧分享

高速ADC PCB布局布線技巧分享

評論