一、原理圖繪制及檢查流程

| 階段 | 流程 |

| 原理圖繪制 | 根據已有原理圖或資料(數據手冊、方案書)繪制原理圖 |

| DRC檢查 | EDA的DRC自檢,初步找出繪制不合理部分 |

| 根據Check List自檢 | 根據Check List進行原理圖及PCB詳檢 |

二、原理圖檢查清單細則

| 原理圖Check List | |||

| 電源電路 | 自檢確認項目 | 確認結果 | 備注 |

| 應用設計 | 模擬部分數字部分是否隔離 | ||

| 每個IC的電源引腳是否都有一個去耦電容 | |||

| 去耦/儲能電容是否足夠大 | |||

| 電感、電阻、磁珠的額定功率、電流是否達到要求 | |||

| 電源大小的配置電阻是否設置正確(反饋引腳電阻) | |||

| 電源網絡上的電容額定電壓是否合適 | |||

| 需要測試的電源處是否添加測試點 | |||

| 電源輸出精度是否滿足要求 | |||

| 輸出電流能力是否超過負載峰值20% | |||

| DC-DC設計 | 是否有防反接電路 | ||

| 輸入電容耐壓是否滿足要求 | |||

| 電源電路是否有指示燈 | |||

| 開關電感下不允許有信號線通過 | |||

| 開關電感的飽和電流是否滿足70%裕量 | |||

| 有兩路及兩路以上使用同一個DCDC電路,輸出端和地平面是否分割 | |||

| DCDC散熱是否有考慮 | |||

| 參考設計來源及與參考設計的不同之處說明 | |||

| LDO設計 | 最低壓差是否滿足要求 | ||

| 散熱引腳是否有足夠的散熱銅皮 | |||

| 輸入使能默認使能還是失能 | |||

| 時鐘部分 | 自檢確認項目 | 確認結果 | 備注 |

| 時鐘電路 | 時鐘及高速信號是否有正確的連接方式 | ||

| 時鐘信號是否采用點到點連接 | |||

| 無源晶振設計 | 無源晶振是否有起振電阻設計(1MΩ)(也可0Ω代替,需要時更換) | ||

| 無源晶振起振電容是否滿足要求 | |||

| 無源晶振的精度是否滿足要求 | |||

| 復位電路 | 自檢確認項目 | 確認結果 | 備注 |

| 確認主芯片復位是高電平復位還是低電平復位 | |||

| 確認主芯片復位的電平時間 | |||

| 主芯片是否為上電復位,是否有上/下拉電阻 | |||

| 原理圖 | 自檢確認項目 | 確認結果 | 備注 |

| 原理圖是否采用0.05inch柵格 | |||

| 原理圖圖頁規格采用A4規格,元器件過大時可使用A3規格 | |||

| 必要的部分是否有注釋標注 | |||

| 每張原理圖是否有文件名 | |||

| 所有元器件是否有符號和容量等標識 | |||

| 電阻、電容、電感等器件的管腳標注等不必要標識不要顯示 | |||

| LED顏色標識是否顯示 | |||

| 器件管腳上的引線,應引出后再分叉,不得直接在器件管腳上分叉。 | |||

| 電路是否需要上/下拉電阻 | |||

| 各個管腳的上/下拉電阻是否正確 | |||

| 提供各單點網絡列表和 連接管腳列表,并一一確認 | |||

| 確認原理圖中的器件與數據手冊一致 | |||

| 確認器件名稱及位號是否正確 | |||

| 多圖頁原理圖是否有重新分配位號 | |||

| 總線的名稱和作用是否有標識 | |||

| 網絡標識的標注是否正確 | |||

| 是否已經標識出需要阻抗匹配的電路 | |||

| GND及電源測試點是否標識 | |||

| 確認DRC檢查的每個錯誤及警告是否已經修改正確 | |||

| 最新的原理圖生成的網表必須保證已經導入PCB | |||

| 可以邀請其他成員一起檢查原理圖設計 | |||

| PCB Check List | |||

| 規則設置 | 自檢確認項目 | 確認結果 | 備注 |

| 安全距離設置是否正確 | |||

| 是否正確設置物理和電氣規則(注意電源網絡和地網絡的約束設置) | |||

| Test Via、Test Pin的間距設置是否足夠 | |||

| 疊層的厚度和方案是否滿足設計和加工要求 | |||

| 所有有特性阻抗要求的差分線阻抗是否已經經過計算,并用規則控制 | |||

| 確認DRC已經調整到最少,對于不能消除DRC要一一確認 | |||

| 器件檢查 | 自檢確認項目 | 確認結果 | 備注 |

| 確認所有器件封裝是否與公司統一庫一致,是否已更新封裝庫 | |||

| 元器件是否100% 放置 | |||

| 較重的元器件,應該布放在靠近PCB支撐點或支撐邊的地方,以減少PCB的翹曲 | |||

| 接口相關的器件盡量靠近接口放置 | |||

| 發熱量大的器件是否需要加裝散熱片,距離是否足夠 | |||

| 金屬殼體的元器件,特別注意不要與其它元器件相碰,要留有足夠的空間位置 | |||

| 與結構相關的器件布好局后是否鎖住以防止誤操作移動位置 | |||

| 在PCB上軸向插裝較高的元件,應該考慮臥式安裝 | |||

| 功能檢查 | 自檢確認項目 | 確認結果 | 備注 |

| 數模混合板的數字電路和模擬電路器件布局時是否已經分開,信號流是否合理 | |||

| A/D轉換器跨模數分區放置 | |||

| 時鐘器件布局是否合理 | |||

| 高速信號器件布局是否合理 | |||

| IC器件的去耦電容數量及位置是否合理 | |||

| 信號線以不同電平的平面作為參考平面,當跨越平面分割區域時,參考平面間的連接電容是否靠近信號的走線區域 | |||

| 保護電路的布局是否合理,是否利于分割 | |||

| 電源電路 | 自檢確認項目 | 確認結果 | 備注 |

| 是否IC電源距離IC過遠 | |||

| LDO及周圍電路布局是否合理 | |||

| 模塊電源等周圍電路布局是否合理 | |||

| 電源的整體布局是否合理 | |||

| 絲印檢查 | 自檢確認項目 | 確認結果 | 備注 |

| 器件位號是否遺漏,位置是否能正確標識器件 | |||

| 器件位號是否符合公司標準要求 | |||

| 確認器件的管腳排列順序、第1腳標志、器件的極性標志、連接器的方向標識的正確性 | |||

| 確認設計要求的絲印添加是否正確 | |||

| 確認PCB編碼正確且符合公司規范 | |||

| 確認單板的PCB編碼位置和層面正確 | |||

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

原理圖

+關注

關注

1293文章

6310瀏覽量

232902 -

pcb

+關注

關注

4317文章

23002瀏覽量

396228 -

Checklist

+關注

關注

0文章

7瀏覽量

3225

發布評論請先 登錄

相關推薦

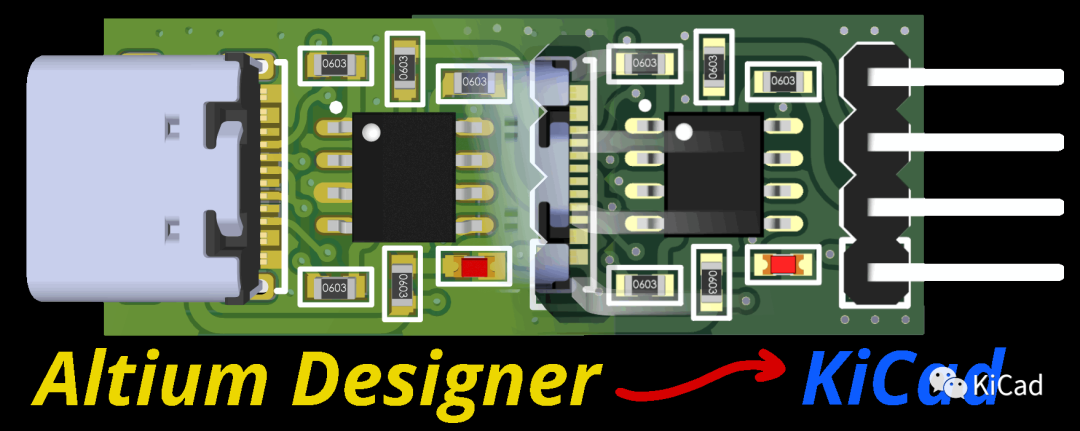

如何導入Altium Designer的原理圖和PCB?

“ ?KiCad可以支持直接導入Altium Designer的原理圖及PCB文件。與其它導入器不同,KiCad導入器可以直接導入源生的二進制文件(*.schdoc及*.pcbdoc),而不需要像

ad怎么實現原理圖與pcb元件對應

在Altium Designer(AD)中,實現原理圖(Schematic)與PCB(Printed Circuit Board)元件對應的過程是一個關鍵的設計步驟,它確保了電路設計的準確性和一致性

AD20原理圖跟PCB怎么交互

在Altium Designer 20(簡稱AD20)中,原理圖和PCB之間的交互是設計流程中的一個重要環節,它允許設計師在邏輯設計和物理實現之間自由切換,確保設計的準確性和一致性。以下是AD20

ad怎么把原理圖和pcb相關聯

在Altium Designer(簡稱AD)中,將原理圖和PCB相關聯是一個重要的設計步驟,它確保了從邏輯設計到物理實現的順利過渡。以下是實現原理圖和PCB相關聯的步驟: 一、分配元件

AD畫完原理圖后如何導入PCB

在Altium Designer(簡稱AD)中,將畫完的原理圖導入到PCB(Printed Circuit Board,印制電路板)是一個關鍵的設計步驟。以下是導入過程: 一、準備階段 確保原理圖

altium怎么把原理圖導入pcb

在Altium Designer中,將原理圖導入到PCB設計是一個關鍵的步驟,它確保了電路設計的準確性和可制造性。這個過程涉及到多個階段,包括原理圖的創建、編譯、檢查以及最終的導入到PCB

Altium怎么把原理圖換成pcb

在Altium Designer中,將原理圖轉換為PCB(Printed Circuit Board,印制電路板)圖是一個關鍵的設計步驟。以下是將原理圖換成

FS201資料(pcb & DEMO & 原理圖)

電子發燒友網站提供《FS201資料(pcb & DEMO & 原理圖).zip》資料免費下載

發表于 07-16 11:24

?0次下載

干貨!原理圖設計規范133條checklist

原理圖設計是產品設計的理論基礎,設計一份規范的原理圖對設計PCB、跟機、做客戶資料具有指導性意義,是做好一款產品的基礎。原理圖設計基本要求: 規范、清晰、準確、易讀。因此制定《

發表于 04-01 15:50

ad原理圖封裝怎么和pcb封裝關聯

AD原理圖封裝與PCB封裝關聯是電子設計自動化(EDA)過程中的重要環節。為了實現這一關聯,需要遵循一定的步驟和注意事項。 一、AD原理圖封裝與PCB封裝的關聯原理 在電子設計中,

原理圖和pcb的關系

原理圖和pcb的關系? 原理圖和PCB之間有著密切的關系,它們是電子設計中兩個不可分割的部分。原理圖是電子設備的邏輯和電路圖紙,而

原理圖及PCB Checklist大放送~

原理圖及PCB Checklist大放送~

評論