源漏區嵌入SiC 應變技術被廣泛用于提高90nm 及以下工藝制程 NMOS 的速度,它是通過外延生長技術在源漏嵌入 SiC 應變材料,利用硅和碳晶格常數不同,從而對溝道和襯底硅產生應力,改變硅導帶的能帶結構,從而降低電子的電導有效質量和散射概率。

硅的晶格常數是5.431A,碳的晶格常數是3.57A,硅與碳的不匹配率是34.27%,從而使得 SiC 的晶格常數小于純硅,并且碳的晶格常數遠小于硅的晶格常數,SiC只需很少的碳原子就可得到很高的應力。圖2-7所示為在硅襯底上外延生長SiC應變材料外延。SiC會對橫向的溝道產生張應力,從而使溝道的晶格發生形變,晶格變大。

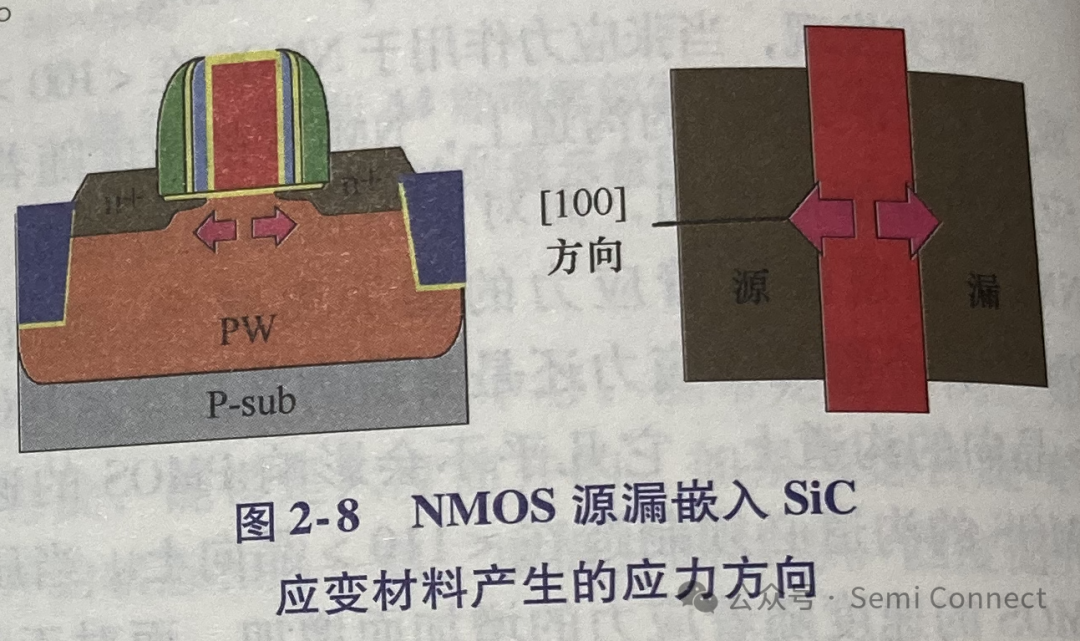

在 NMOS 的源漏嵌入SiC 應變材料,如圖2-8所示,NMOS的溝道制造在[100] 方向上,SiC應變材料會在該方向產生單軸的張應力,得到的主能谷的等能面的軸向都是垂直于溝道分向,沿溝道方向單軸張應力會減小溝道方向的電子電導有效質量和散射概率,源漏嵌入SiC應變材料可以有效地提高NMOS 的速度。

源漏嵌入 SiC 應變材料是選擇外延(Se-lective Epitaxial Growth,SEG)技術。選擇外延技術是利用外延生長的基本原理,以及硅在絕緣體上很難核化成膜的特性,在硅表面的特定區域生長外延層而其他區域不生長的技術。外延生長的基本原理是根據硅在SiO2上核化的可能性最小,在Si3N4上比在SiO2上大一點,在硅上可能性最大的特性完成的。這是因為在硅襯底上外延生長硅層是同質外延,而在SiO2和Si3N4上是異質外延,所以落在絕緣體上的原子因不易成核而遷移到更易成核的硅單晶區內。

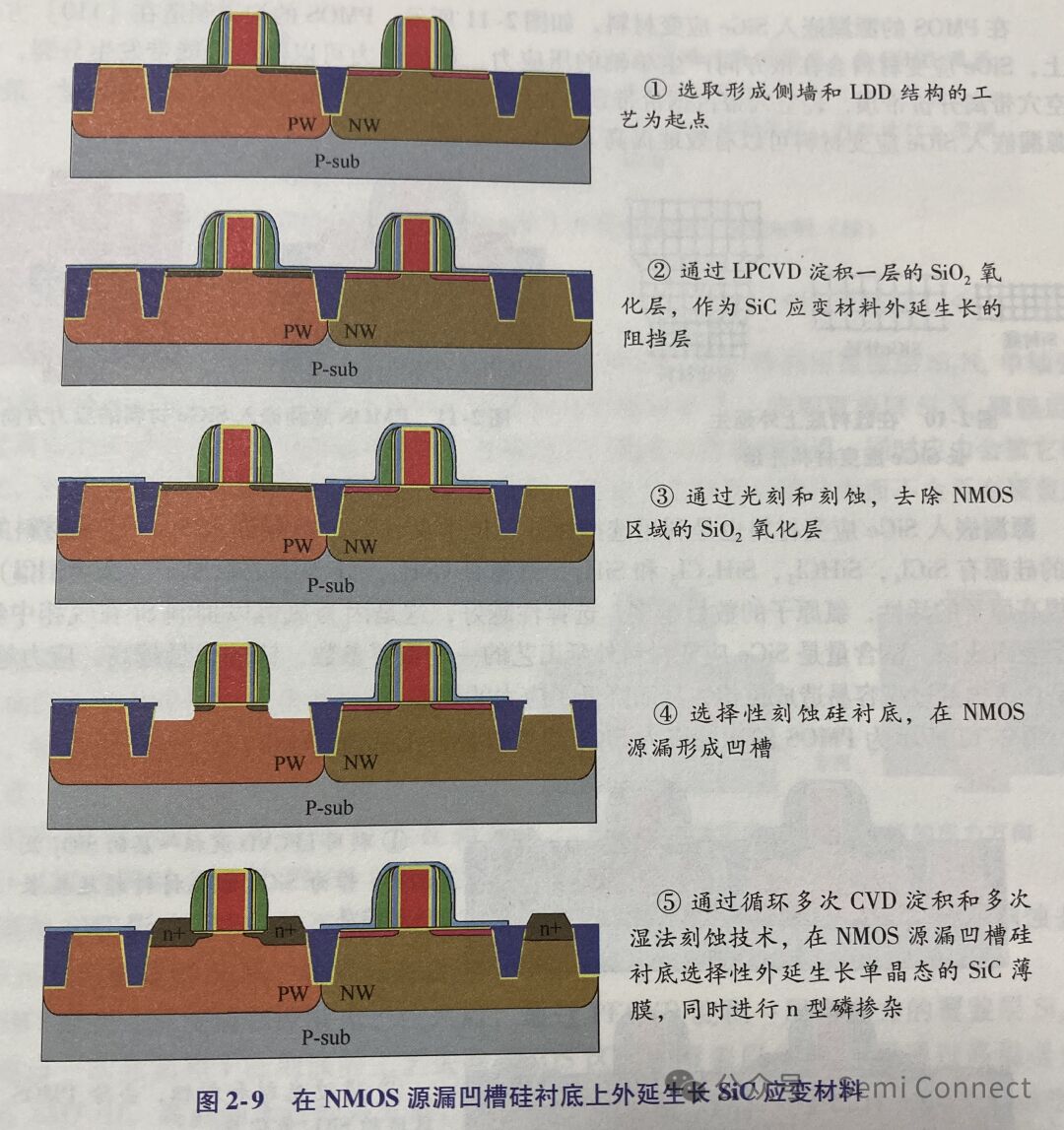

實現源漏嵌入 SiC 應變材料工藝具有一定的難度,因為SiC 應變材料外延生長工藝的選擇性比較差,它在源漏凹槽襯底生長的同時,也會在氧化物等非單晶區域上生長,例如在側壁和STI上生長 。可以通過CVD淀積和濕法刻蝕技術,進行多次淀積和多次刻蝕的方式來改善外延生長SiC 應變材料,因為利用CVD工藝可以在單晶硅襯底獲得單晶態的SiC 薄膜,而在氧化物等非單晶區域上得到非晶態的SiC 薄膜,由于非晶態的SiC 薄膜具有較高的刻蝕率,所以可以通過多次淀積和多次刻蝕循環在源漏單晶硅襯底上選擇性生長出一定厚度的單晶態SiC薄膜。

另外,SiC 應變材料在高溫熱退火的熱穩定性比較差,在大于900°C的高溫熱退火中,SiC 應變材料中的部分碳原子會離開替位晶格的位置,一旦替位碳原子離開替位晶格,應力就會失去,離開的碳原子的數量與高溫熱退火的時間成正比。所以在 SiC 應變材料薄膜形成后,必須嚴格控制高溫退火的時間,而先進的毫秒退火工藝可以改善這一問題。

圖2-9所示為 NMOS 的源漏嵌入SiC 應變材料的工藝流程。

-

NMOS

+關注

關注

3文章

290瀏覽量

34291 -

SiC

+關注

關注

29文章

2759瀏覽量

62449 -

晶格

+關注

關注

0文章

93瀏覽量

9192

原文標題:源漏嵌入 SiC 應變技術

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

金屬電阻應變片工作原理簡介

淺析SiC-MOSFET

海飛樂技術現貨替換IXFN50N120SIC場效應管

基于分布式光纖應變傳感器技術的山體滑坡在線監測預警方案

漏源電壓VDS相關資料下載

SiC MOSFET的器件演變與技術優勢

PNP與NPN哪個是“源”與”漏“的渾水

三菱PLC源型和漏型的區別

源漏嵌入SiC應變技術簡介

源漏嵌入SiC應變技術簡介

評論