對(duì)于從事芯片行業(yè)的人員來說,還是有必要了解數(shù)字電路中的一些基本概念,例如用作邏輯開關(guān)的 MOS 晶體管。當(dāng)然,我們的目的是了解現(xiàn)代芯片中的行為本質(zhì),而不需要陷入半導(dǎo)體物理方程。

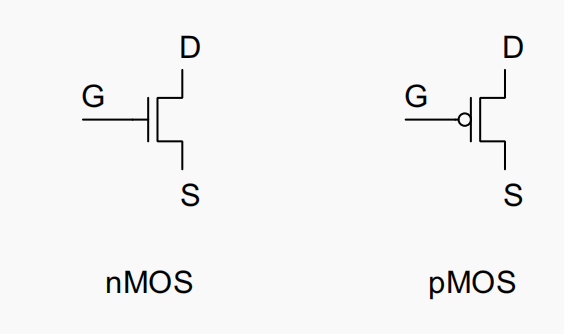

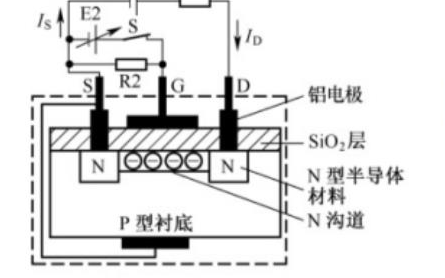

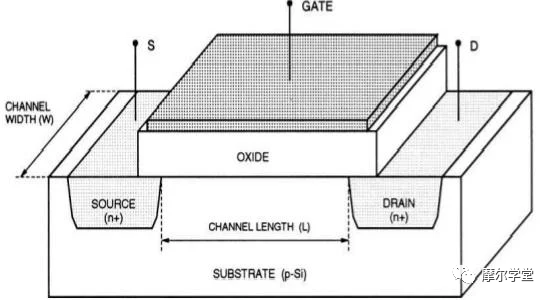

所有數(shù)字電路的基本組件是MOS晶體管。MOS是Metal-Oxid-Semiconductor金屬氧化物體的首字母縮寫,表示制造晶體管所用的制造工藝。有三個(gè)端口:柵極 (G)、漏極 (D) 和源極 (S)。

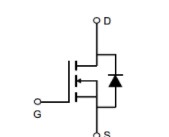

柵極是一個(gè)控制輸入:它控制源極和漏極之間的電流流動(dòng)。MOS晶體管有兩種類型:nMOS和pMOS。上圖顯示了兩個(gè)MOS晶體管的符號(hào)。

MOS晶體管作為開關(guān)

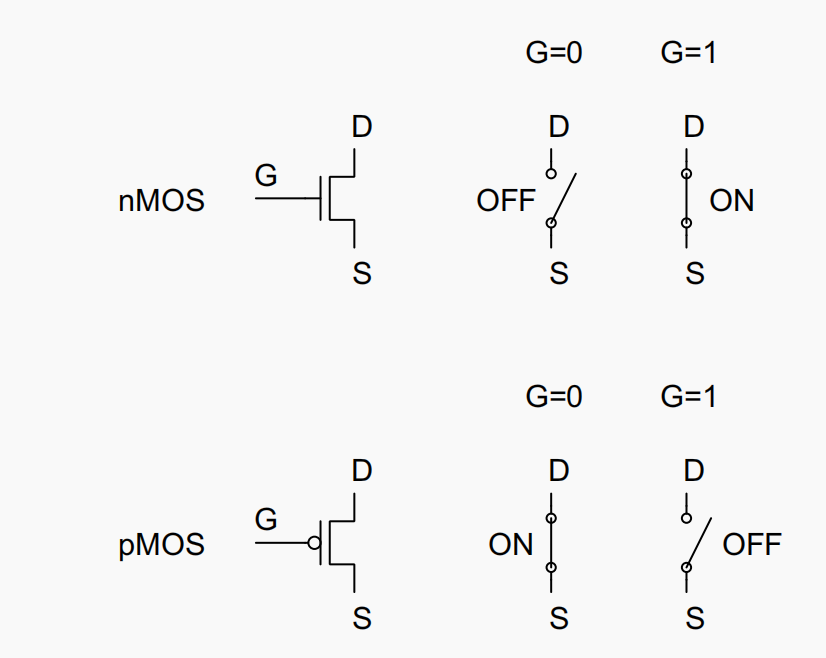

首先考慮nmos晶體管。如果柵極接地 (邏輯0),則漏極和源極之間沒有電流流動(dòng)。因此,我們說晶體管是關(guān)的,對(duì)應(yīng)于邏輯0。如果柵電壓高,則從源極到漏極電流可以流動(dòng)。我們說晶體管是開著的,對(duì)應(yīng)于邏輯1。

PMOS晶體管正好相反。當(dāng)柵極處于與邏輯1相對(duì)應(yīng)的正電壓時(shí)沒有電流流,晶體管處于OFF狀態(tài)。與邏輯0相對(duì)應(yīng)的足夠低的柵電壓則會(huì)形成從源極到漏極的導(dǎo)通路徑,因此晶體管處于ON狀態(tài)。

總之,MOS晶體管的柵極控制源極和漏極之間的電流流動(dòng),使我們可以將MOS晶體管視為ON/OFF開關(guān)。

當(dāng)nMOS晶體管的柵極為1時(shí),晶體管是接通的,電流在源極和漏極之間流動(dòng)。當(dāng)柵極為0時(shí),nMOS晶體管關(guān)閉,源極和漏極之間沒有電流流動(dòng)。pMOS晶體管正好相反,當(dāng)柵極電壓為低時(shí)接通,當(dāng)柵極高時(shí)關(guān)斷。

CMOS作為反相器

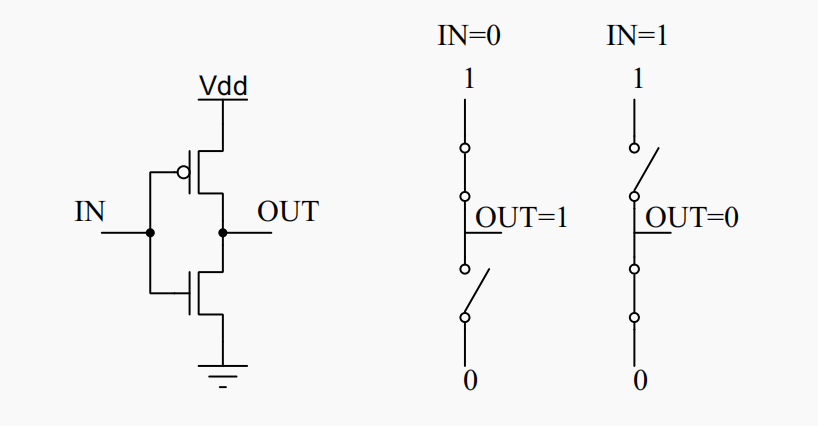

使用MOS晶體管建立的最簡(jiǎn)單的邏輯門是反相器。反相器由兩個(gè)互補(bǔ)MOS晶體管組成,一個(gè)是nMOS,一個(gè)是pMOS,互補(bǔ)MOS(CMOS)反相器因此而得名。下圖顯示了使用一個(gè)nMOS晶體管和一個(gè)pMOS晶體管的CMOS反相器或"非"門的原理圖和開關(guān)級(jí)模型。

輸入IN連接兩個(gè)晶體管的門。當(dāng)輸入IN為0時(shí),nMOS晶體管為OFF,而pMOS晶體管為ON。因此,輸出OUT被拉到邏輯1,因?yàn)樗ㄟ^pMOS晶體管連接到Vdd。相反,當(dāng)IN為1時(shí),nMOS為ON,PMOS為OFF,而OUT則被拉低到“0”,因?yàn)樗ㄟ^nMOS晶體管與GND相連。

到這里,我們的數(shù)字電路可以完成一些最基本的邏輯功能,但是還不能夠存儲(chǔ)信息。

雙穩(wěn)態(tài)元件

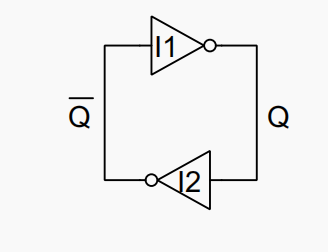

現(xiàn)在我們已經(jīng)熟悉了MOS晶體管和CMOS反相器,是時(shí)候?qū)W習(xí)如何在MOS數(shù)字電路中存儲(chǔ)1bit信息了,即如何使用MOS晶體管和反相器形成一個(gè)1位存儲(chǔ)單元。存儲(chǔ)器的基本組件是雙穩(wěn)態(tài)元件,即具有兩個(gè)穩(wěn)定狀態(tài)的邏輯元件。下圖顯示了由兩個(gè)反相器I1和I2組成的雙穩(wěn)態(tài)元件。反相器是交叉耦合的,這意味著11的輸入是I2的輸出,反之亦然。

如果Q=0,12接收到一個(gè)False輸入,在輸出上產(chǎn)生一個(gè)TRUE輸出。11接收到一個(gè)TRUE輸入,在輸出上產(chǎn)生一個(gè)False輸出。這與最開始的輸入Q=0是一致的,所以電路處于穩(wěn)態(tài)。

如果Q=1,12接收一個(gè)TRUE輸入,在輸出上產(chǎn)生一個(gè)FALSE輸出。11接收一個(gè)FALSE輸入,在輸出上產(chǎn)生一個(gè)TRUE輸出。與最初的輸入Q=1是一致的,所以同樣電路處于穩(wěn)態(tài)。

因?yàn)榻徊骜詈戏聪嗥饔袃蓚€(gè)穩(wěn)定狀態(tài),0和1,所以電路被稱為雙穩(wěn)態(tài)。交叉耦合反相器的狀態(tài)包含在一個(gè)二進(jìn)制狀態(tài)變量Q中。具體來說,如果Q=0,它將永遠(yuǎn)保持0,如果Q=1,它將永遠(yuǎn)維持1。

雖然交叉耦合反相器可以存儲(chǔ)一點(diǎn)信息,但它們不實(shí)用,因?yàn)橛脩魶]有輸入來控制狀態(tài)。因此,我們必須用電路來擴(kuò)展雙穩(wěn)態(tài)元件,它提供輸入以控制狀態(tài)變量的值。一個(gè)這樣的元件,可以接受輸入來控制存儲(chǔ)在雙穩(wěn)態(tài)的值是一個(gè)靜態(tài)RAM單元。

后續(xù)我們?cè)俳榻BSRAM和DRAM。

到這里,雖然不夠?qū)嵱茫俏覀円呀?jīng)可以使用MOS晶體管設(shè)計(jì)組合邏輯和時(shí)序邏輯了,這是芯片科技的關(guān)鍵一步。

-

CMOS

+關(guān)注

關(guān)注

58文章

5603瀏覽量

234212 -

反相器

+關(guān)注

關(guān)注

6文章

306瀏覽量

42955 -

晶體管

+關(guān)注

關(guān)注

77文章

9403瀏覽量

136637 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1536瀏覽量

80087

原文標(biāo)題:數(shù)字電路的基礎(chǔ)——CMOS

文章出處:【微信號(hào):數(shù)字芯片實(shí)驗(yàn)室,微信公眾號(hào):數(shù)字芯片實(shí)驗(yàn)室】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

MOS晶體管

【下載】《晶體管電路設(shè)計(jì)》——晶體管電路基礎(chǔ)知識(shí)匯總

晶體管電路設(shè)計(jì)

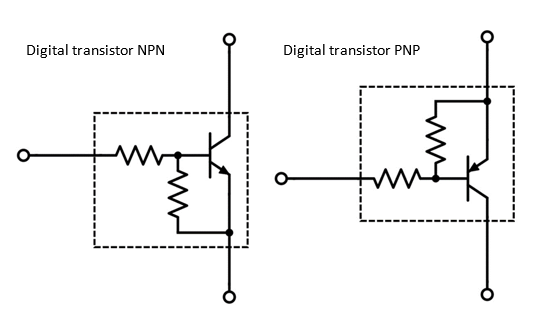

數(shù)字晶體管的原理

數(shù)字晶體管的原理

增強(qiáng)型MOS晶體管,增強(qiáng)型MOS晶體管是什么意思

MOS晶體管的應(yīng)用

MOS晶體管結(jié)構(gòu)與CMOS單元電路與版圖闡述

MOS管和晶體管的概念

淺析MOS 晶體管的核心概念

如何使用數(shù)字晶體管

數(shù)字電路的基礎(chǔ)概念:MOS晶體管

數(shù)字電路的基礎(chǔ)概念:MOS晶體管

評(píng)論