本文從數字芯片設計項目技術總監的角度出發,介紹了如何將芯片的產品定義與設計和驗證規劃進行結合,詳細講述了在FPGA上使用IP核來開發ASIC原型項目時,必須認真考慮的一些問題。文章從介紹使用預先定制功能即IP核的必要性開始,通過闡述開發ASIC原型設計時需要考慮到的IP核相關因素,用八個重要主題詳細分享了利用ASIC所用IP來在FPGA上開發原型驗證系統設計時需要考量的因素。

本篇文章是SmartDV數字芯片設計經驗分享系列文章的第一篇,作為全球領先的驗證解決方案和設計IP提供商,SmartDV的產品研發及工程應用團隊具有豐富的設計和驗證經驗。在國產大容量FPGA新品不斷面市的今天,SmartDV及其中國全資子公司“智權半導體”愿意與國內FPGA芯片開發商合作,共同為國內數字芯片設計公司開發基于本地FPGA的驗證與設計平臺。

明了設計需求

半導體IP核提供商支持復雜的ASIC項目,其中一些項目在時鐘速度、片芯面積占用、功耗、可靠性、功能安全和可重用性方面有極高的要求,所有這一切都帶來了對半導體IP這種預先定制的電路部件的很高期望。一旦有人決定自己不去開發某項功能,而是通過合作伙伴獲得該功能,都會將購買該組件的功能視為必然結果。如果所使用的IP核來自諸如SmartDV這類信譽良好的供應商,該過程將順利進行。

廣告

由于同一IP核的最終應用領域可能完全不同,因此IP核提供商必須將所有可能的應用領域考慮在內,以避免讓客戶失望。例如像MIPICSI-2接收器/發射器IP或USB接口這樣的預定制功能,在用于一款已經被銷售數百萬次的消費性產品中時,它的要求就與該功能被用于數量有限的噴氣戰斗機這樣的“熱點領域”有所不同。

對一位用戶來說,成功的產品定義可能是片芯面積的縮小。而對另一位用戶來說,它也可能意味著即使在惡劣的運行條件下,也可以實現最低的功耗或最高的可靠性。在大多數情況下,還有另外一個關鍵點需要考慮。IP核不僅應該只在ASIC上“實現功能”,而且還可用作基于FPGA的原型設計的一部分。眾所周知,在開發ASIC的過程中需要非常謹慎,但遺憾的是,我們常常低估了FPGA也需要非常特別的關注,并且還有其獨特的集成方式。

坦率地來講,將ASICIP核移植到FPGA中并不是一件容易的任務,但如果這個過程有條不紊,成功是可以實現的!本文全面講述了將ASICIP核移植到FPGA中時必須考慮到的所有要點,并通過使用SmartDV的USB3.2Gen2x1DeviceIP實例來進一步說明這些要點。

對于芯片設計工程師的關鍵價值

將一款IP核部署到ASIC和FPGA兩種架構中具有挑戰性,但值得一試。

將ASICIP移植到FPGA中時,需要考慮的相關因素包括在需求、性能、時鐘、功能等方面的差異。

最佳的芯片設計解決方案是用FPGA來作為原型工具,以及它和經過流片驗證的IP核的結合,以保證正確無誤地實現設計。

無論目標是ASIC還是FPGA,快速且成功完成項目的一個關鍵因素是涉及該項目的專家團隊的經驗水平,因此選擇一個可靠的IP合作伙伴也是設計團隊取得成功的又一關鍵!

使用預先定制功能即IP核的必要性

集成電路設計團隊的最終目標是能夠更快速地交付一款有效用的最終產品,以便于不錯過更早進入市場的機會,并確保在競爭對手面前建立自己的競爭優勢。多年來,使用IP核一直是最大限度地縮短復雜電路的開發時間,以及減少驗證電路組件所需工作量的一種通用方法。

使用預先定制的電路組件消除了“重新創造輪子”的需要,但是IP核需要能夠在提高可靠性和避免錯誤這兩個方面之外提供額外的優勢,因為它們(通常)已經被其他工程師們部署在其項目中。一段時間以來,業內已經用了一個恰當的術語“左移”來描述這一現象,即在產品生命周期的早期階段就執行測試。從產品規格的創建到ASIC模塊設計的流片,時間窗口在整個時間軸上都朝著項目開始的方向移動。

同樣,在設計過程中使用FPGA早已被確立為一種標準方法,以便能夠在可提供ASIC之前就對數字電路進行測試。這個理念導致了使用一個現成可用的、可重新編程或可重新配置的FPGA硬件組件來以實時速度運行設計,以在設計流程的早期階段檢測出錯誤。

與最終的ASIC相比,FPGA絕不是成本低廉的解決方案,但它可為設計團隊帶來實實在在的價值,從而支持設計團隊去有效地發現在電路創建過程中已經產生的錯誤,這些錯誤無法通過仿真或其他基于軟件的驗證方法檢測到。通過擴展,它還支持在驗證過程中發現和消除缺陷。

此外,在ASIC芯片開始供貨之前,通常希望有一個可用的功能平臺,以便能夠在開發硬件的同時,去實現和測試運行所需的軟件和固件。因此,可以安全地假設IP核的使用和FPGA的使用都是經過驗證的電路實現和驗證方法,其應用不會造成任何困難。然而,實際設計過程也經常是“細節決定成敗”。

面向ASIC原型驗證的IP核考量因素

實際上,提供一款IP并將其無縫地用于ASIC和FPGA是一項極具挑戰性的任務。在本節中,我們將討論在考慮原型設計任務時就開始出現的最普遍的問題。

原型設計:各種考量因素的總體概述

主題1:一款原型和最終ASIC實現之間的要求有何不同?

主題2:當使用FPGA進行原型設計時會立即想到哪些基本概念?

主題3:在將專為ASIC技術而設計的IP核移植到FPGA架構上時通常會遇到哪些困難?

主題4:為了支持基于FPGA的原型,通常需要對ASICIP核進行哪些更改?

主題5:我們如何確保在FPGA上實現所需的性能?

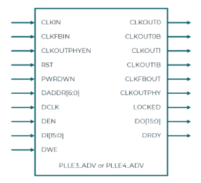

主題6:在時鐘方面必須加以考量的因素有哪些?

主題7:如果目標技術是FPGA,而不是ASIC,那么需要如何測試IP核的功能?

主題8:設計團隊還應該牢記什么?

認為只需要將打算實例化的IP模塊和集成該模塊的實例之間的物理接口進行匹配就行的這種理念就是不現實的。為了能夠成功地集成預先定制的電路功能,需要考慮更多的問題。

事實上,嵌入IP核遠非易事!有各種各樣的參數可能需要調整:例如,必須確保時鐘信號與頻率匹配,還必須特別注意復位的分布規律。輸入和輸出信號必須與電路的其余部分同步;甚至可能需要應用帶有延遲的時鐘和數據信號。IP核的集成也改變了整個系統的延遲,額外的功能也影響電路的時序行為,邏輯門利用以及諸如存儲單元的使用等等。

事實是一款IP核必須為不同的目標架構提供相同的功能——例如,來自不同制造商的ASIC和FPGA產品,它們具有不同的工藝節點和結構,這給功能實現的質量提出了特殊挑戰;同時,也對IP供應商用于驗證和物理確認電路功能的方法提出了特殊挑戰。

主題1:一款原型和最終ASIC實現之間的要求有何不同?

通常,與基于FPGA的原型設計相比,在ASIC設計的后期會提出各種不同的要求。例如,除了提供實際的電路功能之外,ASIC規范的主要關注點可以是降低功耗,也可能是占用最小的片芯面積,甚至是實現最高的時鐘頻率。此外,必須提供測試結構方案來支持功能測試,重點是能識別已流片的ASIC的物理缺陷。

所有這些要求都與在原型設計期間如何在FPGA中使用IP幾乎無關,進一步的解釋如下所述:

片芯面積占用(使用邏輯門數量)在原型設計中扮演著次要的角色。當然,我們希望所使用的FPGA器件的復雜度越低越好,這樣原型的性價比更高且可減少總體支出。然而,在許多情況下,從一開始就有一個“盡可能大”的可重構的模塊是非常明智的,這樣就能夠覆蓋可能導致面積占用量增加的電路變化,而不需要在原型設計進行期間將FPGA器件切換到更復雜的FPGA。切換很可能需要重新設計,或者在使用預先定制的FPGA開發板的情況下,重新購買一個基于FPGA的原型驗證平臺。

功耗對于一個目標僅為實現單一功能的原型設計來說根本不重要,但是開發人員也期望部署專為ASIC降低功耗開發的方法,并將其包含在原型設計中則可能是明智的做法。關于該話題的更詳細的討論,可以在接下來的主題8的答案下找到:我們還應該牢記什么?

ASICRTL可能包含測試結構,以實現數字部件的大規模量產測試,目的是找出有缺陷的單元。為了支持相關的測試,需要實現測試結構。然而,這些類型的測試結構通常不在FPGA中實現,因為根本不需要它們。FPGA組件已經經過了充分的測試。

本系列文章的目標是全面分享如何利用ASICIP來實現完美的FPGA驗證原型的經驗,本篇在講述了如何了解ASICIP與FPGA驗證原型的區別并提前做相應規劃之后,還將詳細介紹與之相關的另外七大主題。下一篇將介紹使用FPGA進行原型設計時會立即想到哪些基本概念?在將專為ASIC技術而設計的IP核移植到FPGA架構上時通常會遇到哪些困難?以及為了支持基于FPGA的原型,通常需要對ASICIP核進行哪些更改?歡迎關注SmartDV全資子公司“智權半導體”微信公眾號繼續閱讀。

最后,SmartDV在相關介紹和分析之后,還提供實際案例:用基于FPGA的方法來驗證USB3.2Gen2x1DeviceIP

USB3.2Gen2x1DeviceIP:實現、驗證和物理驗證

USB3.2Gen2x1DeviceIP的實現挑戰

關于作者

PhilippJacobsohn

PhilippJacobsohn是SmartDV的首席應用工程師,他為北美、歐洲和日本地區的客戶提供設計IP和驗證IP方面的支持。除了使SmartDV的客戶實現芯片設計成功這項工作,Philipp還是一個狂熱的技術作家,樂于分享他在半導體行業積累的豐富知識。在2023年加入SmartDV團隊之前,Philipp在J.Haugg、Synopsys、Synplicity、EpsonEuropeElectronics、LatticeSemiconductors、EBVElektronik和SEI-Elbatex等擔任過多個管理和現場應用職位。Philipp在瑞士工作。

SunilKumar

SunilKumar是SmartDV的FPGA設計總監。作為一名經驗豐富的超大規模集成電路(VLSI)設計專業人士,Sunil在基于FPGA的ASIC原型設計(包括FPGA設計、邏輯綜合、靜態時序分析和時序收斂)和高速電路板設計(包括PCB布局和布線、信號完整性分析、電路板啟動和測試)等方面擁有豐富的專業知識。在2022年加入SmartDV團隊之前,Sunil在L&TTechnologyServicesLimited擔任過項目經理和項目負責人職位。Sunil在印度工作。

關于智權半導體

智權半導體科技(廈門)有限公司是SmartDVTechnologies?在華設立的全資子公司,其目標是利用SmartDV全球領先的硅知識產權(IP)技術和產品,以及本地化的支持服務來賦能中國集成電路行業和電子信息產業。目前,SmartDV在全球已有300家客戶,其中包括十大半導體公司中的七家和四大消費電子公司。

通過將專有的SmartCompiler?技術與數百位專家工程師的知識相結合,SmartDV可以快速、經濟、可靠地定制IP,以實現您獨特的設計目標。因此,無論您是為下一代SoC、ASIC或FPGA尋找基于標準的設計IP,還是尋求驗證解決方案(VIP)來測試您的芯片設計,您都會發現SmartDV的IP非常容易集成,并在性能上可力助您的芯片設計實現差異化。

審核編輯 黃宇

-

FPGA

+關注

關注

1620文章

21471瀏覽量

597976 -

asic

+關注

關注

34文章

1171瀏覽量

119870

發布評論請先 登錄

相關推薦

數字芯片設計驗證經驗分享:將ASIC IP核移植到FPGA上——明了需求和詳細規劃以完成充滿挑戰的任務

數字芯片設計驗證經驗分享:將ASIC IP核移植到FPGA上——明了需求和詳細規劃以完成充滿挑戰的任務

評論