1. 引言

隨著嵌入式技術飛速發展,高速電路的開發面臨器件尺寸縮小、時鐘頻率提升、布線密度增加等因素,嵌入式產品在信號傳輸、電源質量等問題上要求日益提高。為確保高速電路在產品整個生命周期內的可靠性,必須采用先進的可靠性技術。

武漢萬象奧科學習易瑞來殷老師可靠性相關課程與經驗,以更好的應對這些挑戰。

2. 高速電路開發的挑戰

由于產品和器件的尺寸不斷縮小,器件的時鐘頻率越來越高,信號邊緣速率也越來越快,導致高速電路問題日益突出。現在IC的集成規模越來越大,管腳數量越來越多,單板上布線的密度不斷加大,IC的電源電壓逐漸降低、電流逐漸加大,功耗越來越大。

以上幾個方面就是現代高速電路開發的最新挑戰,對設計者的可靠性設計水平提出了更高的要求。

高速電路中的器件參數不一致,或發生飄移,使得整個電路的性能逐步降低,直至功能完全喪失。也可能產生過電應力或降額不足,使器件失效。SI問題的隱蔽性較大,往往在出廠前無法測試或通過老化篩選出問題,帶來可靠性隱患。

可靠性設計主要就是解決產品在整個生命周期內出現的品質問題,既可以解決產品性能退化的問題,也可以解決器件失效的問題。可靠性技術在高速電路中的應用主要有最壞情況數字電路時序容差分析、串擾分析和電源完整性技術等。

3. 高速電路可靠性問題

高速電路引起的可靠性問題主要有以下5個方面:

信號傳輸延時逐步加大,造成時序失效。

信號波形失真逐步加大,造成信號讀取錯誤。

信號之間的串擾逐步加大,產生誤碼或程序運行錯誤。

電源質量和地彈逐步變壞,影響器件的正常工作。

EMC指標逐漸超過要求。

4. 高速電路設計的可靠性技術

解決上述5個方面的問題,個人認為可以采用以下3種可靠性技術來解決:

1) 運用最壞情況分析(WCCA)方法,進行數字電路時序分析,使傳輸線延時、波形失真等在整個生命周期內不超過要求,保證高速數字電路的正常邏輯連接。

以前的電路板運行速度較低,因此很少有時序問題,現在的器件速度越來越快,時鐘周期為納秒級,傳輸走線延時的影響十分突出,已影響到器件能否正常工作,必須分析最壞情況下的時序參數。

數字電路時序容差分析主要是分析數字電路間的時序關系,即分析時序余量是否滿足要求。

為了分析該電路的時序容差情況,主要考慮三個方面的因素:器件本身的時序參數容差、PCB布線產生的時序容差、其他干擾產生的時序容差。

器件本身的時序參數容差分析主要是檢查輸出器件端口的時序參數是否滿足輸入器件端口的時序參數要求。并且對器件的時序參數按最壞情況考慮,不是按一般的典型值進行分析。

PCB布線產生的時序容差分析主要是分析器件端口模型、傳輸線拓撲、終端匹配、負載數量等在最壞情況下,采用信號完整性(SI)仿真工具,分析傳輸信號延時和波形,得出對時序的影響。

其他干擾產生的時序容差分析主要是分析電源輸入、電源平面諧振特性、同步開關噪聲、串擾等對信號時序的影響。

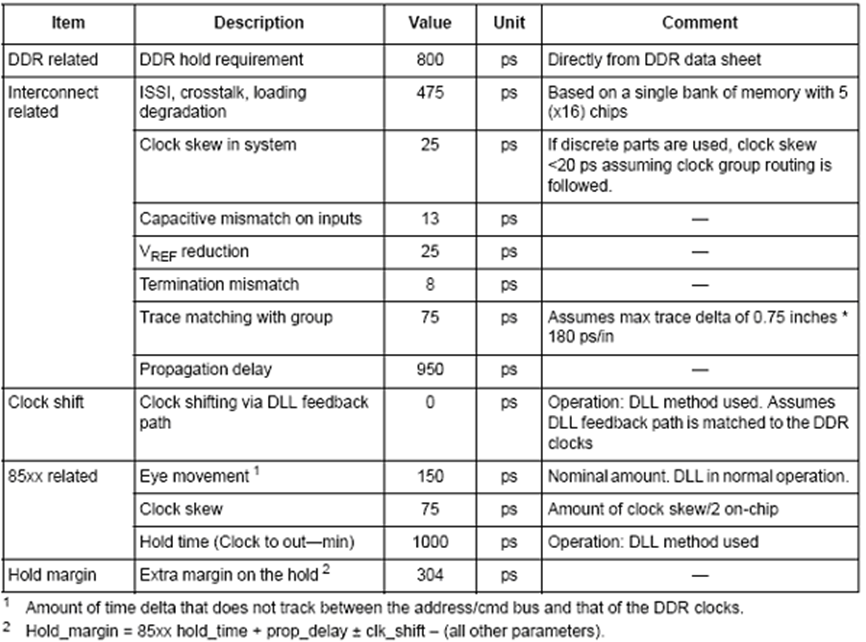

時序參數中最關鍵的是建立時間和保持時間兩個參數。如下圖,是某DDR存儲器的地址、控制、命令信號的保持時間要求,對其中的每個參數都要分析得到它們的最壞情況值,然后代入公式中得到容差值,如果大于0,表示容差滿足要求,如果小于0,表示容差設計不足,需要重新設計。

2) 運用仿真和實驗相結合的方法,準確分析出串擾源和耦合途徑。

串擾是PCB設計時必須關注的可靠性問題。由于被干擾信號上產生的脈沖或毛刺等多是半高電平,在CMOS信號的閾值附近,這樣造成的串擾問題有很大的隨機性,很多不能在出廠前測試出來,在市場上也是時有時無,返修產品有時候很難重復失效現象,分析起來非常困難,這些都是典型的可靠性問題。

串擾分析的方法推薦使用仿真和實驗相結合的方法,既減少實驗次數,又分析得比較全面。比如在分析一個串擾問題時,有些工程師認為是感性串擾,有些認為是容性串擾,有些認為是地彈噪聲。

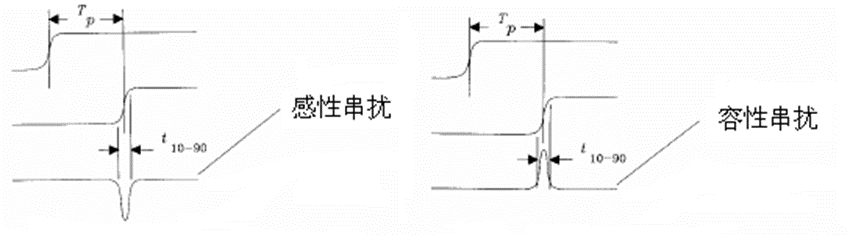

我們知道,感性串擾和容性串擾的相同點是:串擾在遠端為短脈沖,近端為長信號。不同之處是:前向感性串擾和前向容性串擾的極性相反(如下圖),感性串擾產生的是噪聲電壓信號,是串接在被干擾導線上的,而容性串擾產生的是噪聲電流信號,是并接在被干擾導線和地之間的,也就是說,感性串擾隨負載增大而減小,容性串擾隨負載增大而增大。可利用這兩點來辨別容性串擾和感性串擾。如果完全用實驗的方法,那么要用很多的單板來進行割線、飛線、焊接器件等,做多次實驗,但是用仿真的方法就方便經濟得多了,而且幾乎可以想怎么做就怎么做。

在PCB電路仿真中,把被串擾線負載電阻減小10倍時,串擾馬上顯著減小。可見降低對地阻抗可減小串擾大小,這是容性串擾的特征。

另外我們去掉在串擾源和被串擾信號線中間的一塊灌銅地平面,提取出電路的仿真模型,在HSPICE中再次仿真,發現串擾顯著增加。這也是容性串擾的一個證明。注意,這種方法是不能通過實際測試驗證的,只能通過仿真來分析。

同時通過實際測試發現,串擾源的正跳變在被干擾信號線上對應為正的串擾信號,負跳變在被干擾信號線上對應為負的串擾信號。

綜上所述,根據上述串擾形式判別方法,再通過上面幾點的仿真和實測結果,能肯定該串擾為容性串擾占主導。最后針對容性串擾的特點,減小負載電阻,降低了串擾,電路恢復正常。

3) 運用電源完整性(PI)方法,分析電源輸出濾波電路和電源平面設計,保證整個生命周期內的電源都符合要求。

隨著信號頻率的增高和高速系統單板布線越來越密集,無噪聲的電源分配成為了PCB設計的一個主要挑戰。當高速集成電路I/O端口同時改變狀態時,通過電源分配系統(PDS)的紋波噪聲隨頻率的變化而變化,這個噪聲既影響高速設備系統中的IC工作,同時干擾周圍的環境。

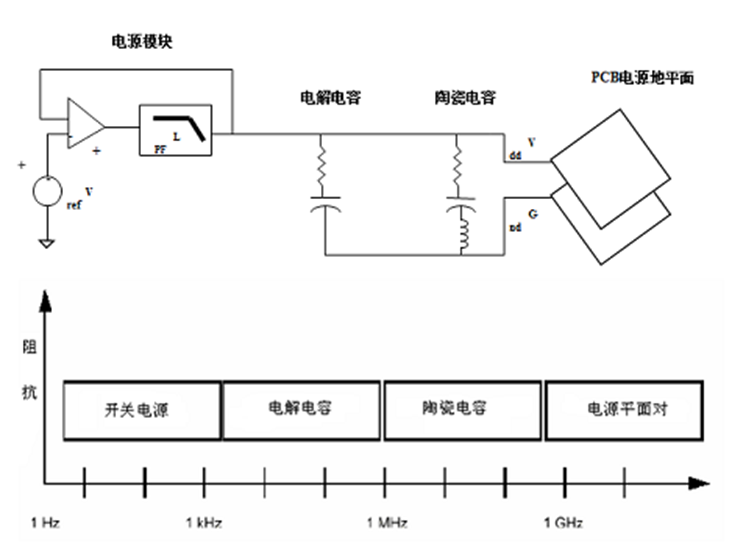

為了確保良好的電源分配,電源分配阻抗必須在一個很寬的頻率范圍內控制在一個要求的目標阻抗下。這可以通過在目標頻率范圍內仔細的考慮開關電源,大電容,陶瓷電容以及電源/地平面對等等來實現。陶瓷電容一般作去耦用,在邏輯開關時給需要大電流的驅動器件提供本地補償。

上圖顯示了在控制電源分配系統(PDS)目標阻抗時各個頻率范圍內哪種器件是最有效的。

可以看出電源完整性工作主要有:確定目標阻抗和選擇合適的PDS組成部分。

確定目標阻抗主要是根據SSN(SimultaneousSwitchingNoise同步開關噪聲)來計算動態電流,然后根據電源變化的要求(一般為3-5%),計算出目標阻抗。這個時候也必須根據可靠性設計規律,考慮最壞情況下的動態電流,所以我們一般是假定所有I/O口同時切換,而且每個端口的輸出電流都取最大值。而電源變化的要求則需要取最小值。

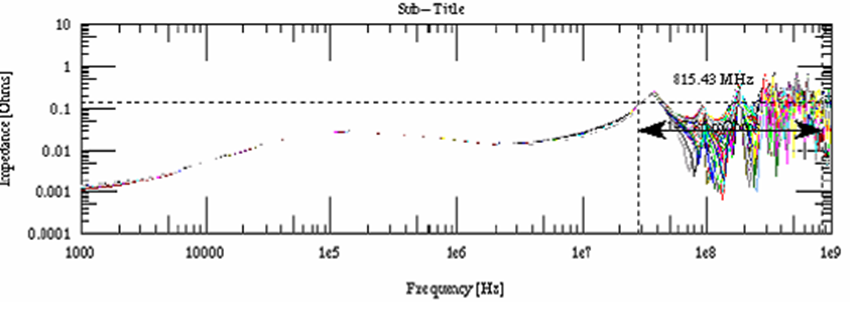

對于PDS的各個部分,特別是電解電容和陶瓷電容,必須考慮器件的容差,因為電容的來料精度一般比較差,20%精度的電容最常使用。同時電容容值受溫度、濕度、氣壓以及壽命的影響也很顯著。我們分析過,考慮上述因素后,電容的容值最大可以變化1倍以上。而且電容內部的分布參數(如ESR、ESL)都有很大容差。所以在PI分析中對電容參數也要選擇多個參數分別分析,得出最壞情況下的PDS阻抗曲線。如下圖所示。

?

可以看出,用可靠性技術來分析電源完整性,不僅要分析典型值下的PDS系統阻抗特性,同時要根據器件在最壞情況下的參數容差,分析PDS的極限阻抗特性,達到在整個生命周期內,電源對產品都不會引起可靠性問題。

-

嵌入式

+關注

關注

5031文章

18680瀏覽量

296185 -

高速電路

+關注

關注

8文章

153瀏覽量

24185 -

電路開發

+關注

關注

0文章

3瀏覽量

3609

發布評論請先 登錄

相關推薦

高速電路開發中有哪些挑戰?

高速電路開發中有哪些挑戰?

評論