滯回比較器(Hysteresis Comparator),也稱為施密特觸發器(Schmitt Trigger)或遲滯比較器,是一種具有特殊功能的比較器電路。與普通比較器不同,滯回比較器在輸入信號接近閾值電壓時,其輸出狀態的變化不是瞬間完成的,而是具有一定的滯后性。這種滯后性通過引入正反饋機制實現,可以有效抑制輸入信號的噪聲干擾,提高系統的穩定性和可靠性。

閾值電壓的定義與重要性

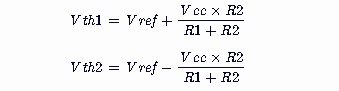

滯回比較器的閾值電壓是指使輸出電平發生跳變的輸入電壓值。由于滯回特性的存在,滯回比較器具有兩個閾值電壓:上升閾值電壓(Vth1)和下降閾值電壓(Vth2)。當輸入電壓從低電平向高電平變化時,達到上升閾值電壓時輸出由低變高;而當輸入電壓從高電平向低電平變化時,必須降至下降閾值電壓以下,輸出才會由高變低。這兩個閾值電壓的差值即為滯回寬度,它決定了比較器對輸入信號噪聲的抑制能力。

閾值電壓的確定方法

1. 電路設計參數

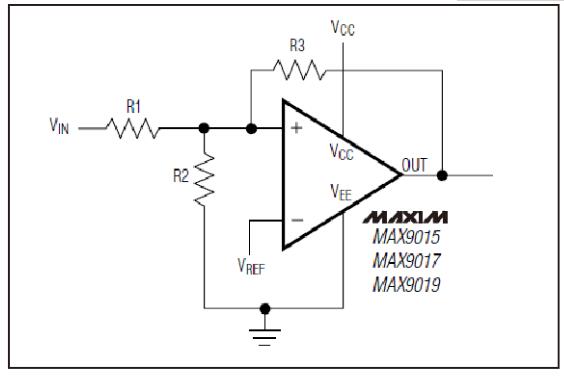

滯回比較器的閾值電壓主要由以下幾個設計參數決定:

- 電源電壓Vcc :決定了比較器的輸出電平范圍。

- 參考電壓Vref :作為輸入信號與運算放大器正輸入端進行比較的基準值,通常閾值電壓會圍繞這個值波動。

- 電阻R1和R2 :這兩個電阻決定了比較器的滯回寬度和閾值電壓。通過調整這兩個電阻的阻值,可以靈活地設置所需的閾值電壓和滯回寬度。

- 運算放大器 :運算放大器的性能直接影響比較器的精度和穩定性。在選擇運算放大器時,需要考慮其輸入偏置電流、輸入偏置電壓、增益帶寬積等參數。

2. 閾值電壓的計算公式

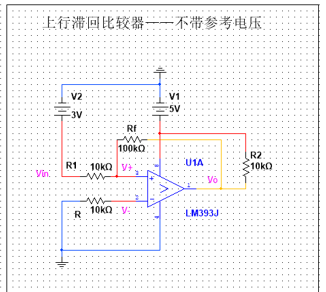

對于同向滯回比較器,其閾值電壓的計算公式如下:

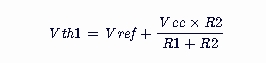

- 上升閾值電壓Vth1 :

這個公式表示當輸入電壓從低電平向高電平變化時,達到這個電壓值時輸出會由低變高。

- 下降閾值電壓Vth2 :

這個公式表示當輸入電壓從高電平向低電平變化時,降至這個電壓值以下時輸出會由高變低。

3. 電路仿真與驗證

在完成電路設計后,通常需要進行電路仿真來驗證比較器的性能是否滿足設計要求。仿真過程中可以觀察輸入電壓和輸出電壓的波形圖,確認閾值電壓的實際值與計算值是否一致。如果發現偏差較大,需要調整電路參數并重新進行仿真驗證。

-

施密特觸發器

+關注

關注

3文章

235瀏覽量

25807 -

輸入信號

+關注

關注

0文章

447瀏覽量

12542 -

閾值電壓

+關注

關注

0文章

73瀏覽量

51371

發布評論請先 登錄

相關推薦

滯回比較器的閾值電壓如何確定?

滯回比較器的閾值電壓如何確定?

評論