一、引言

CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)門(mén)電路是現(xiàn)代數(shù)字電子系統(tǒng)中廣泛使用的關(guān)鍵組件。它們以其低功耗、高噪聲容限和易于集成等優(yōu)點(diǎn)而著稱(chēng)。然而,在設(shè)計(jì)CMOS門(mén)電路時(shí),經(jīng)常會(huì)遇到多余的輸入端問(wèn)題。這些多余的輸入端如果不妥善處理,可能會(huì)對(duì)電路的性能和穩(wěn)定性產(chǎn)生不利影響。因此,了解并掌握CMOS門(mén)電路多余輸入端的處理方法對(duì)于確保電路設(shè)計(jì)的成功至關(guān)重要。

二、CMOS門(mén)電路概述

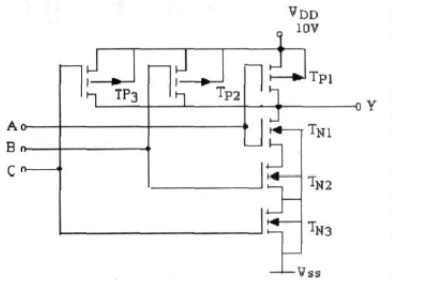

CMOS門(mén)電路由PMOS(P型金屬氧化物半導(dǎo)體)和NMOS(N型金屬氧化物半導(dǎo)體)晶體管組成,通過(guò)互補(bǔ)的方式實(shí)現(xiàn)邏輯功能。CMOS門(mén)電路的主要特點(diǎn)是靜態(tài)功耗極低,因?yàn)楫?dāng)電路處于穩(wěn)定狀態(tài)時(shí),PMOS和NMOS晶體管中只有一個(gè)處于導(dǎo)通狀態(tài),而另一個(gè)則處于截止?fàn)顟B(tài),從而避免了電流的直接流通。

三、多余輸入端的影響

在CMOS門(mén)電路中,多余的輸入端如果不接任何信號(hào)或處理不當(dāng),可能會(huì)產(chǎn)生以下幾種影響:

- 邏輯功能不確定 :多余的輸入端如果處于浮空狀態(tài)(即未接任何信號(hào)),其電平狀態(tài)可能不穩(wěn)定,導(dǎo)致電路的邏輯功能無(wú)法確定。

- 功耗增加 :在某些情況下,多余的輸入端如果接入高電平或低電平信號(hào),可能會(huì)增加電路的靜態(tài)功耗。

- 噪聲敏感性增加 :未處理的輸入端可能更容易受到外部噪聲的干擾,影響電路的穩(wěn)定性和可靠性。

四、多余輸入端的處理方法

針對(duì)CMOS門(mén)電路多余輸入端的問(wèn)題,可以采取以下幾種處理方法:

1. 接地處理

將多余的輸入端接地是一種常見(jiàn)的處理方法。這種方法適用于CMOS或非門(mén)、或非門(mén)等邏輯門(mén)電路,因?yàn)樗鼈兊倪壿嫻δ茉谳斎攵私拥貢r(shí)不會(huì)受到影響。接地處理可以有效地防止輸入端浮空帶來(lái)的不穩(wěn)定性和噪聲干擾。

實(shí)施步驟 :

- 使用導(dǎo)線將多余的輸入端與地(GND)相連。

- 確保接地連接可靠,避免接觸不良或開(kāi)路現(xiàn)象。

2. 接電源處理

對(duì)于CMOS與門(mén)、與非門(mén)等邏輯門(mén)電路,如果多余的輸入端接入高電平信號(hào)對(duì)邏輯功能無(wú)影響,則可以將多余的輸入端接電源(VCC)。這種方法可以確保輸入端處于穩(wěn)定的高電平狀態(tài),避免浮空帶來(lái)的問(wèn)題。

實(shí)施步驟 :

3. 并接使用

在某些情況下,可以將CMOS門(mén)電路多余的輸入端與正在使用的輸入端并接在一起使用。這種方法適用于輸入端數(shù)量較多的情況,可以簡(jiǎn)化電路設(shè)計(jì)并減少元件數(shù)量。但需要注意的是,并接使用時(shí)要確保不會(huì)改變電路的邏輯功能。

實(shí)施步驟 :

- 使用導(dǎo)線將多余的輸入端與正在使用的輸入端相連。

- 驗(yàn)證并接后的電路邏輯功能是否符合設(shè)計(jì)要求。

4. 接入反相器

對(duì)于需要具有多種輸入和輸出的復(fù)雜電路,可以考慮將CMOS門(mén)電路多余的輸入端接入一個(gè)反相器。通過(guò)反相器的作用,可以將多余的輸入端反相輸出,從而實(shí)現(xiàn)其他功能。這種方法需要額外的元件和布線,但可以增加電路的靈活性和功能性。

實(shí)施步驟 :

- 選擇合適的反相器元件。

- 使用導(dǎo)線將多余的輸入端與反相器的輸入端相連。

- 將反相器的輸出端連接到需要的位置。

5. 留空不接

在某些特殊情況下,如果CMOS門(mén)電路的多余輸入端確實(shí)不需要使用,并且不會(huì)對(duì)電路的邏輯功能和穩(wěn)定性產(chǎn)生影響,也可以選擇留空不接。但需要注意的是,這種方法需要謹(jǐn)慎使用,因?yàn)榱艨盏妮斎攵丝赡軙?huì)受到外部噪聲的干擾。

實(shí)施步驟 :

- 確認(rèn)多余的輸入端確實(shí)不需要使用。

- 確保留空的輸入端不會(huì)受到外部噪聲的干擾。

五、注意事項(xiàng)

在處理CMOS門(mén)電路多余輸入端時(shí),需要注意以下幾點(diǎn):

- 了解電路特性 :在處理之前,需要充分了解CMOS門(mén)電路的特性,包括其邏輯功能、輸入電壓范圍、功耗等。

- 避免干擾 :在連接和處理輸入端時(shí),要注意避免引入外部噪聲和干擾信號(hào)。

- 選擇適當(dāng)?shù)脑?/strong> :在選擇限流電阻、反相器等元件時(shí),要根據(jù)電路的實(shí)際需求進(jìn)行選擇,確保元件的規(guī)格和性能符合設(shè)計(jì)要求。

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27064瀏覽量

216504 -

數(shù)字電子

+關(guān)注

關(guān)注

6文章

104瀏覽量

21160 -

組件

+關(guān)注

關(guān)注

1文章

505瀏覽量

17807 -

CMOS門(mén)電路

+關(guān)注

關(guān)注

0文章

6瀏覽量

4900

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

CMOS和TTL集成門(mén)電路多余輸入端的處理方法

CMOS和TTL集成門(mén)電路多余輸入端如何處理?

CMOS電路多余輸入端懸空,會(huì)造成邏輯混亂,該如何處理?

CMOS和TTL集成門(mén)電路多余輸入端如何處理?

[轉(zhuǎn)]CMOS器件空閑管腳的處理 精選資料分享

二(2)輸入端CMOS或非門(mén)電路

ttl門(mén)電路中輸入端負(fù)載特性

關(guān)于TTL和CMOS門(mén)電路的邏輯輸入端輸入關(guān)系的區(qū)別/總結(jié)

cmos門(mén)電路多余輸入端的處理方法

cmos門(mén)電路多余輸入端的處理方法

評(píng)論