借助由仿真驅(qū)動(dòng)的虛擬合規(guī)性測(cè)試解決方案,采用更智能、更精簡(jiǎn)的工作流程,提高 PCIe 設(shè)計(jì)的工作效率

具有設(shè)計(jì)探索和報(bào)告生成能力,可加快小芯片的信號(hào)完整性分析以及UCIe 合規(guī)性驗(yàn)證,從而幫助設(shè)計(jì)師提高工作效率,縮短新產(chǎn)品上市時(shí)間

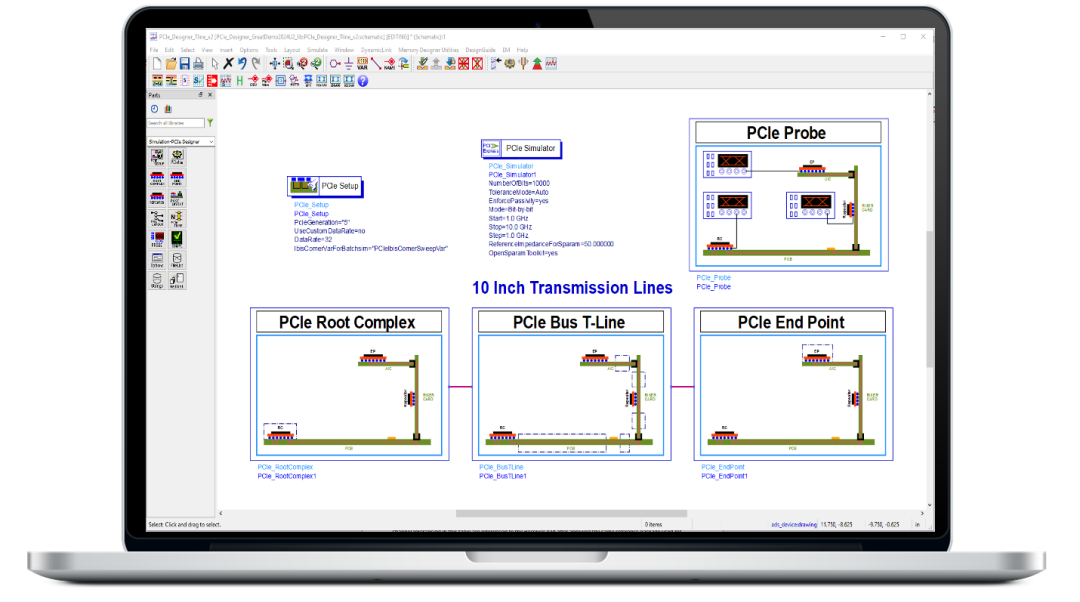

是德科技(Keysight Technologies,Inc.)宣布推出System Designer for PCIe,這是其先進(jìn)設(shè)計(jì)系統(tǒng) (ADS) 軟件套件中的一款新產(chǎn)品,支持基于行業(yè)標(biāo)準(zhǔn)的仿真工作流程,可用于仿真高速、高頻的數(shù)字設(shè)計(jì)。System Designer for PCIe 是一種智能的設(shè)計(jì)環(huán)境,用于對(duì)最新的PCIe Gen5 和 Gen6 系統(tǒng)進(jìn)行建模和仿真。是德科技還在改進(jìn)其電子設(shè)計(jì)自動(dòng)化平臺(tái),通過(guò)為現(xiàn)有的 Chiplet PHY Designer 工具增加新功能,評(píng)估Chiplet中芯片到芯片的鏈路裕度性能,并對(duì)電壓傳遞函數(shù) (VTF) 是否符合相關(guān)參數(shù)標(biāo)準(zhǔn)進(jìn)行測(cè)量。

System Designer for PCIe 是一種智能的設(shè)計(jì)環(huán)境

用于對(duì)最新PCIe Gen5 和 Gen6 系統(tǒng)進(jìn)行建模和仿真

PCIe 憑借其高速數(shù)字傳輸能力、出色的可擴(kuò)展性和適應(yīng)能力,成為廣泛適用于電子行業(yè)各領(lǐng)域的重要通用接口標(biāo)準(zhǔn)。它的用途十分廣泛,范圍涵蓋從日常生活中的消費(fèi)電子設(shè)備到高性能計(jì)算和關(guān)鍵基礎(chǔ)設(shè)施系統(tǒng)中的專(zhuān)業(yè)應(yīng)用。 復(fù)雜的 PCIe 設(shè)計(jì)支持多鏈路和多通道系統(tǒng),主要涉及 RootComplex 和 End-Point 之間的復(fù)雜分析設(shè)置,有時(shí)還會(huì)包括中繼器。通常,設(shè)計(jì)人員需要投入大量時(shí)間準(zhǔn)備仿真工作,卻很容易出錯(cuò)。在仿真過(guò)程中,往往缺乏針對(duì)特定供應(yīng)商的算法建模接口(AMI)仿真模型,而實(shí)際上在設(shè)計(jì)周期的早期階段就需要使用這些模型來(lái)探索設(shè)計(jì)空間。設(shè)計(jì)師還需要確保他們的原型設(shè)計(jì)能夠在硬件制造開(kāi)啟之前通過(guò)合規(guī)性測(cè)試。能夠提升工作效率、優(yōu)化工作流程和提高合規(guī)性

System Designer for PCIe能夠利用一種智能的設(shè)計(jì)環(huán)境,自動(dòng)設(shè)置多鏈路、多通道和多層級(jí)(PAM4)的 PCIe 系統(tǒng)。它簡(jiǎn)化了仿真設(shè)置步驟,縮短了從首次探索到發(fā)現(xiàn)更深層次問(wèn)題的時(shí)間。

PCIe AMI 建模器支持 NRZ 和 PAM4 調(diào)制,能夠快速生成 PCIe 系統(tǒng)分析所需的 AMI 模型。AMI 模型生成器為設(shè)計(jì)師提供了一套向?qū)降?AMI 模型生成工作流程,可快速創(chuàng)建發(fā)射器(Tx)和接收器(Rx)模型。

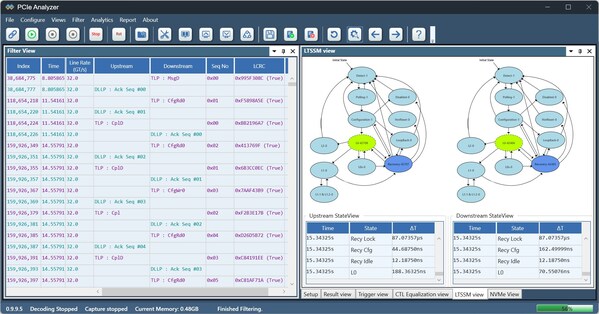

采用經(jīng)過(guò)簡(jiǎn)化的、由仿真驅(qū)動(dòng)的虛擬合規(guī)性測(cè)試,使得設(shè)計(jì)人員能夠確保設(shè)計(jì)的質(zhì)量。高度集成的、由仿真驅(qū)動(dòng)的 PCIe 合規(guī)性測(cè)試工作流程可最大限度地減少設(shè)計(jì)迭代,縮短產(chǎn)品上市時(shí)間,從而降低設(shè)計(jì)成本。

Chiplet PHY Designer的增強(qiáng)功能

Chiplet PHY Designer 是 EDA 行業(yè)首款針對(duì)通用小芯片互聯(lián)技術(shù) (UCIe) 標(biāo)準(zhǔn)的仿真解決方案,有助于評(píng)估和預(yù)測(cè)芯片到芯片的鏈路裕量、用于通道合規(guī)性分析的 VTF 以及前向時(shí)鐘的性能。Chiplet PHY Designer 具有全新的設(shè)計(jì)探索和報(bào)告生成能力,可加速信號(hào)完整性分析和合規(guī)性驗(yàn)證,從而提高設(shè)計(jì)人員的工作效率,縮短新產(chǎn)品的上市時(shí)間。

是德科技EDA 事業(yè)部高速數(shù)字產(chǎn)品線總監(jiān) Hee-Soo Lee 表示:“我們將持續(xù)拓展由標(biāo)準(zhǔn)驅(qū)動(dòng)的工作流程解決方案,從而為客戶提供支持。與同類(lèi)產(chǎn)品相比,我們的高速數(shù)字產(chǎn)品組合能夠?yàn)樾盘?hào)完整性分析和合規(guī)性測(cè)試驗(yàn)證提供更準(zhǔn)確、更先進(jìn)的仿真軟件,在 EDA 行業(yè)處于領(lǐng)先地位。PCIe 和 UCIe 等數(shù)字標(biāo)準(zhǔn)對(duì)于保障電子系統(tǒng)的性能而言至關(guān)重要。設(shè)計(jì)師在工作過(guò)程中使用是德科技的 PCIe 和 UCIe 仿真解決方案,可以縮短開(kāi)發(fā)周期,節(jié)省大量時(shí)間和成本。”

關(guān)于是德科技

是德科技(NYSE:KEYS)啟迪并賦能創(chuàng)新者,助力他們將改變世界的技術(shù)帶入生活。作為一家標(biāo)準(zhǔn)普爾 500 指數(shù)公司,我們提供先進(jìn)的設(shè)計(jì)、仿真和測(cè)試解決方案,旨在幫助工程師在整個(gè)產(chǎn)品生命周期中更快地完成開(kāi)發(fā)和部署,同時(shí)控制好風(fēng)險(xiǎn)。我們的客戶遍及全球通信、工業(yè)自動(dòng)化、航空航天與國(guó)防、汽車(chē)、半導(dǎo)體和通用電子等市場(chǎng)。我們與客戶攜手,加速創(chuàng)新,創(chuàng)造一個(gè)安全互聯(lián)的世界。

-

仿真

+關(guān)注

關(guān)注

50文章

3938瀏覽量

132811 -

PCIe

+關(guān)注

關(guān)注

14文章

1147瀏覽量

81632 -

PHY

+關(guān)注

關(guān)注

2文章

284瀏覽量

51488 -

是德科技

+關(guān)注

關(guān)注

19文章

825瀏覽量

81294

原文標(biāo)題:是德科技推出System Designer和Chiplet PHY Designer,優(yōu)化基于數(shù)字標(biāo)準(zhǔn)的仿真工作流程

文章出處:【微信號(hào):KeysightGCFM,微信公眾號(hào):是德科技快訊】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Prodigy Technovations推出功能強(qiáng)大的PCIe Gen5協(xié)議分析儀

新思科技PCIe 7.0驗(yàn)證IP(VIP)的特性

安費(fèi)諾高速電纜解決方案滿足PCIe、EDSFF、OCP規(guī)范和機(jī)架式電源要求

新思科技推出業(yè)界首款PCIe 7.0 IP解決方案

新思科技發(fā)布PCIe 7.0 IP解決方案,賦能AI與HPC前沿設(shè)計(jì)

新思科技推出業(yè)界首款PCIe 7.0 IP解決方案

是德科技聯(lián)合新思科技、Ansys推出了一個(gè)全新的集成射頻設(shè)計(jì)遷移流程

是德科技與ETS Lindgren合作推出NB-NTN OTA測(cè)試解決方案

是德科技推出QuantumPro解決方案

重磅!《兆芯&中科方德生態(tài)聯(lián)合解決方案》全新發(fā)布

是德科技將推出為汽車(chē)行業(yè)PCBA測(cè)試設(shè)計(jì)的解決方案

虹科Safran與是德科技合作推出基于GNSS技術(shù)的5G LBS方案

超高性能和無(wú)與倫比的靈活性!Safran與是德科技合作推出基于GNSS技術(shù)的5G LBS方案

虹科Safran與是德科技合作推出基于GNSS技術(shù)的5G LBS方案

Safran與是德科技合作推出基于GNSS技術(shù)的5G LBS方案

是德科技推出PCIe和UCIe仿真解決方案

是德科技推出PCIe和UCIe仿真解決方案

評(píng)論