一、規則設置

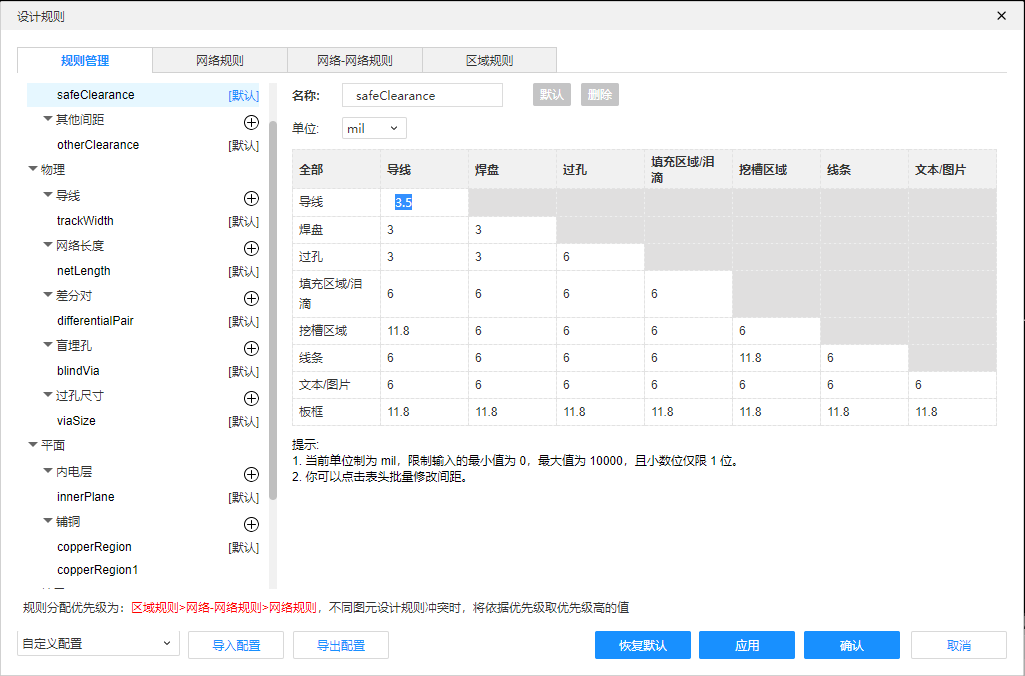

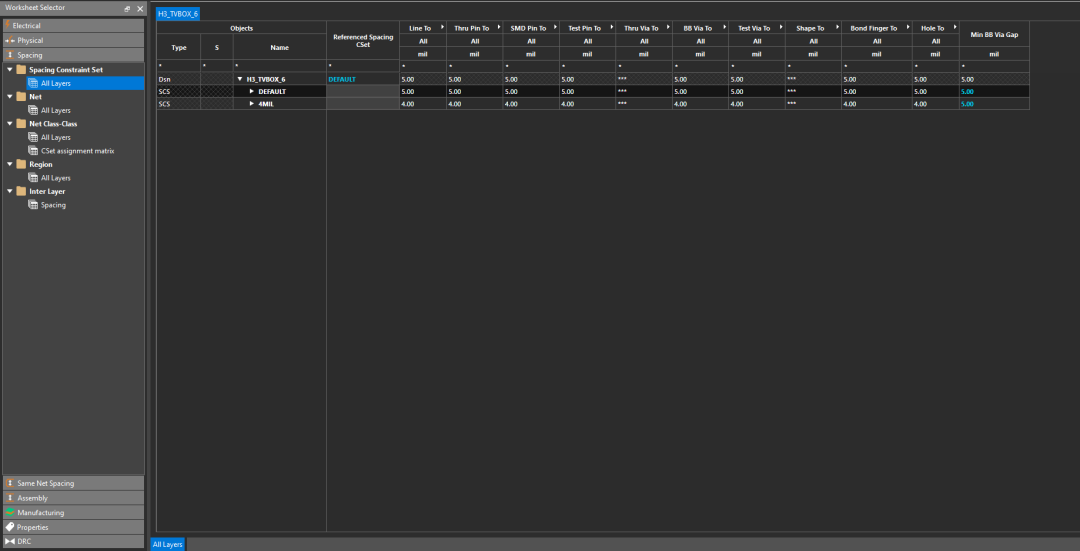

使用EDA設計時,首先進行PCB的規則設置,一般規則設置比較重要的有間距設置、物理規則、平面規則、網絡設置。分別展示立創EDA和Allegro的規則設置界面。

立創EDA的規則設計更直觀,而Allegro的規則設置則更全面。

具體的規則設置則是根據當前繪制PCB來決定的,同時需要參考板廠生產工藝給定的參數來進行設置。如嘉立創打板時,多層板線距要求大于3.5mil時不額外收取工藝費,這時就需要在安全距離的導線到導線的距離中設置為至少3.5mil/0.089mm。

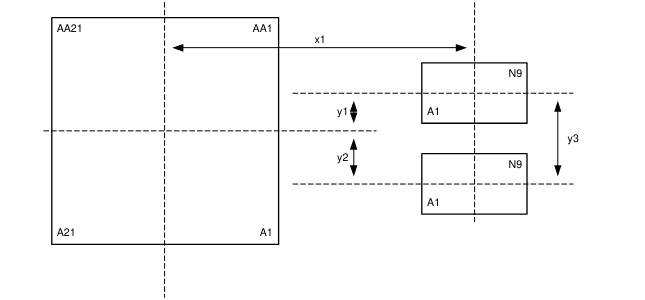

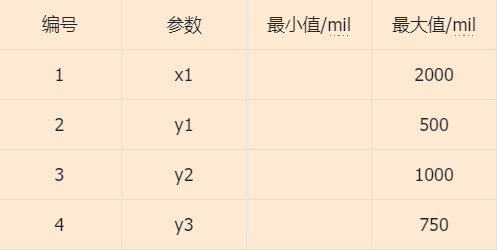

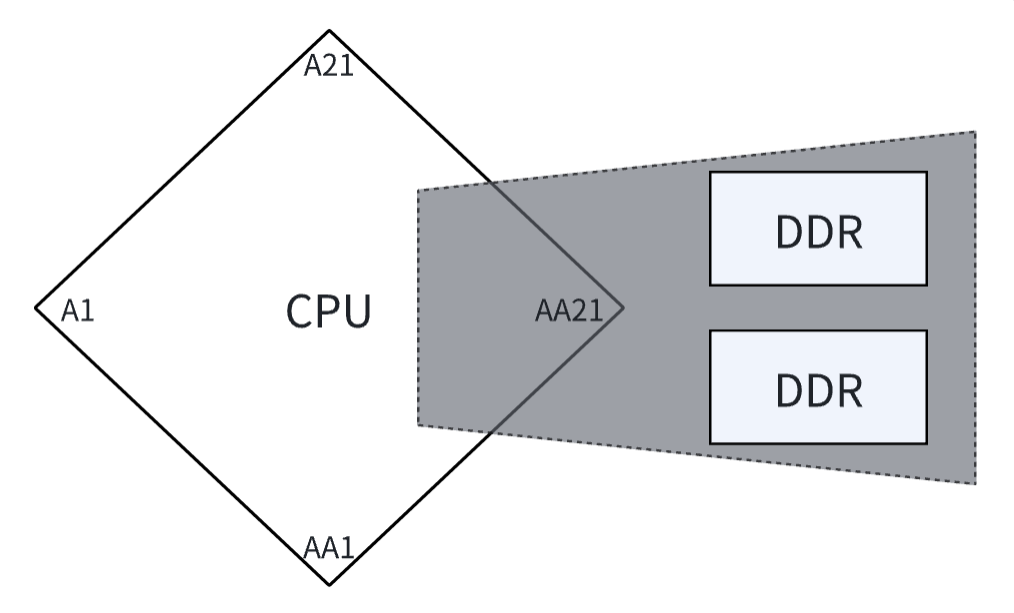

在這些模塊中CPU和DDR均為BGA封裝,此部分布線有難度,應當優先處理。CPU和DDR的布局可參照下圖。

本圖只是示意圖,放置的最終目的是限制最大布線長度并流出適當的布線空間。

用于DDR電路的區域必須與其他信號隔離開,如下圖所示。這個禁止區域的大小應該根據DDR的放置和布線決定。對于非DDR信號,不能在禁止區域內的DDR信號層上走線。只有在通過接地層與DDR信號層隔離開來的其他層上布線時,非LPDDR才能在該區域中布線。一般走線時應該盡量將該區域繞過。

如上圖所示,本次布局CPU和DDR采用此布局,灰色部分則是DDR隔離區,DDR信號可以在這里放置,非DDR則最好不要經過這個區域,并且使用包地的方式進一步隔離該區域。

三、CPU及DDR布線要點

走線時應該盡量滿足3W規則,即兩條導線中心的距離至少為線寬的三倍(如導線線寬5mil,兩條導線中心距離應為15mil,兩導線邊距則是10mil,即2W)。這樣布線能有效防止信號之間的串擾。

布信號線時應注意阻抗匹配以及等長布線。等長布線時先將各組線分組設置,這個功能在立創EDA和Cadence中均可實現,詳見另一篇文檔。阻抗匹配:單端50Ω,差分100Ω。計算阻抗匹配的工具有很多,如果是在嘉立創進行繪制可以直接使用嘉立創阻抗計算神器,也可以使用如ICD Stackup Planner、SI9000等專業阻抗計算軟件。

同組信號中優先拉差分信號線,同時需要留足空間以方便后續做等長。

設置參考平面,這個參考平面一般為地平面,因此設計時需定義好疊層。信號線盡量不走頂層和底層,而是走中間層,因為中間層的數據傳輸速率相較于頂層和底層快,頂層和底層少走線也利于擺放器件。

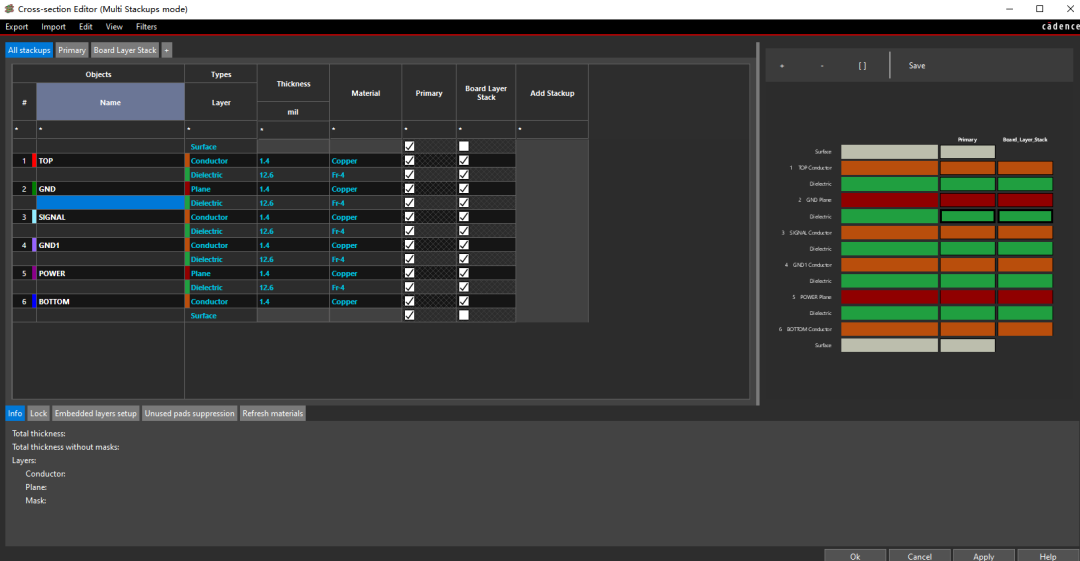

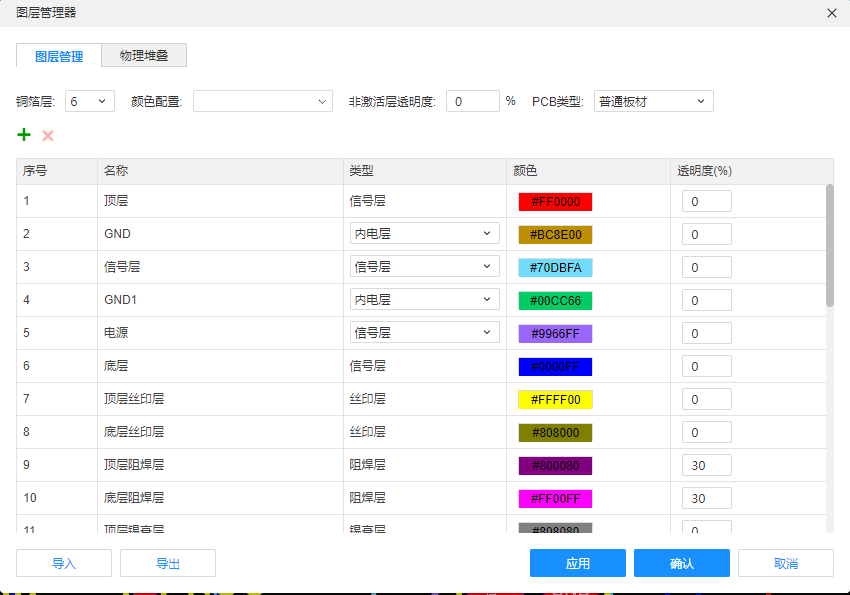

分別展示Allegro和立創EDA的疊層管理器,六層板的疊層設計一般為信號層——地平面——信號層——地平面——電源層——信號層。這樣設置可以保證信號線的參考平面總為地平面。

四、電源部分布局布線要點

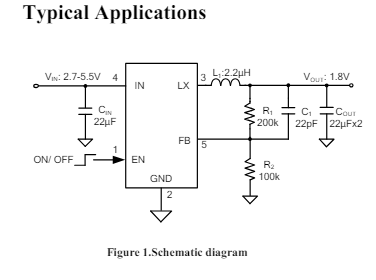

本設計電源較多且多使用DCDC電源芯片,因此電源部分布線一定要注意一下事項:典型電路:一般典型電路都可以從數據手冊中找到,如本次使用的DCDC電源芯片SY8089A:

設計時需要參考官方手冊給出的典型電路來選取各元器件的值。同時,部分元器件的數值選取可以參考數據手冊中給出的計算公式計算,以匹配自己設計的電路。

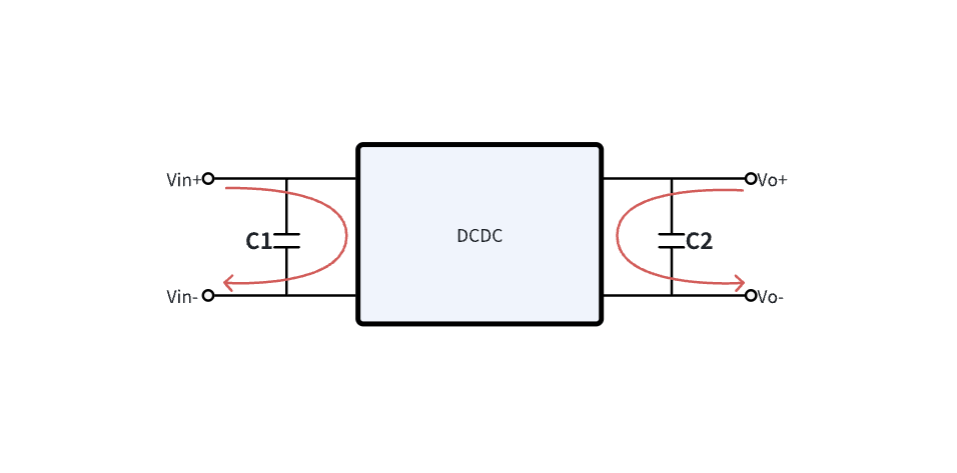

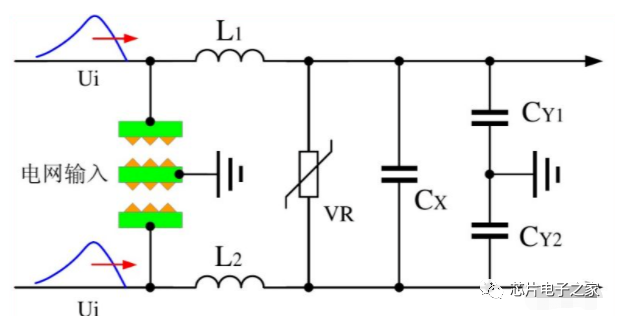

電流路徑:

回流路徑如紅色箭頭所示,其中C1、C2是輸入和輸出電容,這兩個電容的作用為減小輸入電流和輸出電壓的紋波。

回流路徑如紅色箭頭所示,其中C1、C2是輸入和輸出電容,這兩個電容的作用為減小輸入電流和輸出電壓的紋波。

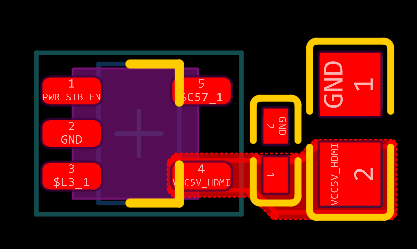

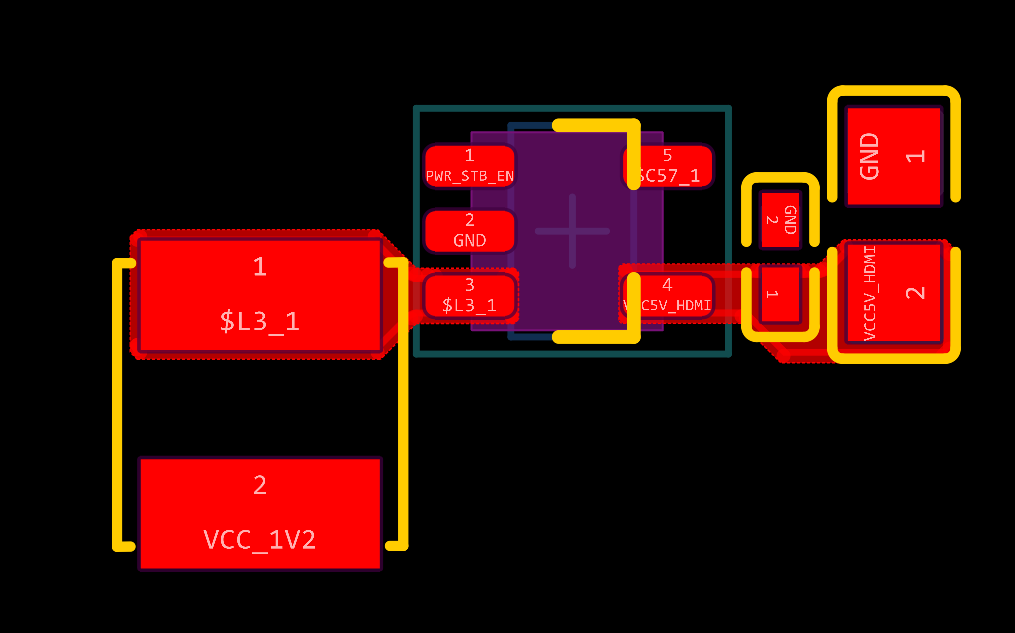

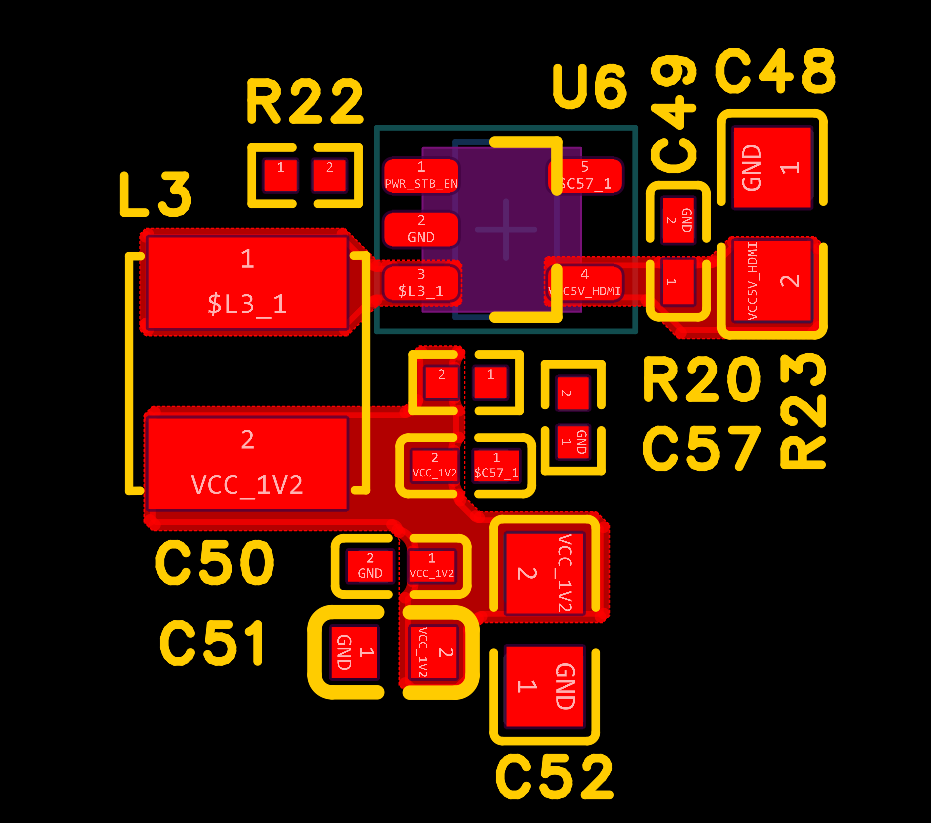

器件布局:

其中輸入電容對于任何降壓型轉換器件來說都是實現其可靠操作的重要器件。因此,在放置完IC后應該首先安放輸入電容。放置了輸入電容后立即布線將之與IC連接,這樣在其走線排布的路徑中就不會有其他的器件及走線穿過了。輸入電容的電源與接地之間以及IC的VIN和GND之間的額外寄生電感將由于開關動作而產生過大的電壓尖峰(V=L*di/dt),這個電壓尖峰有可能導致IC故障。

所以,輸入電容應該盡可能靠近IC引腳,且走線盡可能粗、短,利用如此連接方式盡可能的減小寄生電感。

在布局中,第二重要的是電感。電感盡量放置在靠近IC處,并保持盡可能小的SW節點鋪銅面積。連接SW節點的所有銅箔相當于電容的一塊極板,而另一塊極板則是電路中的每一點,這個電容是一個噪聲耦合路徑。通過使SW節點很小,可以最大限度的減少電容極板的面積并減小耦合。

輸出電容是完成功率布線的最后一步。其為系統中連接至電源接地端的最終器件,而且它的擺放位置旨在盡可能縮短從電感器背部至電源接地的距離。輸出電容如果擺放不當通常會引起不良的輸出電壓調節。

每種功率器件的安置和布線以盡量縮短它們之間的距離為宗旨。使這些環路面積保持很小可實現SMPS(即開關模式電源)的最佳運作。

除了功率器件外還有一些小信號器件,如:EN(使能)、FB(反饋)、PG(檢測)等。噪聲較高的功率器件及其節點產生噪聲,而模擬小信號器件容易受到噪聲干擾。所以應該采用簡短和直接的布線將這些器件布局在靠近IC的地方,以盡量防止噪聲對其的影響。特別需要注意,必須盡可能使FB節點保持小巧,以最大限度地減少噪聲并提供優良的輸出電壓調節能力。

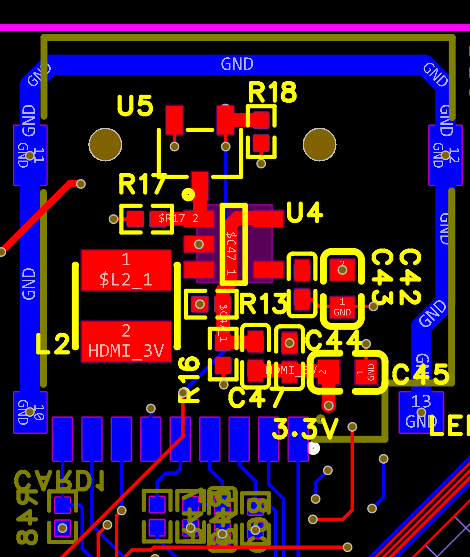

五、HDMI布局布線要點

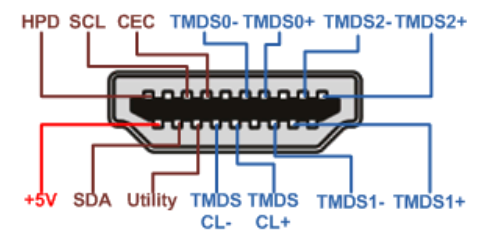

HDMI連接器中有四對最小化傳輸差分數字信號(TMDS)通道;熱插拔檢測 (HPD) 通道,可檢測何時建立連接;消費 類電子控制 (CEC) 通道,允許用戶通過 HDMI 控制器件;實用通道,用于 HDMI 以太網或音頻返回通道;SDA 和 SCL 通道,可提供 I2C 控制;以及最后一個通道,可提供 5V 電源。

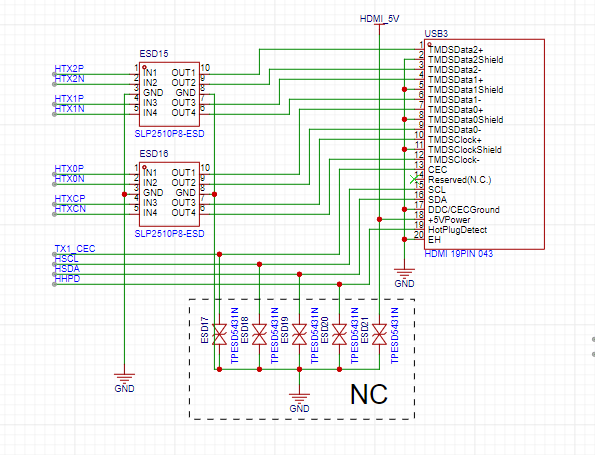

為了防止ESD故障,可以通過 HDMI 連接器將 5V 工作電壓、TVS 二極管放置在各通道上。此外TMDS通道為高速線(對于 HDMI 2.0 而言可達18Gbps),放置在這些高速布線上的 ESD 保護二極管要求電容足夠低,以保持信號完整性并滿 足 HDMI 合規標準。

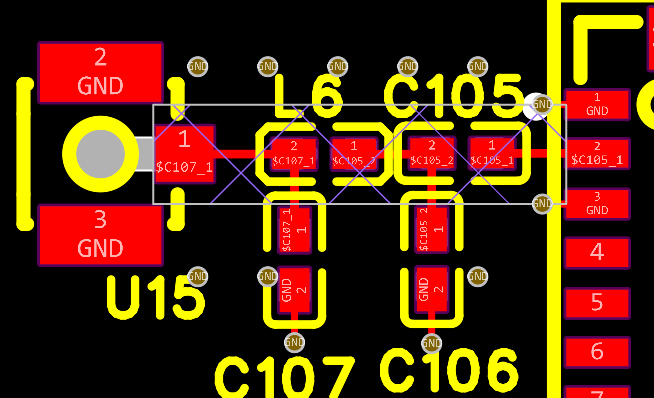

ESD器件在布局上應該盡可能靠近HDMI引腳,但是也不能太近,考慮到焊接,其距離最好控制在烙鐵頭能夠焊接的距離上(1.5mm左右);

HDMI中六個TMDS通道為三組差分信號,在布線時按照差分線規則引線,換層布線盡量不要超過兩次,盡可能不打孔換層。差分對走線需要做100Ω阻抗匹配,阻抗匹配在CPU及DDR布線中有提到。使用堅實的電源層和接地層來實現 100Ω 阻抗控制,以及電源噪聲最小化。即差分走線下面應該是完整的參考平面。

HDMI接口的5V電源靠近接口來放置即可,不宜太遠;

HDMI走線<3000mil,并行走到連接處即可,不要使用蛇形走線;

差分對內等長誤差<200mil,差分對間盡量等長,誤差<1000mil即可;

盡可能使HDMI連接器和器件之間的電氣長度保持最短,從而使衰減最小化。

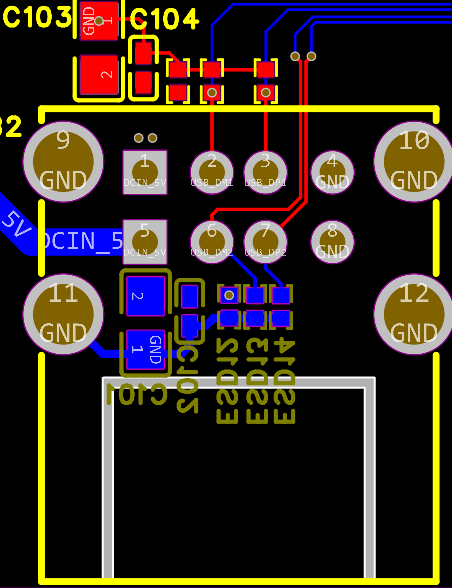

六、WIFI模塊布局布線要點

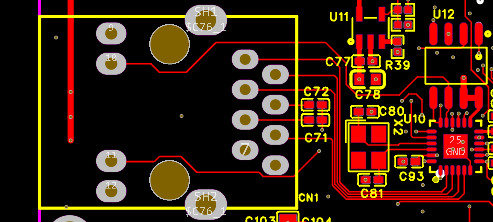

Linux開發板中WIFI使用模塊RTL8189ETV,因此布局布線重點在天線的放置位置處。模塊需要自己搭建射頻電路(RFIOP)。

為保證損耗最小,RF走線盡量短,元件之間盡量排緊湊一些;RF走線盡量走直線,不要使用直角走線,走線寬度以及走線和外圍 GND 的間距推薦0.5mm。因PCB 板材和介質會影響 RF 走線阻抗,為保證 RF 走線的阻抗為 50Ω,可以適當調整走線寬度以及走線和外圍 GND 的間距。

RF盡量一字走線,如果空間受限無法一字走線,可使用L形走線,但不能使用U形走線。

RF走線四周一定要包地處理,上下層通過GND過孔連接。

射頻部分布局盡量靠近板邊,盡可能遠離強輻射信號(高速信號等)。

七、EMAC布局布線要點

Linux開發板中使用了兩個以太網接口,其中一個使用以太網轉換芯片。以太網轉換芯片PHY和變壓器之間的距離也應該盡可能的短,距離一般不超過127mm,若RJ45接口自帶變壓器,則以太網轉換芯片盡可能的靠近RJ45接口放置。時鐘電路應當盡可能的靠近以太網轉換芯片,遠離電路板的邊緣以及其它高頻信號、IO端口走線和其它磁性元器件。

八、TF卡布局布線要點

VCC_SD的電容需要靠近卡座引腳放置進行濾波,遵循先大后小的原則。

TF卡盡量放置在板邊,方便插拔,ESD器件要靠近TF卡來放置,走線需要先經過ESD器件再進入SD卡,不要打孔穿;

TF卡走線為單端線,控制阻抗50歐姆;

所有的信號線盡量走在同一層,這樣有利于信號的一致性,走線與高頻信號隔開,空間準許的情況下,單根包地,空間緊張的情況下整組進行包地處理,走線需要有完整的參考平面;

TF卡的時鐘信號,與其他信號線的間距保證20mil左右,有空間的情況下,包地處理;

組內數據線不要相差太大,需要控制400mil以內,走線總長度不要太長盡量控制在317.5mm之內,以提高穩定性和兼容性。

在打孔換層的地方加回流地過孔,縮短回流了路徑。

九、USB布局布線要點

USB應該接口靠近板邊或結構定位放置,伸出板邊一定位置(直插除外),方便插拔;

注意ESD和USB的距離,留有一定的的間距,考慮后焊的情況;

在布局時,盡量使差分線路最短,以縮短差分線距離;

USB要走差分,阻抗控制為90歐姆,并包地處理,總長度最好不要超過1800mil;

盡可能縮短走線長度,優先考慮對高速USB差分(RX、TX差分)的布線,USB差分走線在走線的時候,盡可以有的減少換層過孔,從而可以更好的做到阻抗的控制,避免信號的反射。

-

DDR

+關注

關注

11文章

692瀏覽量

64781 -

布線

+關注

關注

9文章

741瀏覽量

84185 -

PCB布局

+關注

關注

9文章

178瀏覽量

27773 -

EDA設計

+關注

關注

1文章

47瀏覽量

13645

發布評論請先 登錄

相關推薦

PCB規劃/布局和布線的設計技巧和要點

PCB布局布線11個要點資料下載

干貨!PCB布局布線九大最全要點

干貨!PCB布局布線九大最全要點

評論