電壓降是電路中的一個重要概念,它指的是在電路中,電流通過電阻或其他元件時,電勢能的降低。電壓降是整個回路的,因為它涉及到電路中所有元件的電勢變化。

電壓降概述

1.1 電壓降的定義

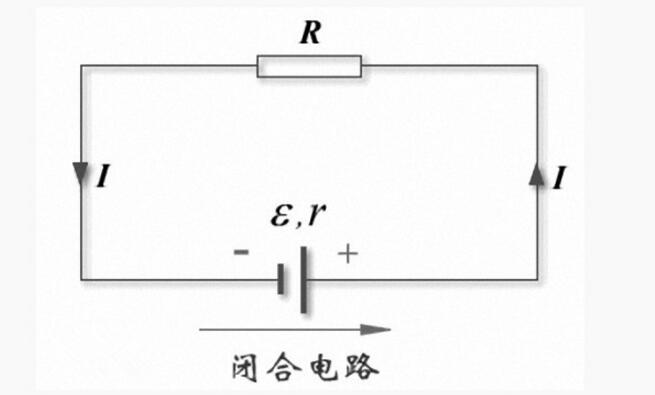

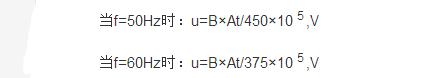

電壓降是指在電路中,電流通過電阻或其他元件時,電勢能的降低。電壓降通常用伏特(V)作為單位。在直流電路中,電壓降是沿著電流方向的電勢降低;在交流電路中,電壓降是瞬時電勢的變化。

1.2 電壓降的物理意義

電壓降是電路中電能轉換為其他形式能量(如熱能、機械能等)的過程。當電流通過電阻時,電能被轉化為熱能,導致電阻的溫度升高。在其他元件中,電壓降可能轉化為機械能、光能等。

1.3 電壓降與電流、電阻的關系

電壓降與電流和電阻之間存在密切的關系。根據歐姆定律,電壓降(V)等于電流(I)乘以電阻(R),即 V = I × R。這意味著在給定的電阻下,電流越大,電壓降就越大;反之亦然。

電壓降的計算方法

2.1 串聯電路中的電壓降

在串聯電路中,所有元件的電壓降之和等于電源電壓。設電路中有n個電阻,分別為R1、R2、...、Rn,電流為I,則總電壓降V_total = I × (R1 + R2 + ... + Rn)。

2.2 并聯電路中的電壓降

在并聯電路中,所有元件的電壓降相等,等于電源電壓。設電路中有m個電阻,分別為R1、R2、...、Rm,電源電壓為V_source,則每個電阻上的電壓降V_drop = V_source。

2.3 復雜電路中的電壓降

對于包含多個串聯和并聯部分的復雜電路,可以使用節點電壓法或環路電流法來計算電壓降。節點電壓法是將電路中的節點設為未知數,然后根據歐姆定律和基爾霍夫電流定律列出方程組,求解節點電壓。環路電流法是將電路中的環路設為未知數,然后根據歐姆定律和基爾霍夫電壓定律列出方程組,求解環路電流。

電壓降的應用

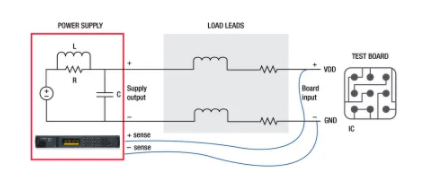

3.1 電源設計

在電源設計中,電壓降是一個重要的考慮因素。電源需要提供足夠的電壓降,以滿足負載的需求。同時,電源的效率也與電壓降有關。降低電壓降可以提高電源的效率,減少能量損失。

3.2 電子設備設計

在電子設備設計中,電壓降對電路的性能和穩定性有重要影響。例如,在放大器設計中,電壓降會影響放大器的增益和線性度。在數字電路設計中,電壓降會影響邏輯門的閾值電壓,從而影響電路的可靠性。

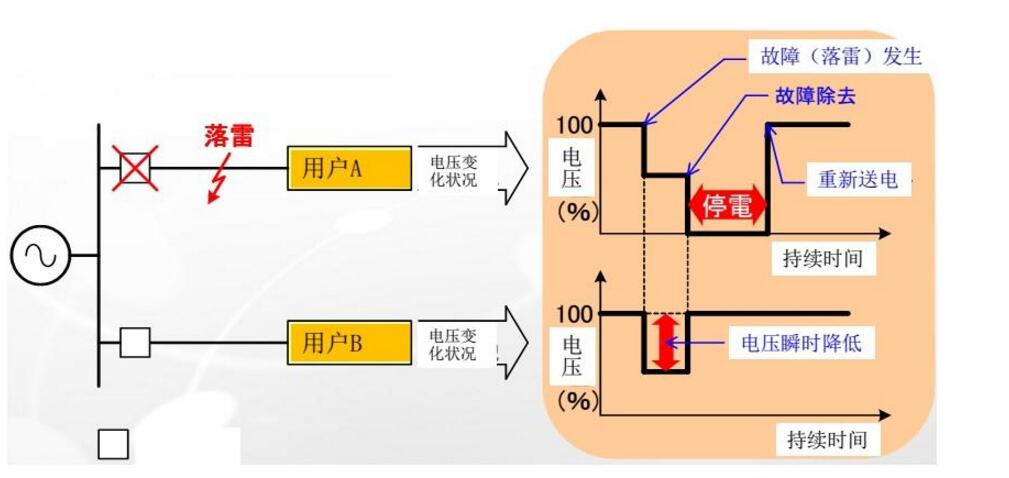

3.3 電力系統設計

在電力系統設計中,電壓降是評估輸電線路性能的重要指標。輸電線路的電壓降越小,輸電效率越高,能量損失越少。此外,電壓降還與輸電線路的穩定性和安全性有關。

電壓降的測量方法

4.1 電壓表法

電壓表法是測量電壓降的常用方法。將電壓表并聯在待測元件的兩端,可以直接測量電壓降。這種方法適用于低電壓、低電流的電路。

4.2 電流表-電阻法

電流表-電阻法是通過測量電流和電阻來計算電壓降。首先,將電流表串聯在電路中,測量電流;然后,將待測元件與一個已知電阻值的電阻并聯,測量并聯電阻上的電壓降。最后,根據歐姆定律計算待測元件上的電壓降。

4.3 示波器法

示波器法是測量交流電路中電壓降的方法。將示波器的探頭連接到待測元件的兩端,可以觀察到電壓隨時間變化的波形。通過測量波形的峰值或有效值,可以計算電壓降。

電壓降的優化方法

5.1 降低電阻值

降低電路中的電阻值可以減小電壓降。在設計電路時,可以選擇低阻值的電阻元件,或者增加導線的截面積,以降低電阻。

5.2 增加電源電壓

增加電源電壓可以減小電壓降對電路性能的影響。在電源設計中,可以選擇高電壓的電源,或者使用升壓電路來提高電壓。

5.3 使用并聯電阻

在電路中使用并聯電阻可以減小電壓降。并聯電阻可以分擔電流,從而減小單個電阻上的電壓降。

-

元件

+關注

關注

4文章

814瀏覽量

36554 -

回路

+關注

關注

0文章

68瀏覽量

12023 -

電勢

+關注

關注

0文章

70瀏覽量

13585 -

電壓降

+關注

關注

2文章

37瀏覽量

8675 -

熱能

+關注

關注

0文章

13瀏覽量

7218

發布評論請先 登錄

相關推薦

為什么會出現電壓降 如何實現盡可能低的電壓降

電壓降是整個回路的嗎為什么

電壓降是整個回路的嗎為什么

評論