在現代電子系統中,電磁干擾(EMI)是一個不容忽視的問題。共模電感作為一種有效的EMI抑制元件,廣泛應用于電源線路、信號傳輸線路等場合。然而,共模電感在抑制共模干擾的同時,也可能對差模信號產生一定的影響。

2. 共模與差模信號基礎

2.1 共模信號與差模信號定義

共模信號是指在兩條或多條導線上,信號的相位和幅度相同的信號。差模信號則是指在兩條導線上,信號相位相反,幅度相同的信號。

2.2 共模與差模信號的產生

共模信號通常由外部電磁干擾、電源線噪聲等引起,而差模信號則是系統內部的正常工作信號。

3. 共模電感的工作原理

3.1 共模電感的定義

共模電感是一種特殊的電感元件,它對共模電流具有高阻抗,而對差模電流的阻抗相對較低。

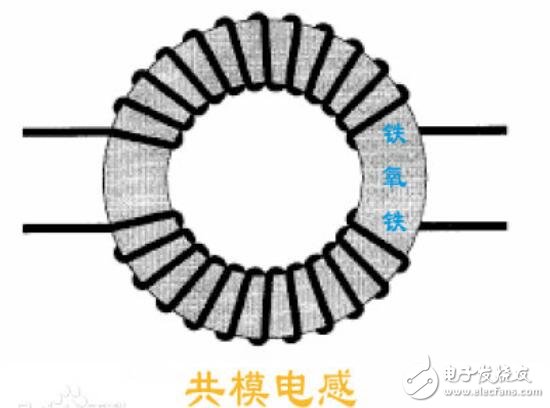

3.2 共模電感的構造

共模電感通常由兩個或多個線圈組成,這些線圈在磁芯上繞制,且具有相同的匝數和方向。

4. 共模電感對差模信號的影響

4.1 影響機理

共模電感對差模信號的影響主要來自于以下幾個方面:

- 寄生電容 :共模電感的線圈之間可能存在寄生電容,這可能導致差模信號的高頻成分受到衰減。

- 磁芯飽和 :在大電流或高磁場下,磁芯可能飽和,影響電感的性能,進而影響差模信號。

- 線圈分布電容 :線圈的分布電容可能導致差模信號的相位和幅度發生變化。

- 線圈繞制不均 :線圈繞制的不均勻性可能導致差模信號的不對稱性增加。

4.2 影響因素

- 電感值 :電感值的大小直接影響到共模電感對差模信號的阻抗。

- 頻率特性 :共模電感的頻率特性決定了其對不同頻率差模信號的影響程度。

- 磁芯材料 :不同的磁芯材料具有不同的磁導率和飽和特性,影響共模電感的性能。

5. 減小共模電感對差模信號影響的策略

5.1 優化設計

- 選擇合適的電感值 :根據系統的需求選擇合適的電感值,以減小對差模信號的影響。

- 使用高磁導率材料 :選擇高磁導率的磁芯材料,以提高共模電感的性能。

- 優化線圈繞制 :確保線圈繞制均勻,減少線圈之間的分布電容。

5.2 使用差模濾波器

在共模電感之后,可以添加差模濾波器來進一步抑制差模干擾,同時保護差模信號不受共模電感的影響。

6. 實驗與案例分析

6.1 實驗設置

設計一個實驗電路,包括共模電感和差模信號源,測量共模電感對差模信號的影響。

6.2 數據分析

通過實驗數據,分析共模電感對差模信號的具體影響,以及不同參數下的影響程度。

7. 結論

共模電感在抑制共模干擾的同時,確實可能對差模信號產生一定的影響。通過優化設計和使用差模濾波器,可以有效地減小這種影響,保證電子系統的正常工作。

-

電子系統

+關注

關注

0文章

397瀏覽量

31128 -

電磁干擾

+關注

關注

36文章

2285瀏覽量

105312 -

共模電感

+關注

關注

9文章

536瀏覽量

26919 -

差模信號

+關注

關注

0文章

43瀏覽量

11192

發布評論請先 登錄

相關推薦

共模電感對差模信號的影響

共模電感對差模信號的影響

評論