概述

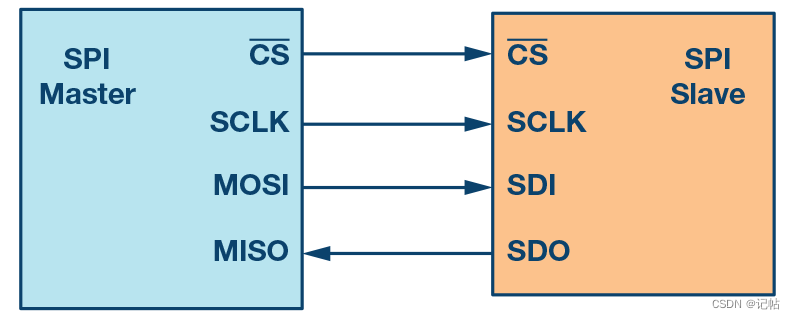

在嵌入式系統的設計中,串行外設接口(SPI)的通信速率是一個關鍵參數,它直接影響到系統的性能和穩定性。瑞薩電子的RA4M2微控制器為開發者提供了靈活而強大的SPI配置選項,確保可以根據不同的應用場景選擇最佳的數據傳輸速率。本文將深入探討RA4M2微控制器的SPI速率配置機制,并提供實用指南以幫助開發者實現精確的速率控制。

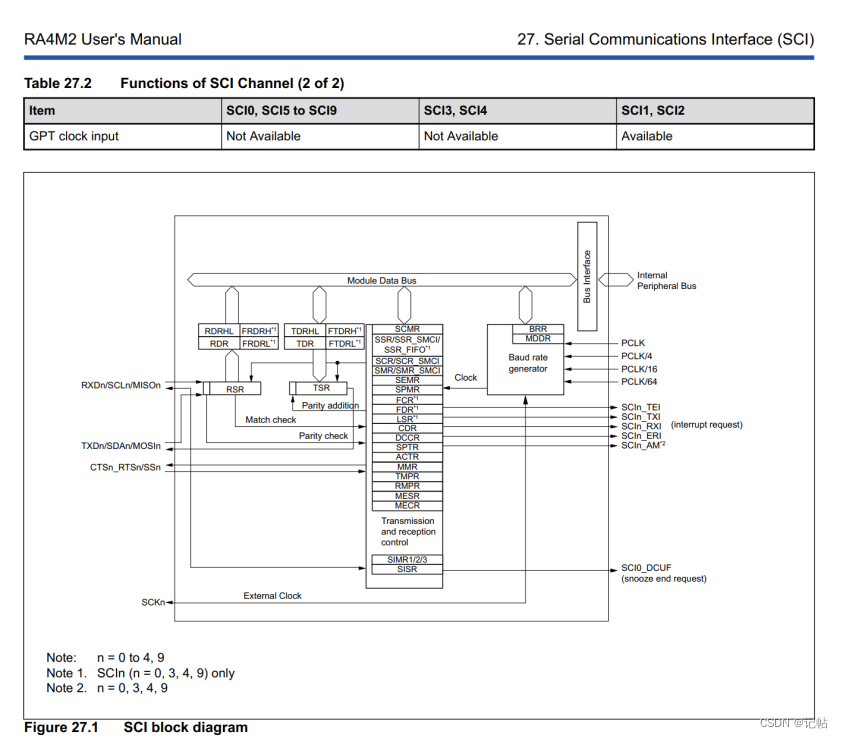

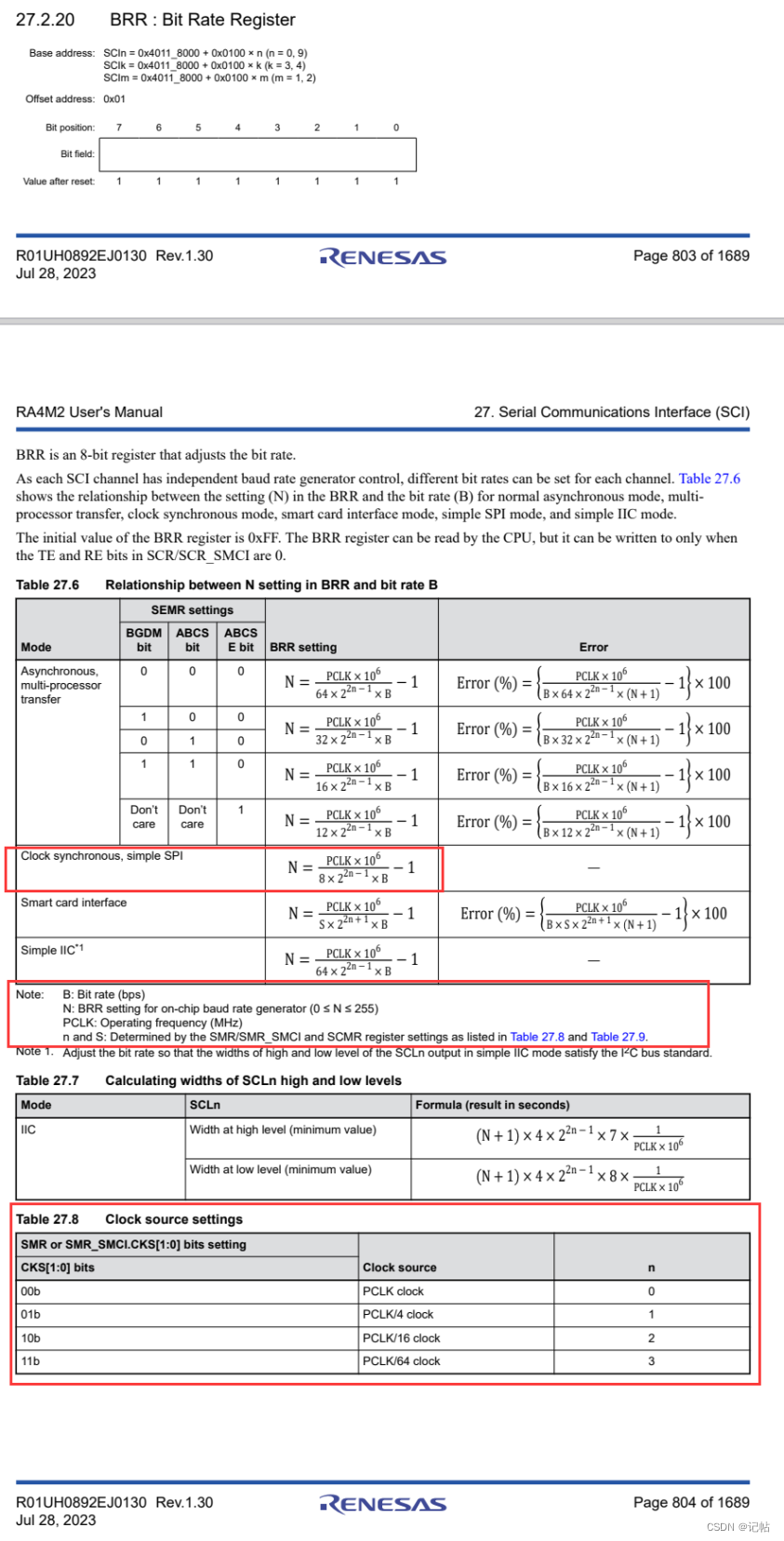

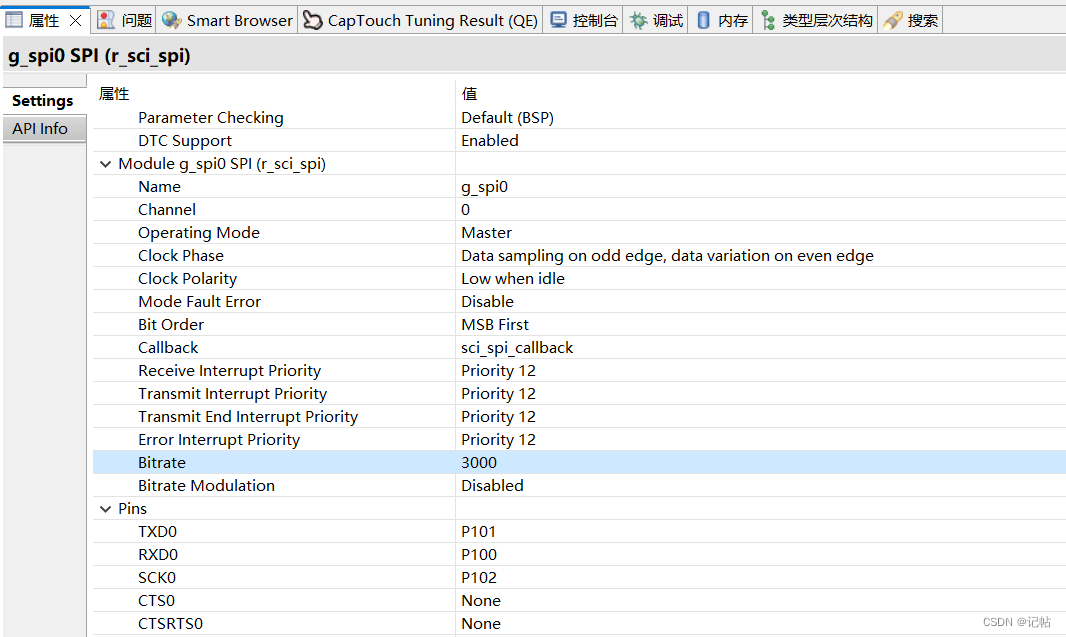

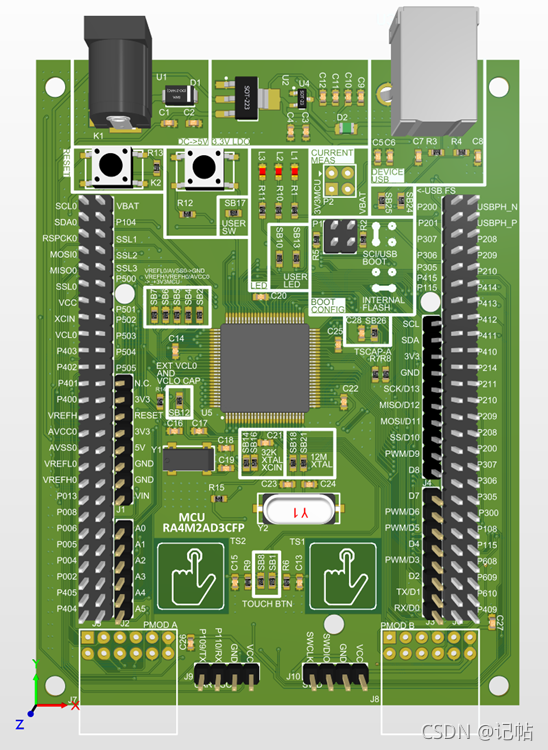

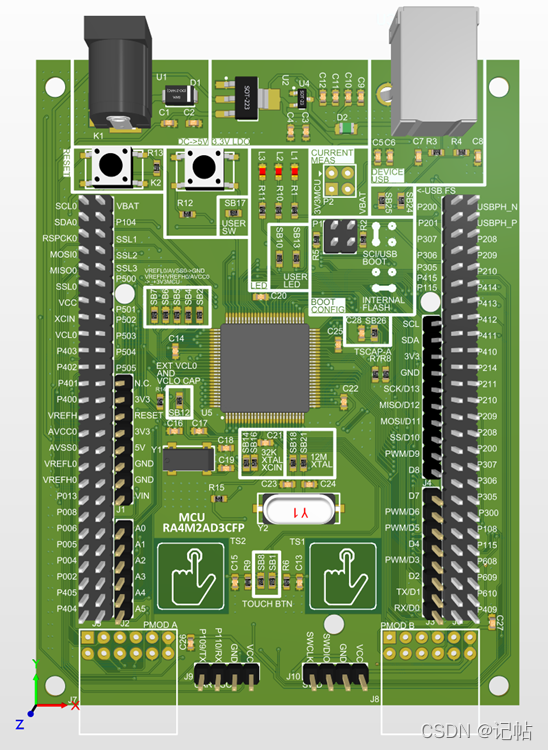

下面文檔是瑞薩RA4M2微控制器用戶手冊中的一部分,顯示了串行通信接口(SCI)的功能和其內部模塊圖。

時鐘來源為PCLK,可以進行1、4、16、64分頻。

最近在弄ST和瑞薩RA的課程,需要樣片的可以加群申請:615061293 。

視頻教學

https://www.bilibili.com/video/BV1NC4y1j7ew/?spm_id_from=333.788&vd_source=1c0885779e6e6a0b447c7e2fd1a68092

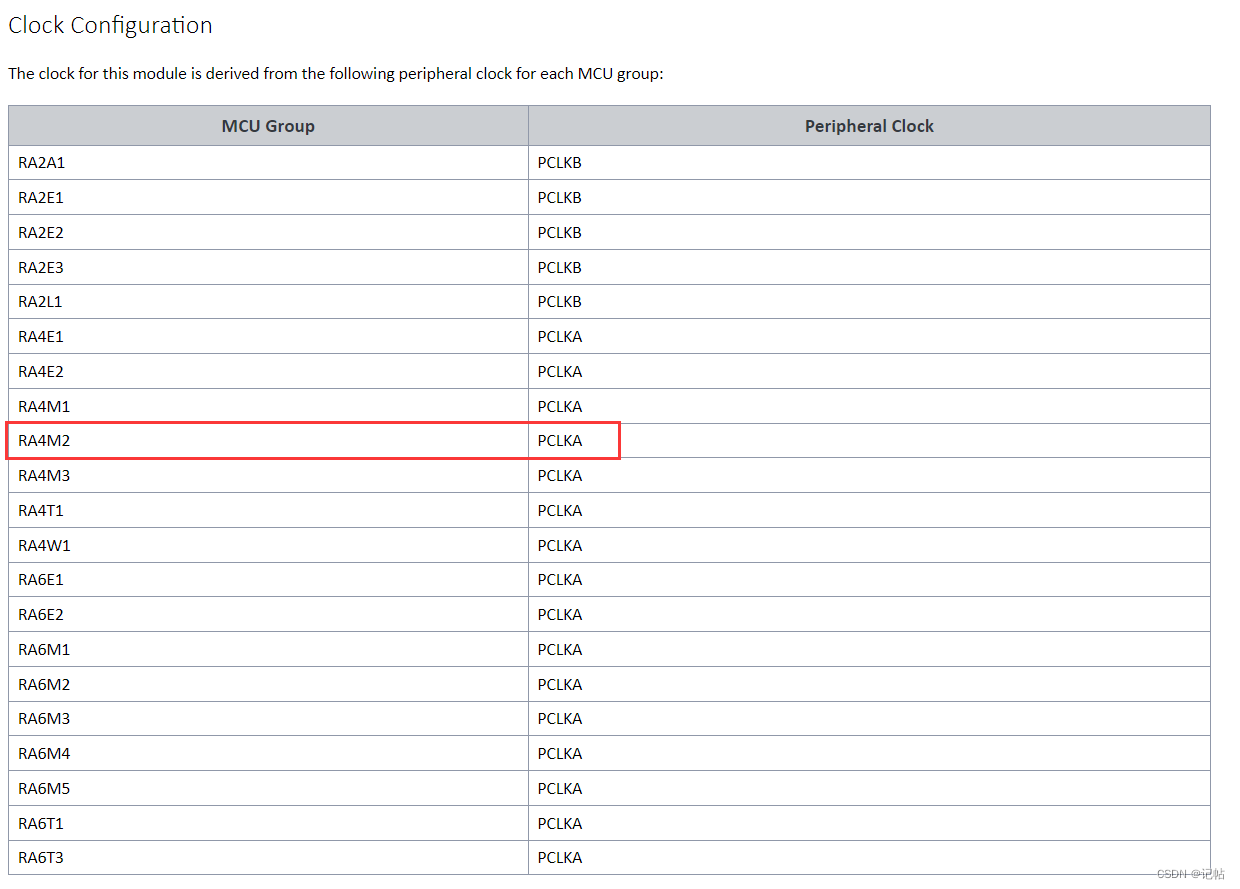

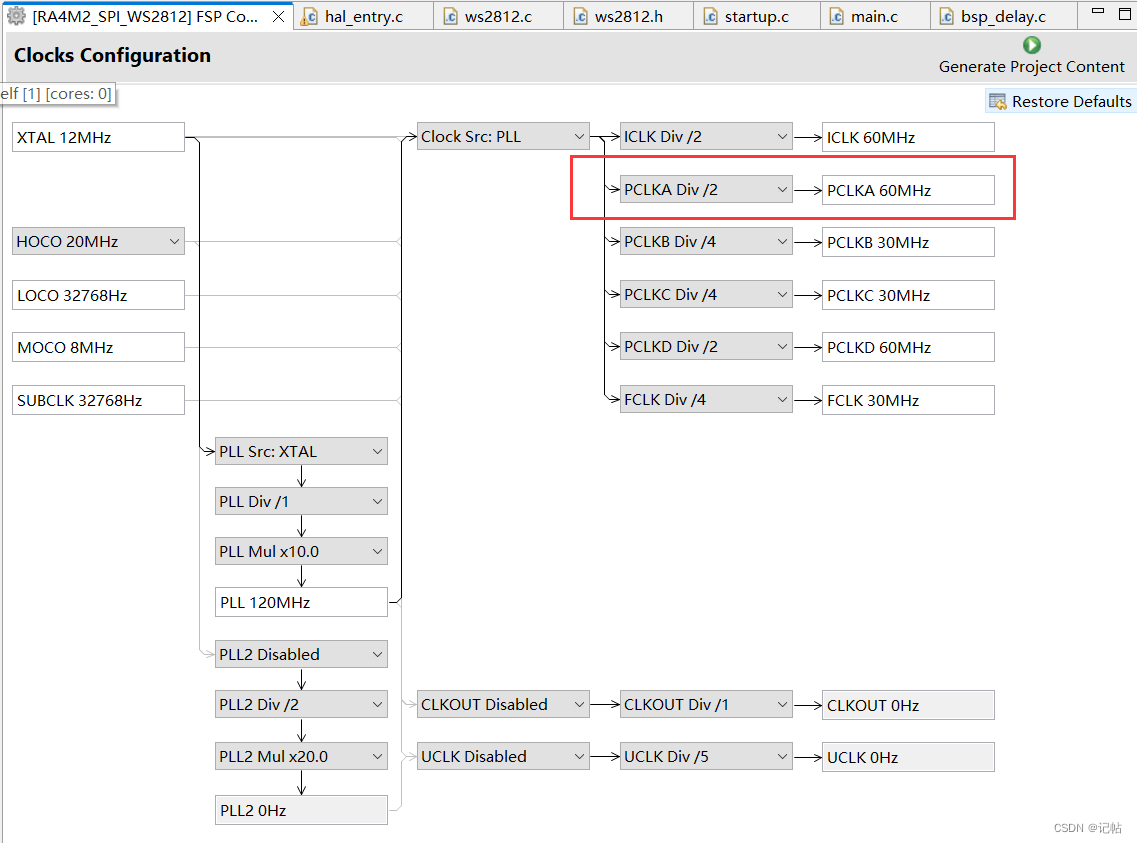

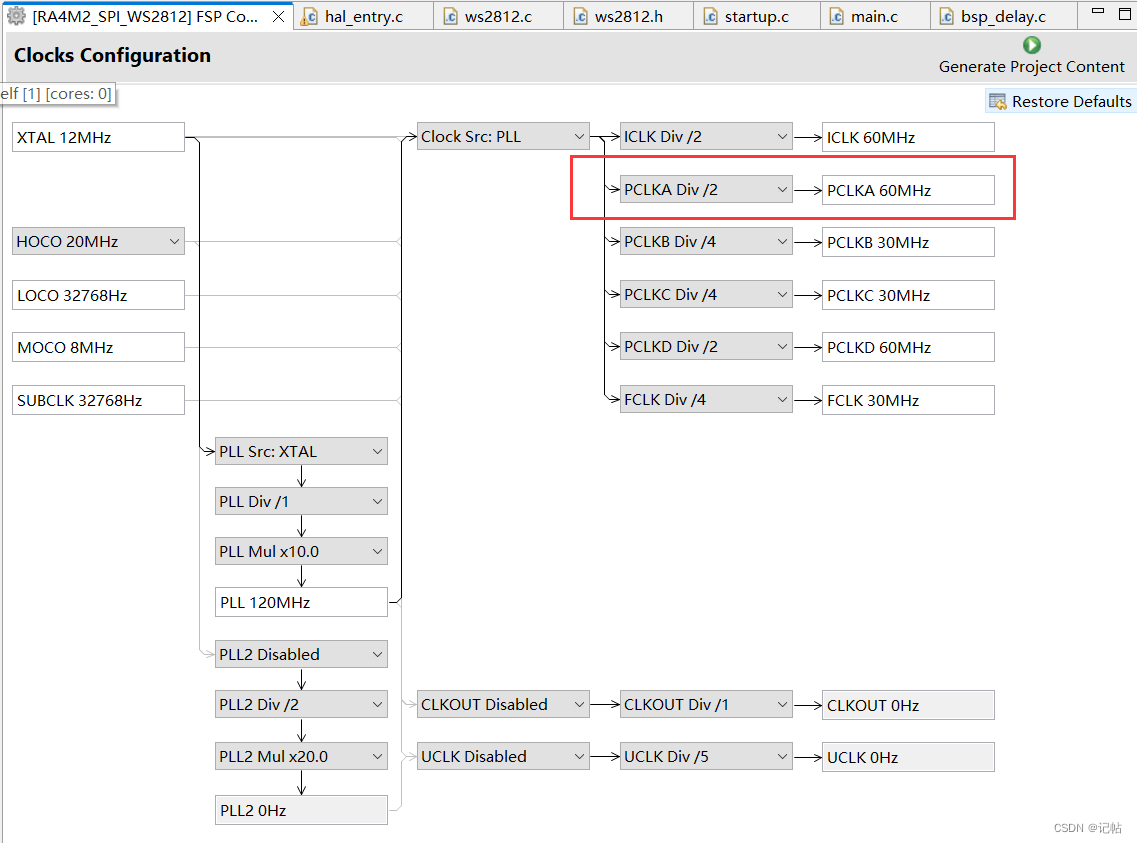

時鐘配置

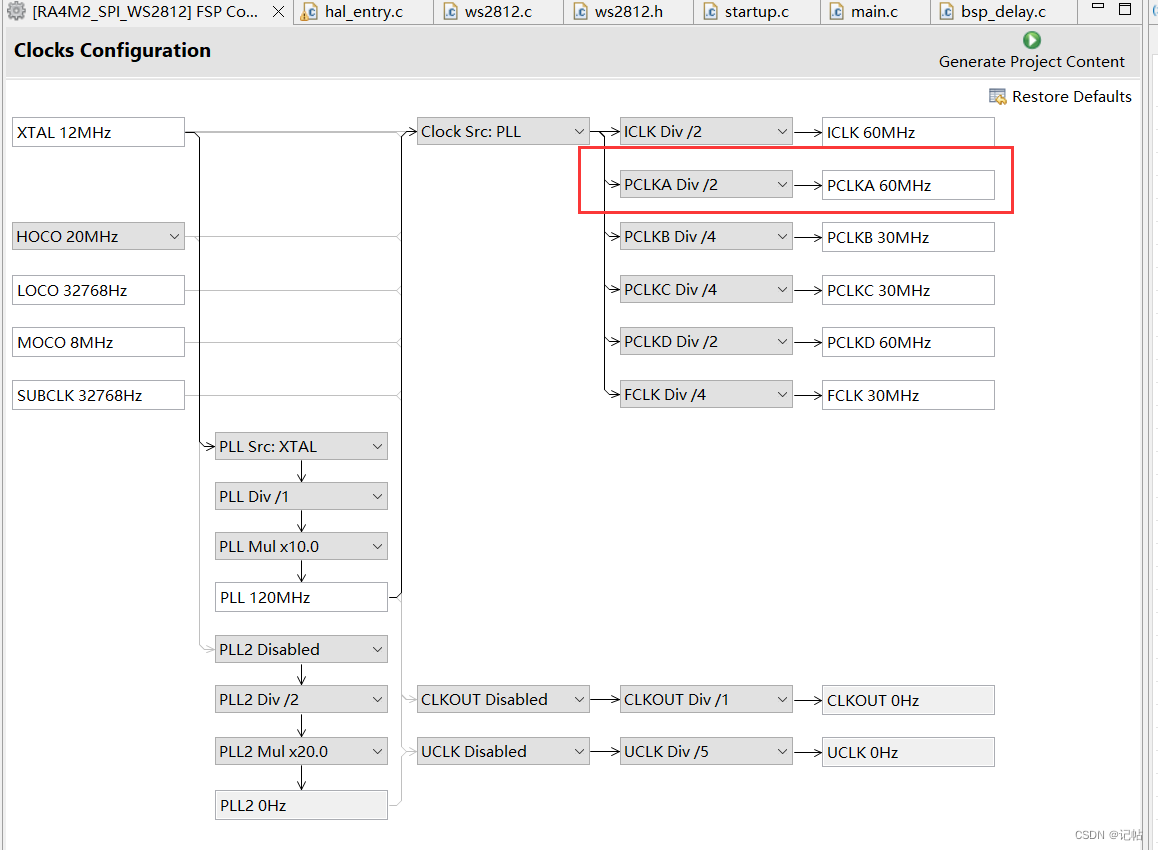

SPI (r_sci_spi)的時鐘來自PLCKA。

這里使用的PLCKA為60MHz。

解析RA4M2的BRR值

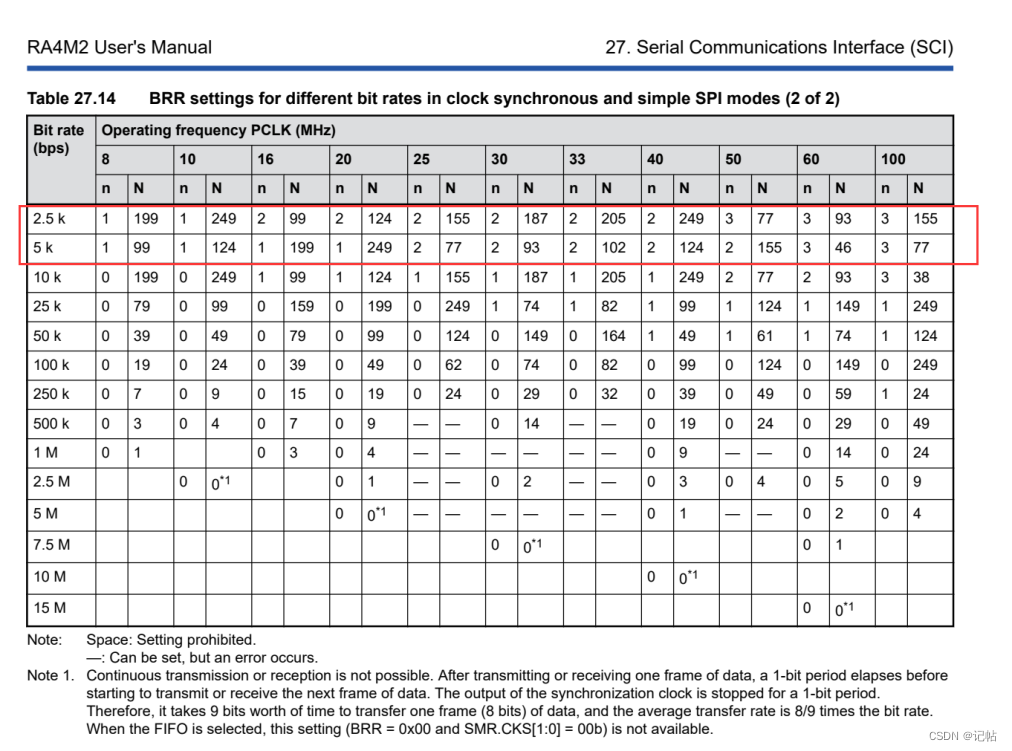

為了確定適合特定PCLK頻率和所需SPI通信速率的BRR值,RA4M2用戶手冊提供了詳盡的表格。這些表格列出了各種PCLK頻率與相應的SPI比特率組合,并指出了相應的BRR配置值。

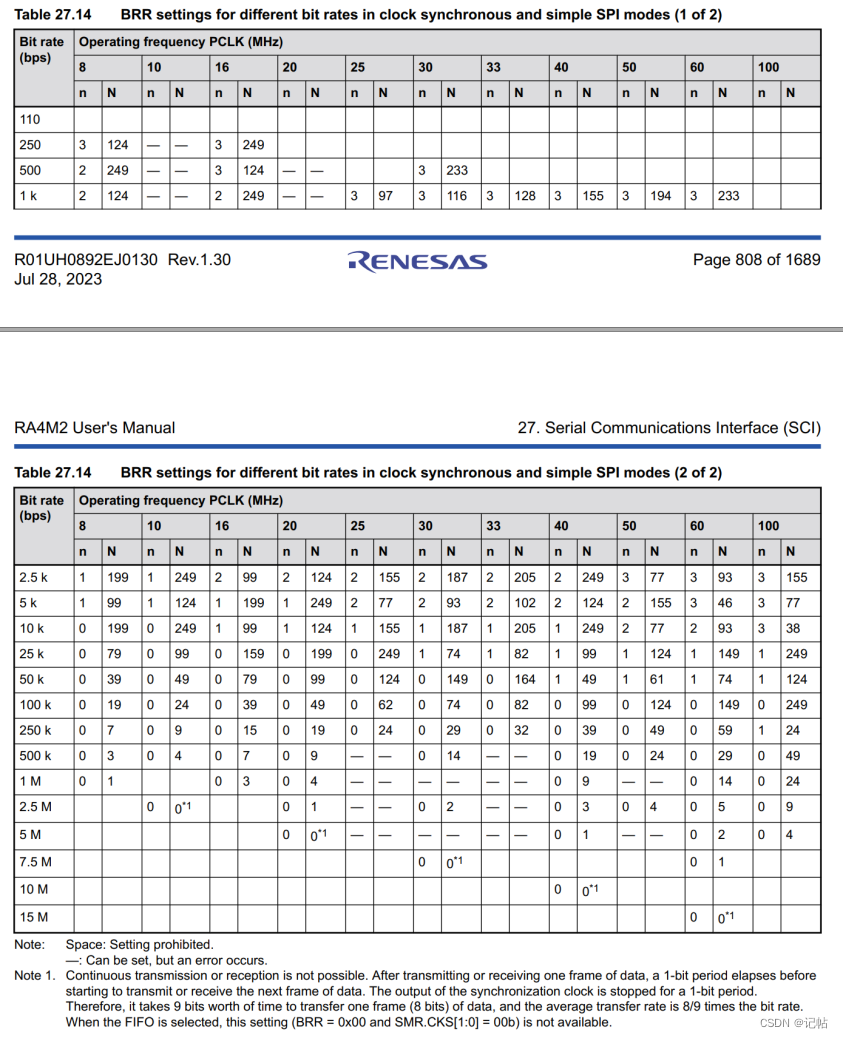

下圖顯示了瑞薩RA4M2微控制器用戶手冊的表格27.14,它列出了在時鐘同步和簡單SPI模式下不同比特率(bps)和操作頻率(PCLK)組合的BRR(Bit Rate Register)設置。

每一行代表一個特定的比特率,從110 bps到1 Mbps,而每一列對應一個特定的PCLK值,從8 MHz到100 MHz。在表格中,n 表示PCLK分頻值,而 N 是BRR寄存器的設置值。例如,要在25 MHz的PCLK上實現500 bps的比特率,BRR應該設置為249。

這個表格對于那些需要精確控制RA4M2微控制器上SCI通道比特率的開發者來說非常有用,因為它允許他們根據系統的PCLK頻率來查找或計算出必須寫入BRR寄存器的確切值。

注意的要點包括:

空格(" ")表示該設置是禁止的。

破折號("—")表示雖然可以設置,但可能會導致錯誤。

時鐘速率

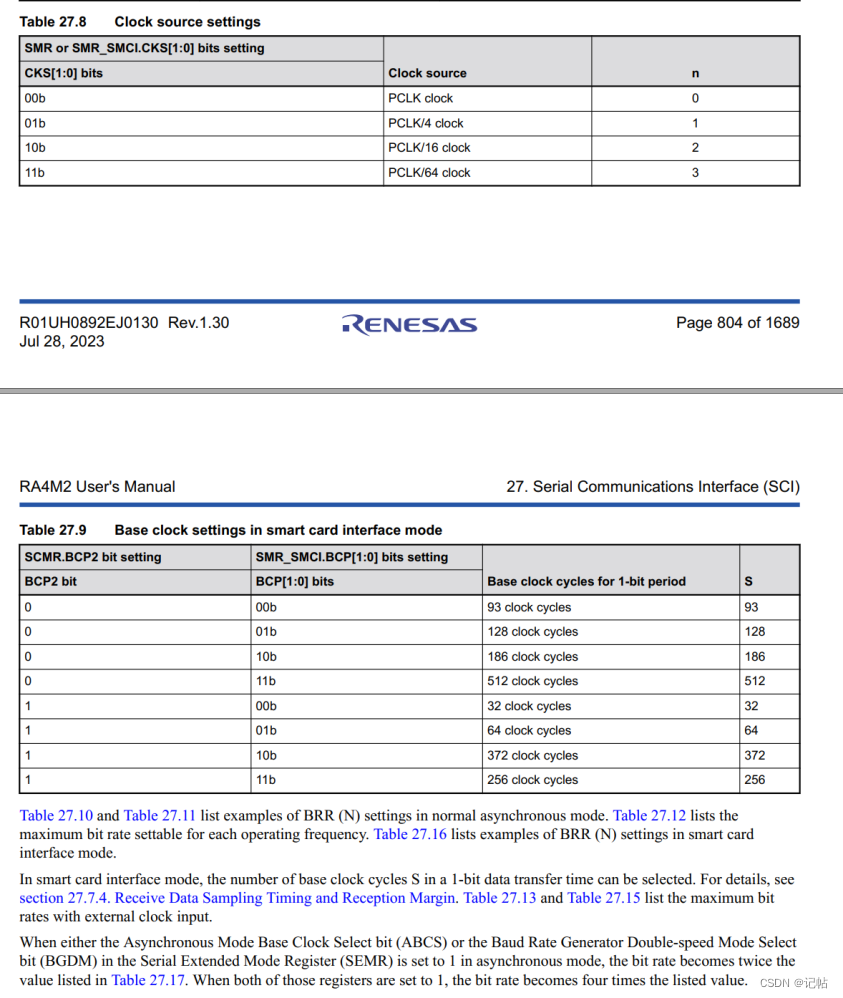

這里,CKS[1:0]的設置決定了SCI的時鐘分頻率,即PCLK的分頻值。表格列出了以下選項:

00b:使用PCLK作為時鐘源。

01b:PCLK的四分之一作為時鐘源。

10b:PCLK的十六分之一作為時鐘源。

11b:PCLK的六十四分之一作為時鐘源。

每種設置都有一個對應的分頻數n,它在編程時用于確定SCI時鐘頻率。

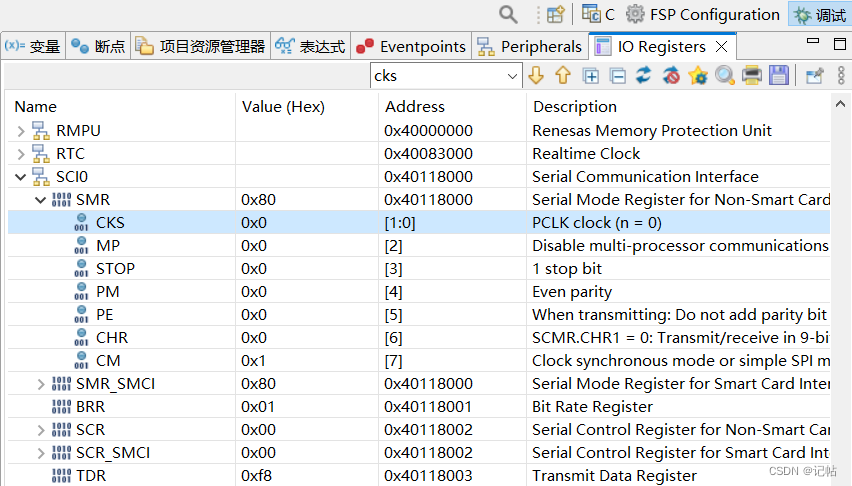

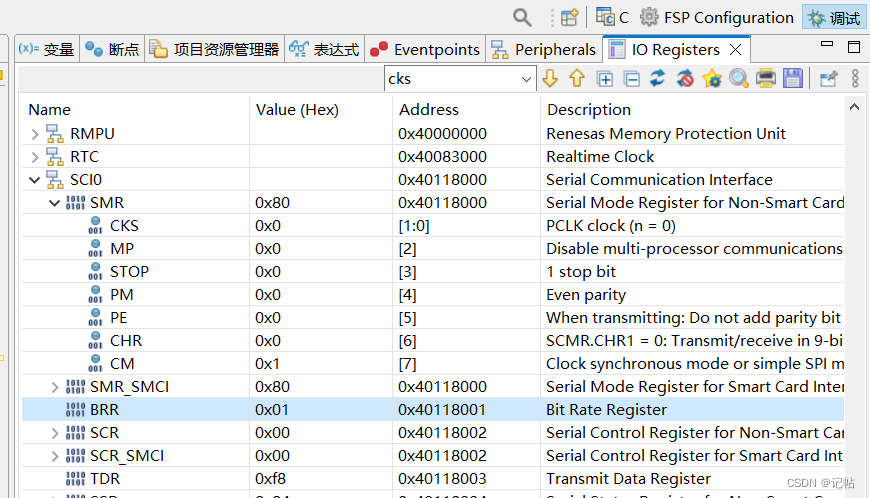

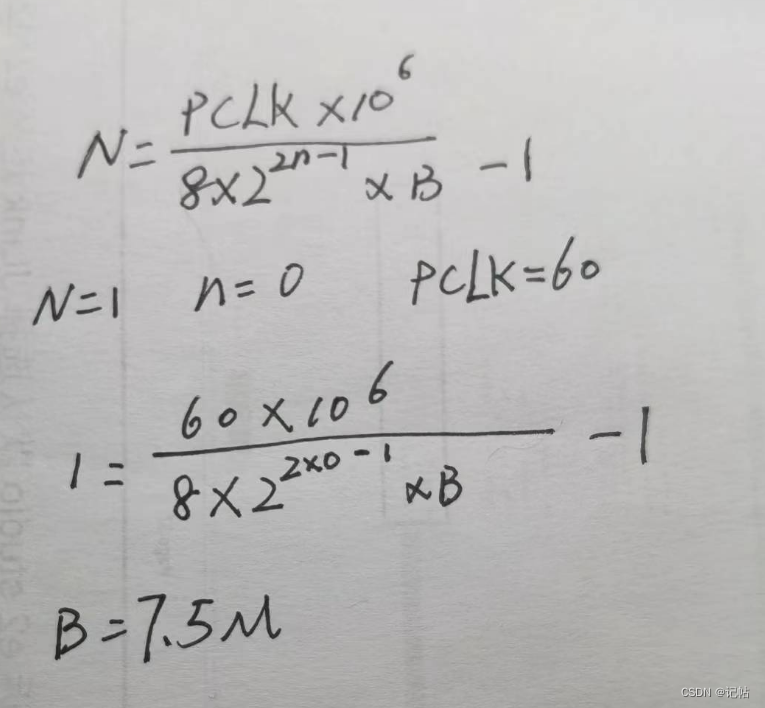

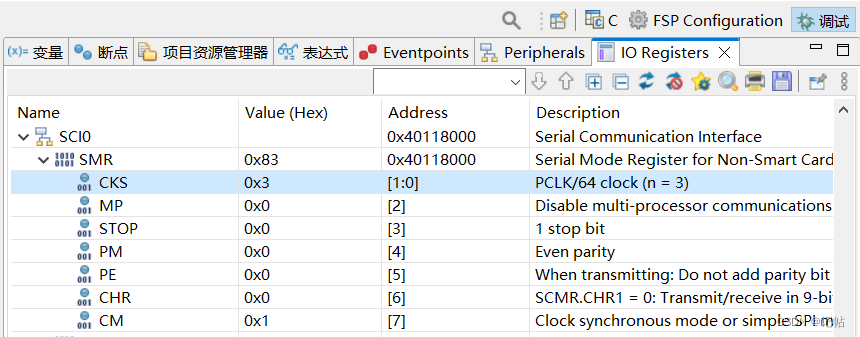

7.5M下寄存器值

PLCKA為60MHz,PCLK=60(MHz)

手冊給出對應的參數設置。

查看CKS寄存器可以得知為0,n=0

BRR寄存器為1,即N=1

計算SPI速率為7.5M。

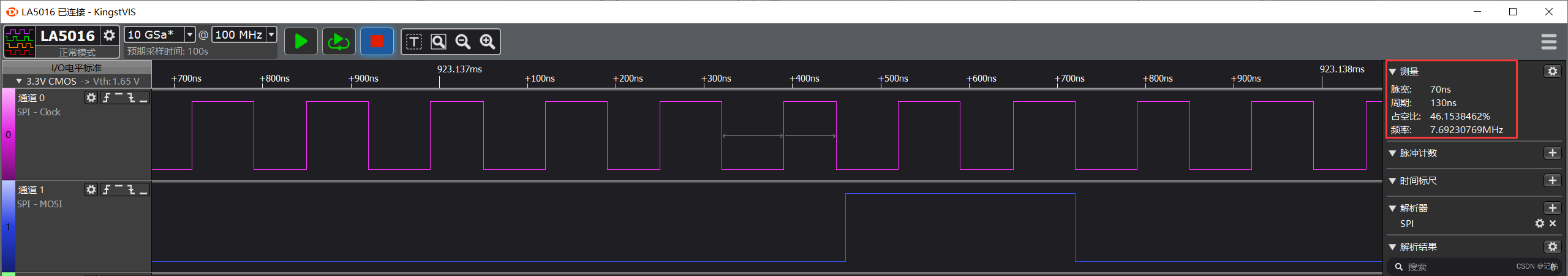

實際測試如下所示。

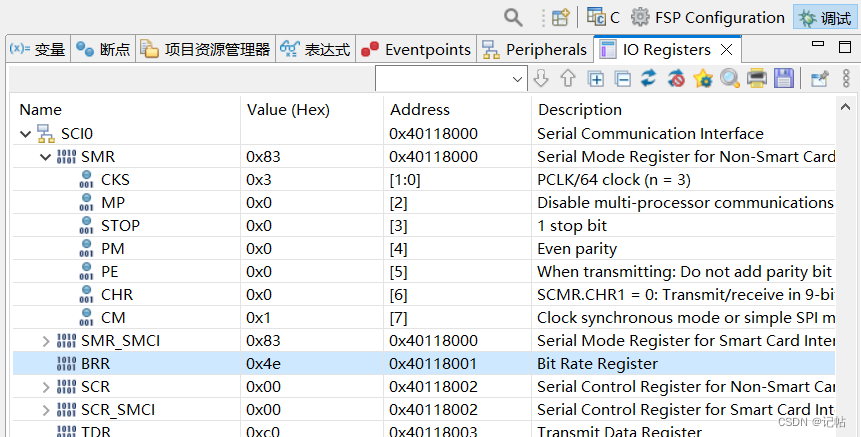

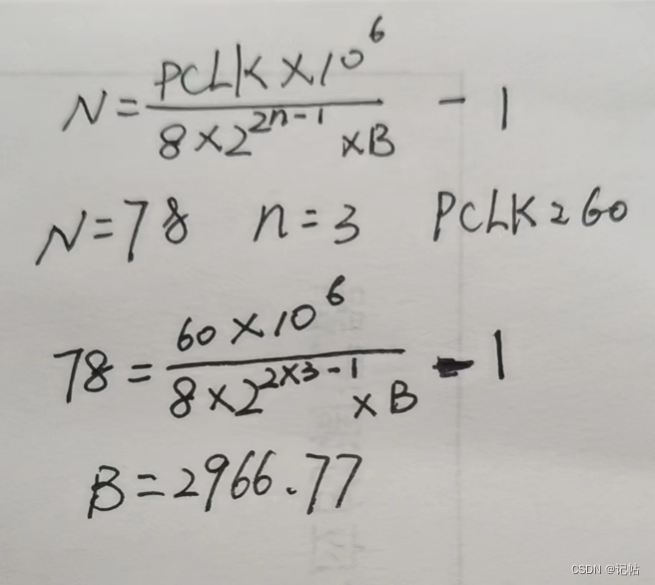

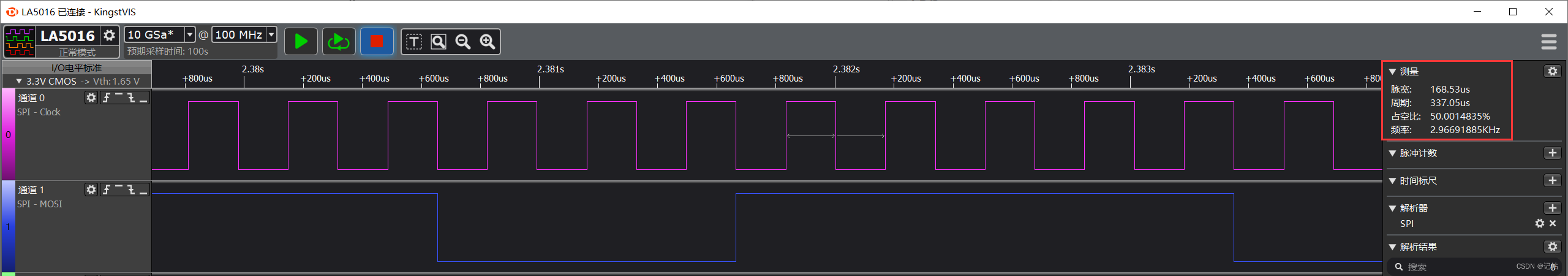

3K下寄存器值

設置速率為3k。

手冊未給出對應的參數設置。

PLCKA為60MHz,PCLK=60(MHz)

查看CKS寄存器可以得知為3,n=3

BRR寄存器為0x4e(78),即N=78

計算SPI實際速率為2966.77。

實際測試如下所示。

-

微控制器

+關注

關注

48文章

7270瀏覽量

149543 -

SPI

+關注

關注

17文章

1645瀏覽量

90488 -

瑞薩電子

+關注

關注

37文章

2796瀏覽量

71975 -

Studio

+關注

關注

2文章

188瀏覽量

28524

發布評論請先 登錄

相關推薦

瑞薩e2studio----SPI速率解析

瑞薩e2studio----SPI速率解析

評論