前言

我們聊聊芯片設(shè)計、流片、驗證、制造、成本的那些事;流片對于芯片設(shè)計來說就是參加一次大考。

流片的重要性就在于能夠檢驗芯片設(shè)計是否成功,是芯片制造的關(guān)鍵環(huán)節(jié),也就是將設(shè)計好的方案交給芯片制造廠生產(chǎn)出樣品。檢測設(shè)計的芯片是否達到設(shè)計要求,或者是否需要進一步優(yōu)化;如果能夠生產(chǎn)出符合要求的芯片,那么就可以大規(guī)模生產(chǎn)了。

上圖流程的輸入是芯片立項設(shè)計,輸出是做好的芯片晶圓。

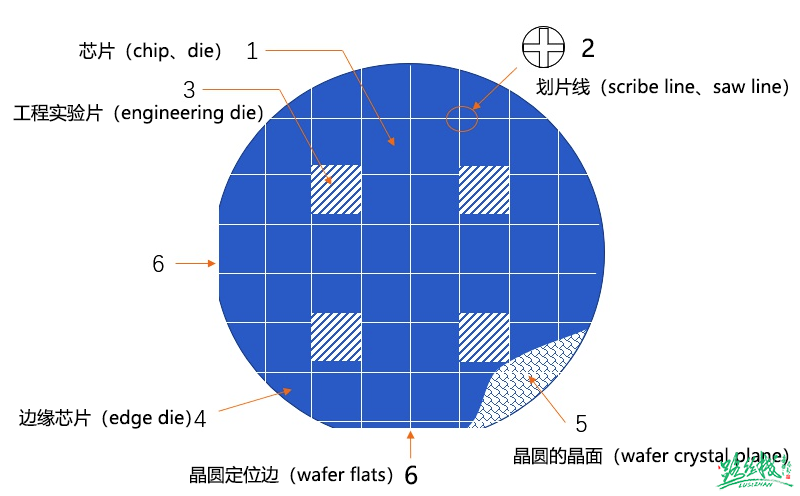

一、晶圓術(shù)語

1. 芯片(chip、die)、器件(device)、電路(circuit)、微芯片(microchip)或條碼(bar):所有這些名詞指的是在晶圓表面占大部分面積的微芯片圖形;

2. 劃片線(scribe line、saw line)或街區(qū)(street、avenue):這些區(qū)域是在晶圓上用來分隔不同芯片之間的間隔區(qū)。劃片線通常是空白的,但有些公司在間隔區(qū)內(nèi)放置對準(zhǔn)標(biāo)記,或測試的結(jié)構(gòu);

3. 工程實驗片(engineering die)和測試芯片(test die):這些芯片與正式芯片或電路芯片不同。它包括特殊的器件和電路模塊用于晶圓生產(chǎn)工藝的電性測試;

4. 邊緣芯片(edge die):在晶圓邊上的一些掩膜殘缺不全的芯片而產(chǎn)生的面積損耗。由于單個芯片尺寸增大而造成的更多邊緣浪費會由采用更大直徑晶圓所彌補。推動半導(dǎo)體工業(yè)向更大直徑晶圓發(fā)展的動力之一就是為了減少邊緣芯片所占的面積;

5. 晶圓的晶面(wafer crystal plane):圖中的剖面標(biāo)示了器件下面的晶格構(gòu)造,此圖中顯示的器件邊緣與晶格構(gòu)造的方向是確定的;

6. 晶圓定位邊(wafer flats)/凹槽(notche):圖示的晶圓由注定位邊(major flat)和副定位邊(minor flat),表示這是一個P型<100>晶向的晶圓。300mm和450mm直徑的晶圓都是用凹槽作為晶格導(dǎo)向的標(biāo)識。這些定位邊和凹槽在一些晶圓生產(chǎn)工藝中還輔助晶圓的套準(zhǔn)。

二、芯片的流片方式(Full Mask、MPW)

Full Mask和MPW都是集成電路的一種流片(將設(shè)計結(jié)果交出去進行生產(chǎn)制造)方式。Full Mask是“全掩膜”的意思,即制造流程中的全部掩膜都為某個設(shè)計服務(wù);而MPW 全稱為Multi Project Wafer,直譯為多項目晶圓,即多個項目共享某個晶圓,也即同一次制造流程可以承擔(dān)多個IC設(shè)計的制造任務(wù)。

1.Full Mask,“全掩膜”,即制造流程中的全部掩膜都為某個設(shè)計服務(wù);Full Mask的芯片,一片晶圓可以產(chǎn)出上千片DIE;然后封裝成芯片,可以支撐大批量的客戶需求。

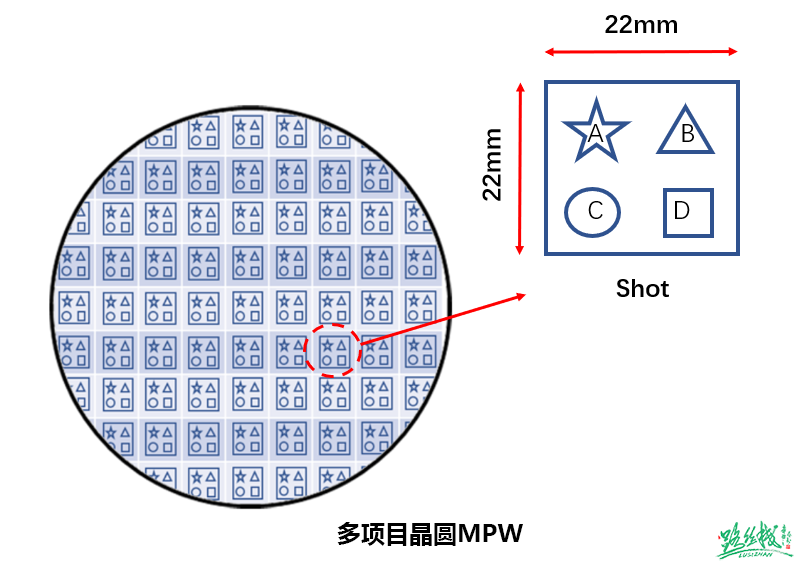

2.MPW全名叫Multi Project Wafer,和電路設(shè)計PCB的拼板打樣類似,叫多項目晶圓。多項目晶圓就是將多個使用相同工藝的集成電路設(shè)計放在同一晶圓片上流片,制造完成后,每個設(shè)計可以得到數(shù)十片芯片樣品,這一數(shù)量對于原型(Prototype)設(shè)計階段的實驗、測試已經(jīng)足夠。這種操作方式可以讓流片費下降90%-95%,也就大幅降低了芯片研發(fā)的成本。

晶圓廠每年都會有固定的幾次MPW機會,叫Shuttle (班車),到點即發(fā)車,是不是非常形象不同公司拼Wafer,得有個規(guī)則,MPW按SEAT來鎖定面積,一個SEAT一般是3mm*4mm的一塊區(qū)域,一般晶圓廠為了保障不同芯片公司均能參與MPW,對每家公司預(yù)定的SEAT數(shù)目會限制(其實SEAT多成本就上去了,MPW意義也沒有了)。MPW優(yōu)勢投片成本小,一般就小幾十萬,可以很好降低風(fēng)險;需要注意的是MPW從生產(chǎn)角度是一次完整的生產(chǎn)流程,因此其還是一樣耗時間,一次MPW一般需要6~9個月,會帶來芯片的交付時間后延。

因為是拼Wafer,因此通過MPW拿到的芯片數(shù)目就會很有限,主要用于芯片公司內(nèi)部做驗證測試,也可能會提供給極少數(shù)的頭部客戶。從這里大家可能已經(jīng)了解了,MPW是一個不完整的,不可量產(chǎn)的投片。

3.晶圓生產(chǎn)角度介紹MPW

畢竟芯片加工還是一個相對復(fù)雜的過程,我相信很多朋友看完第一和小二之前理解的晶圓結(jié)構(gòu),是下圖的,一個框歸屬于一個芯片公司。

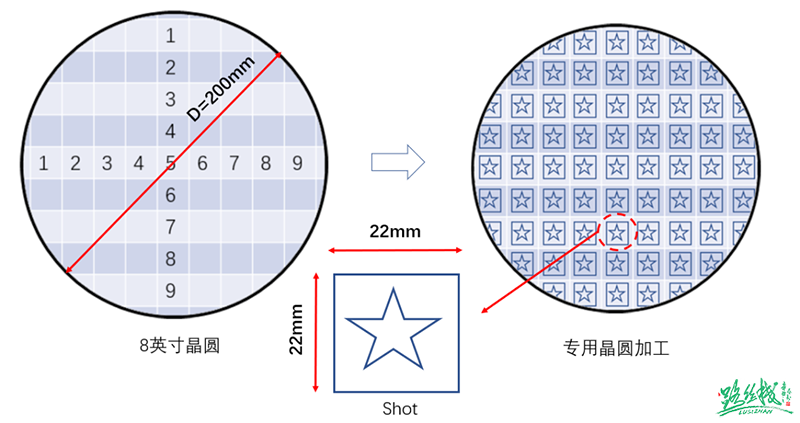

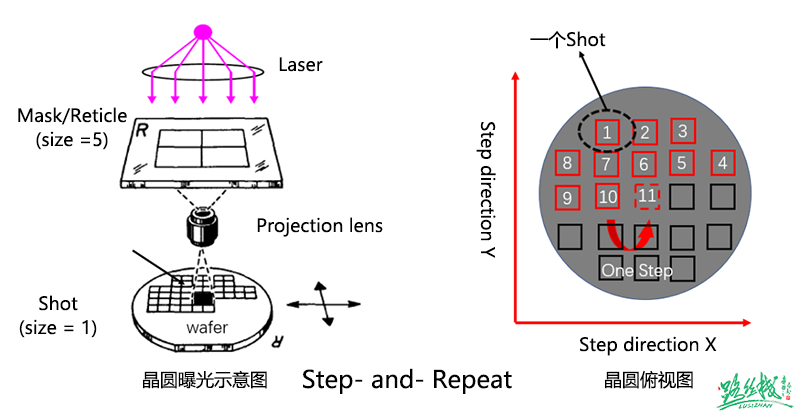

實則不然,這就需要和晶圓的生產(chǎn)流程的光刻技術(shù)相關(guān)了;現(xiàn)階段的光刻技術(shù)DUV/EUV等,大多采用縮影的方式進行曝光,如下圖所示:

采用1:5 放大的mask,對晶圓進行曝光,一次曝光的矩形區(qū)域通常稱為一個shot,完成曝光后,自動調(diào)整晶圓位置,對下個shot進行曝光,如此循環(huán)(Step-and-Repeat),直到整個晶圓完成曝光,而這一個Shot的區(qū)域,則是大家一起分擔(dān)SEAT的區(qū)域;

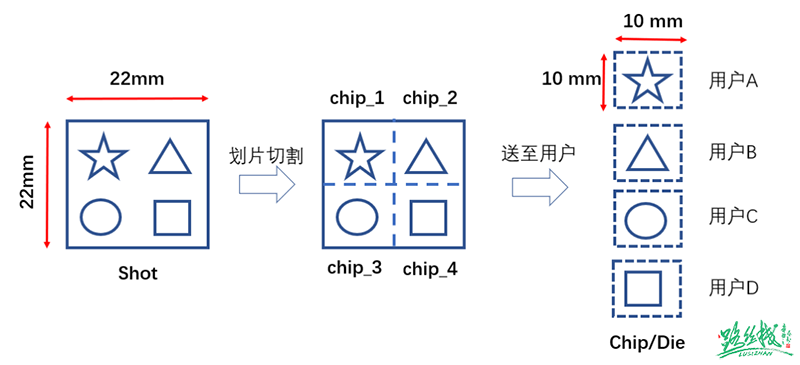

如下示意圖中,一個Shot里面劃分4個小格,每個格子給到一家廠商的設(shè)計,MPW晶圓一般20個以內(nèi)用戶。

三、芯片ECO流程

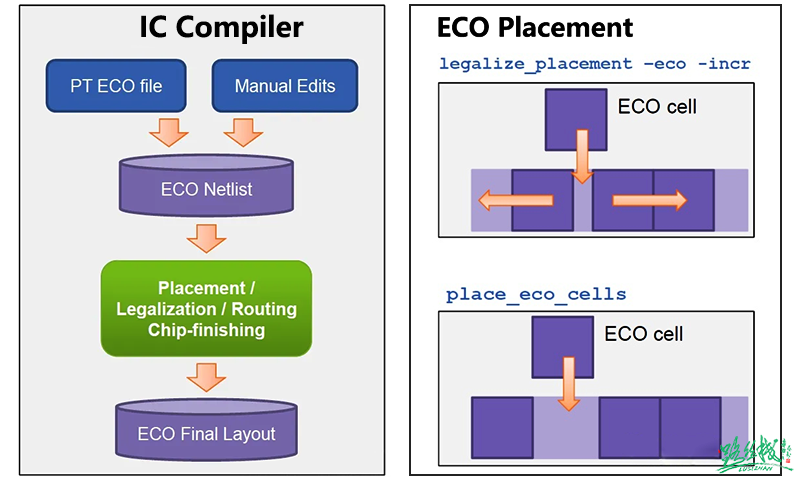

ECO 指的是Engineering Change Order,即工程變更指令。ECO可以發(fā)生在Tapeout之前,過程中,或者之后;Tapeout之后的ECO,改動少的可能僅需要改幾層Metal layer,改動大可能需要動十幾層Metal layer,甚至重新流片。ECO 的實現(xiàn)流程如下圖所示:

如果MPW或者FullMask的芯片,驗證有功能或者性能缺陷,通過ECO對電路和標(biāo)準(zhǔn)單元布局進行小范圍調(diào)整,保持原設(shè)計布局布線結(jié)果基本不變的前提下做小規(guī)模優(yōu)化,修復(fù)芯片的剩余違例,最終達到芯片的簽核標(biāo)準(zhǔn)。不能通過后端布局布線的流程來修復(fù)違例(重新走一遍流程太費時了),而要通過ECO的流程來進行時序、DRC、 DRV以及功耗等優(yōu)化。

四、流片Corner

1.Corner是芯片制造是一個物理過程,存在著工藝偏差(包括摻雜濃度、擴散深度、刻蝕程度等),導(dǎo)致不同批次之間,同一批次不同晶圓之間,同一晶圓不同芯片之間情況都是不相同的。

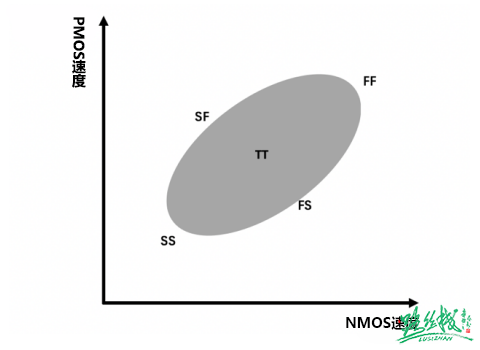

在一片wafer上,不可能每點的載流子平均漂移速度都是一樣的,隨著電壓、溫度不同,它們的特性也會不同,把他們分類就有了PVT(Process,Voltage,Temperature),而Process又分為不同的corner:TT:Typical N Typical P FF:Fast N Fast P SS:Slow N Slow P FS:Fast N Slow P SF:Slow N Fast P 第一個字母代表NMOS,第二個字母代表PMOS,都是針對不同濃度的N型和P型摻雜來說的。NMOS和PMOS在工藝上是獨立做出來的,彼此之間不會影響,但是對于電路,NMOS和PMOS是同時工作的,會出現(xiàn)NMOS快的同時PMOS也快,或者慢,所以會出現(xiàn)FF、SS、FS、SF四種情況。通過Process注入的調(diào)整,模擬器件速度快慢,同時根據(jù)偏差大小設(shè)定不同等級的FF和SS。正常情況下大部分是TT,而以上5種corner在+/-3sigma可以覆蓋約99.73%的范圍,這種隨機性的發(fā)生符合正態(tài)分布。

2.Corner wafer的意義在工程片流片的時候,F(xiàn)AB會pirun關(guān)鍵層次調(diào)整inline variation,有的還會下backup wafer以保證出貨的wafer器件on target,即在TT corner附近。如果單純是為了做一些樣品出來,只進行工程片流片,那可以不驗證corner,但如果為了后續(xù)量產(chǎn)準(zhǔn)備,是必須要考慮corner的。由于工藝在制作過程中會有偏差,而corner是對產(chǎn)線正常波動的預(yù)估,F(xiàn)AB也會對量產(chǎn)芯片的corner驗證有所要求。所以在設(shè)計階段就要滿足corner,在各種corner和極限溫度條件下對電路進行仿真,使其在各種corner上都能正常工作,才能使最終生產(chǎn)出的芯片良率高。

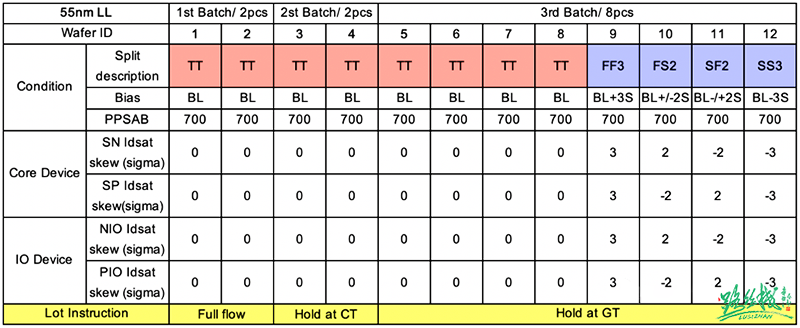

3.Corner Split Table策略 對于產(chǎn)品來講,一般corner做到spec上,正常情況下spec有6個sigma,如FF2(或2FF)表示往快的方向偏2個Sigma,SS3(或3SS)表示往慢的方向偏3個Sigma。Sigma主要表征了Vt的波動,波動大sigma就大,這里3個sigma就是在工藝器件的spec線上,可以允許超出一點點,因為線上波動不可能正正好好做到spec上。

如下是55nm Logic工藝片的例,擬定的corner split table:

①#1 & #2 兩片pilot wafer,一片盲封,一片測CP;

②#3 & #4 兩片hold在Contact,為后道改版預(yù)留工程wafer,可以節(jié)省ECO流片時間 ;

③#5~#12 八片hold在Poly,等pilot的結(jié)果看是否需要調(diào)整器件速度,并驗證corner;

④除了留有足夠的芯片用于測試驗證,Metal Fix,還應(yīng)根據(jù)項目需求,預(yù)留盡可能多的wafer作為量產(chǎn)出貨。

4.確認(rèn)Corner結(jié)果

首先,大部分都應(yīng)該落于四個corner決定的window范圍內(nèi),如果出現(xiàn)大的偏差,那可能是工藝shift。如果各個corner的良率都沒影響符合預(yù)期,那說明工藝窗口充分。如果有個別條件良率低,那就需要調(diào)整工藝窗口。Corner wafer的目的是驗證設(shè)計余量,考察良率是否有損失。大體上,超出這個corner約束性能范圍內(nèi)的芯片報廢。

Corner驗證對標(biāo)的是WAT測試結(jié)果,一般由FAB主導(dǎo),但是corner wafer的費用是由設(shè)計公司承擔(dān)的。一般成熟穩(wěn)定的工藝,同一片wafer上的芯片,同一批次的wafer甚至不同批次的wafer參數(shù)都是很接近的,偏差的范圍相對不會很大。工藝角(Process Corner)PVT(Precess Voltage Temperature)工藝誤差與雙極晶體管不同,在不同的晶片之間以及在不同的批次之間,MOSFETs參數(shù)變化很大。

為了在一定程度上減輕電路設(shè)計任務(wù)的困難,工藝工程師們要保證器件的性能在某個范圍內(nèi),大體上,他們以報廢超出這個性能范圍的芯片的措施來嚴(yán)格控制預(yù)期的參數(shù)變化。

①MOS管的快慢分別指閾值電壓的高低,快速對應(yīng)閾值低,慢速對應(yīng)閾值高。GBW=GM/CC ,其它條件相同情況下,vth越低,gm值越高,因此GBW越大,速度越快。(具體情況具體分析)

②電阻的快慢。fast對應(yīng)的是方塊電阻小,slow對應(yīng)的是方塊電阻大。

③電容的快慢。fast對應(yīng)的是電容最小,slow對應(yīng)的是容值最大。

五、流片成本和晶圓價格

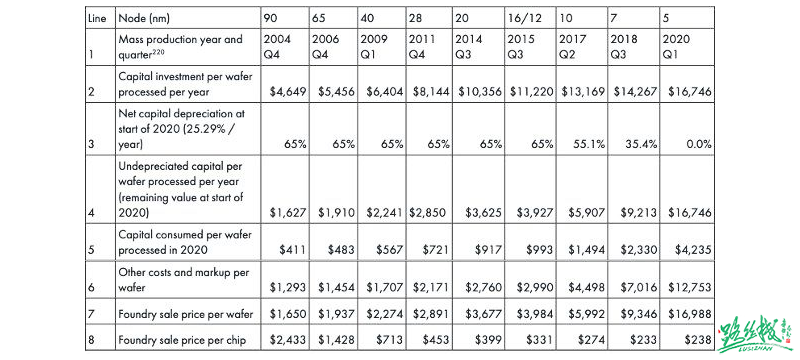

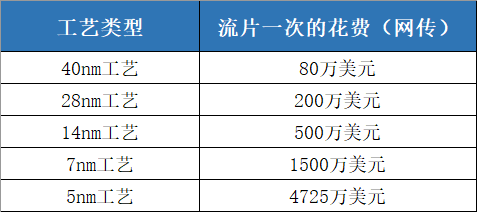

40nm的流片Mask成本大概在80-90萬美元,晶圓成本每片在3000-4000美元左右,加上IP merge,七八百萬人民幣跑不掉了。

28nm工藝流片一次需要200萬美元;14nm工藝流片一次需要500萬美元;7nm工藝流片一次需要1500萬美元;5nm工藝流片一次4725萬美元;3nm工藝流片可能要上億美元;掩膜版、晶圓這兩項主要流片成本中,掩膜版最貴。

越先進的工藝節(jié)點,所需要的掩膜版層數(shù)就越多;因為每一層“掩膜板”對應(yīng)涂抹一次光刻膠、曝光、顯影、刻蝕等操作,涉及材料成本、儀器折舊成本,這些成本都需要fabless客戶買單!

28nm大概需要40層,14nm工藝需要60張掩膜版;7nm工藝需要80張甚至上百張掩膜版;一層Mask 8萬美金,因此芯片必須量產(chǎn),拉低成本!

40nm MCU工藝為例:如果生產(chǎn)10片晶圓,每片晶圓成本(90萬+ 4000*10)/10=9.4萬美元;生產(chǎn)10000片晶圓,每片晶圓成本(90萬+4000*10000)/10000=4090美元。(晶圓量越大越便宜,不同產(chǎn)家報價也不一樣。)

晶圓代工價格來源于網(wǎng)絡(luò)

臺積電今年給的最新報價:最先進的制程3nm,每片晶圓19865美元,折合人民幣大概14.2w左右。

結(jié)語

芯片從設(shè)計到成品有幾個重要環(huán)節(jié),分別是設(shè)計->流片->封裝->測試,但芯片成本構(gòu)成的比例確大不相同,一般為人力成本20%,流片40%,封裝35%,測試5%。

芯片流片是高風(fēng)險的事情,這個風(fēng)險有多高,這個概率在15%-35%左右;不同的團隊和芯片種類概率也不一樣。有模擬芯片公司即使在團隊完備、思路清晰的情況下,還是耗了8年時間,歷經(jīng)18次流片,才最終完成了傳感器模擬計算IP驗證,打造出了理想中的那顆超低功耗、超近傳感芯片。

-

晶圓

+關(guān)注

關(guān)注

52文章

4720瀏覽量

127072 -

芯片設(shè)計

+關(guān)注

關(guān)注

15文章

966瀏覽量

54551 -

芯片驗證

+關(guān)注

關(guān)注

5文章

34瀏覽量

47107 -

流片

+關(guān)注

關(guān)注

0文章

26瀏覽量

9713

發(fā)布評論請先 登錄

相關(guān)推薦

流片的時間與金錢成本

片上網(wǎng)絡(luò)核心芯片的驗證

原型驗證即服務(wù)助力芯片設(shè)計

講講芯片的流片制造那些事兒

是德科技使用數(shù)字孿生信令實現(xiàn)先進的半導(dǎo)體流片原型設(shè)計

國芯科技:正在流片驗證chiplet芯片高性能互聯(lián)IP技術(shù)

聊聊芯片設(shè)計、流片、驗證、制造、成本的那些事

聊聊芯片設(shè)計、流片那些事

芯片設(shè)計流片、驗證、成本的那些事

芯片設(shè)計流片、驗證、成本的那些事

評論