雙穩態觸發器(Bistable Trigger)是一種具有兩個穩定狀態的邏輯電路,廣泛應用于數字電路設計中。它具有兩個基本性質:記憶性和切換性。

一、雙穩態觸發器的基本概念

1.1 雙穩態觸發器的定義

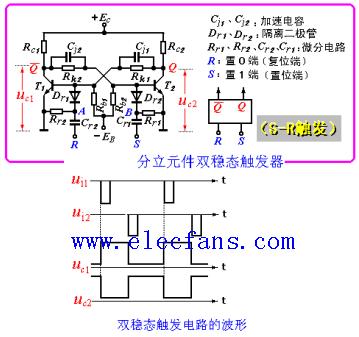

雙穩態觸發器是一種具有兩個穩定狀態的邏輯電路,通常由兩個交叉耦合的反相器或門電路構成。在沒有外部輸入信號的情況下,雙穩態觸發器可以保持在兩個穩定狀態之一,即“0”狀態或“1”狀態。

1.2 雙穩態觸發器的組成

雙穩態觸發器主要由以下部分組成:

(1)輸入端:接收外部輸入信號,用于觸發雙穩態觸發器的狀態切換。

(2)輸出端:輸出雙穩態觸發器的當前狀態,可以是“0”或“1”。

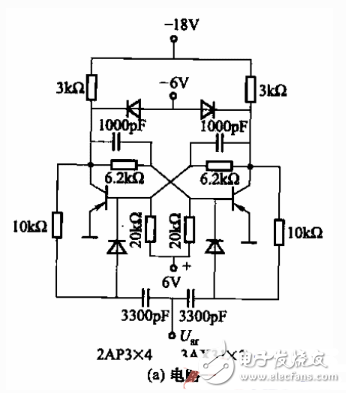

(3)存儲元件:用于存儲雙穩態觸發器的狀態信息,通常由電容、電感或半導體器件構成。

(4)觸發電路:根據輸入信號控制雙穩態觸發器的狀態切換。

1.3 雙穩態觸發器的分類

根據觸發方式的不同,雙穩態觸發器可以分為以下幾類:

(1)SR觸發器(Set-Reset Trigger):通過設置(Set)和復位(Reset)信號來控制狀態切換。

(2)JK觸發器(Jack-Kilby Trigger):通過同時接收J和K信號來控制狀態切換。

(3)D觸發器(Data Trigger):通過接收D信號來控制狀態切換。

(4)T觸發器(Toggle Trigger):通過接收T信號來控制狀態切換,每次觸發都會使輸出狀態翻轉。

二、雙穩態觸發器的基本性質

2.1 記憶性

記憶性是雙穩態觸發器的核心特性之一,它指的是雙穩態觸發器能夠保持其當前狀態,直到接收到外部觸發信號。具體來說,雙穩態觸發器的記憶性包括以下幾個方面:

(1)穩定性:在沒有外部輸入信號的情況下,雙穩態觸發器能夠保持其當前狀態,不會因為內部噪聲或溫度變化而發生狀態變化。

(2)抗干擾性:雙穩態觸發器具有較強的抗干擾能力,即使在外部環境變化較大的情況下,也能夠保持其狀態穩定。

(3)狀態保持時間:雙穩態觸發器能夠在接收到觸發信號后,保持新狀態一定時間,直到下一次觸發信號的到來。

2.2 切換性

切換性是雙穩態觸發器的另一個基本特性,它指的是雙穩態觸發器能夠在接收到外部觸發信號后,從當前狀態切換到另一個穩定狀態。具體來說,雙穩態觸發器的切換性包括以下幾個方面:

(1)觸發條件:雙穩態觸發器需要滿足一定的觸發條件,才能實現狀態切換。例如,SR觸發器需要同時滿足Set和Reset信號的特定組合才能切換狀態。

(2)切換速度:雙穩態觸發器在接收到觸發信號后,能夠在較短的時間內完成狀態切換,以滿足高速數字電路的設計要求。

(3)切換可靠性:雙穩態觸發器在切換過程中,需要保證狀態切換的可靠性,避免因為電路設計不當或外部干擾而導致狀態切換失敗。

三、雙穩態觸發器的應用

3.1 存儲器設計

雙穩態觸發器在存儲器設計中具有重要應用。例如,靜態隨機存取存儲器(SRAM)就是利用雙穩態觸發器來存儲數據的。每個存儲單元由兩個交叉耦合的反相器構成,可以存儲一位二進制數據。

3.2 計數器設計

雙穩態觸發器在計數器設計中也發揮著重要作用。通過將多個雙穩態觸發器級聯,可以構成多位計數器,實現對輸入信號的計數功能。

3.3 時序控制

雙穩態觸發器在時序控制中具有廣泛應用。例如,在微處理器的指令執行過程中,需要通過雙穩態觸發器來控制指令的取值、譯碼和執行等各個階段的時序。

3.4 信號同步

在數字通信系統中,雙穩態觸發器可以用于信號同步。通過將接收到的信號與本地時鐘信號進行同步,可以消除信號傳輸過程中的時延和抖動,提高通信系統的穩定性和可靠性。

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42577 -

反相器

+關注

關注

6文章

310瀏覽量

43242 -

數字電路

+關注

關注

193文章

1600瀏覽量

80497

發布評論請先 登錄

相關推薦

雙穩態觸發器電路圖大全(三極管/CD4017/CD4013雙D觸發器)

雙穩態觸發器的兩個基本性質是什么

雙穩態觸發器的兩個基本性質是什么

評論