RS觸發器(Reset-Set Trigger)是數字電路中的一種基本邏輯單元,具有兩個穩定狀態,即“置位”(Set)狀態和“復位”(Reset)狀態。其靜態特性主要指的是在沒有外部觸發信號變化時,觸發器保持其當前狀態不變的能力。

一、RS觸發器的基本結構

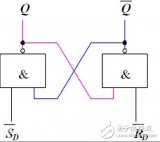

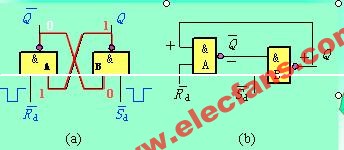

RS觸發器通常由兩個交叉耦合的邏輯門(如或非門或非門)組成,形成正反饋回路。這種結構使得觸發器能夠保持其輸出狀態,直到接收到新的觸發信號。觸發器的兩個輸入端分別為S(置位)和R(復位),兩個輸出端分別為Q和Q'(Q的反相)。

二、靜態特性的定義

靜態特性是指觸發器在沒有外部信號變化時,其輸出狀態保持不變的特性。這是觸發器作為存儲單元的基本要求之一,也是其能夠用于構建寄存器、計數器等復雜數字系統的基礎。

三、RS觸發器的靜態特性分析

1. 保持狀態不變

在沒有外部觸發信號(即S和R保持不變)的情況下,RS觸發器的輸出狀態將保持不變。這是由觸發器的正反饋機制決定的。當觸發器處于某一穩定狀態時(如Q=1,Q'=0),即使外部信號存在微小的波動或噪聲,只要這些波動不足以改變S和R的狀態,觸發器的輸出就會保持不變。

2. 輸入信號的約束

為了保證RS觸發器的靜態特性,其輸入信號需要滿足一定的約束條件。具體來說,當S=1且R=0時,觸發器應進入置位狀態;當S=0且R=1時,觸發器應進入復位狀態;當S=0且R=0時,觸發器的狀態應保持不變(這取決于其初始狀態);而當S=1且R=1時,這是觸發器的禁止狀態,通常應避免這種情況的發生,因為此時觸發器的輸出狀態是不確定的。

3. 穩定性分析

RS觸發器的穩定性主要取決于其內部的正反饋回路和輸入信號的穩定性。在正反饋回路的作用下,一旦觸發器進入某一穩定狀態,它就會通過內部邏輯門之間的相互作用來保持該狀態不變。同時,輸入信號的穩定性也是影響觸發器穩定性的重要因素。如果輸入信號存在較大的波動或噪聲,可能會導致觸發器在狀態之間頻繁切換,從而影響其正常工作。

四、RS觸發器靜態特性的應用

RS觸發器的靜態特性使其在各種數字電路設計中具有廣泛的應用。以下是一些典型的應用場景:

1. 寄存器

寄存器是數字系統中用于存儲數據的基本單元。它由多個RS觸發器(或其他類型的觸發器)組成,每個觸發器可以存儲一位二進制數據。通過組合多個觸發器并添加適當的控制邏輯和輸出邏輯,可以構建出能夠存儲多位數據的寄存器。這些寄存器在微處理器、數字信號處理器等復雜數字系統中起著至關重要的作用。

2. 計數器

雖然RS觸發器本身不直接實現計數功能,但它們可以與其他邏輯門電路結合使用來構建計數器。例如,通過使用JK觸發器(可以看作是一種擴展的RS觸發器)和適當的反饋邏輯,可以實現二進制計數器或環形計數器等。這些計數器在數字電路設計中用于實現定時、分頻等功能。

3. 狀態機

狀態機是一種根據輸入信號和當前狀態來決定下一個狀態和輸出的系統。在狀態機的設計中,RS觸發器(或其變體)被用作存儲當前狀態的基本單元。通過組合多個觸發器并添加適當的控制邏輯和輸出邏輯,可以構建出能夠執行復雜控制流程的狀態機。這些狀態機在數字電路設計中用于實現各種自動控制和數據處理功能。

五、RS觸發器靜態特性的優化

為了提高RS觸發器的靜態特性,可以采取以下優化措施:

1. 改進電路設計

通過優化觸發器的電路設計,如選擇合適的邏輯門類型、調整電路布局和布線等,可以降低觸發器的功耗、提高抗干擾能力和穩定性。

2. 加強輸入信號處理

在觸發器的輸入端加入適當的信號處理電路(如濾波電路、限幅電路等),可以削弱輸入信號的噪聲和波動,從而提高觸發器的穩定性。

3. 引入同步機制

在某些應用中,為了避免觸發器在異步信號作用下產生不穩定狀態,可以引入同步機制。例如,使用同步RS觸發器代替普通的RS觸發器,通過時鐘信號來控制觸發器的狀態轉換過程。

六、結論

RS觸發器的靜態特性是其作為存儲單元和數字電路基本元件的重要基礎。通過保持狀態不變、滿足輸入信號的約束條件以及優化電路設計等措施,可以確保RS觸發器在各種應用場景中穩定可靠地工作。隨著電子技術的不斷發展,RS觸發器及其變體將繼續在數字電路設計中發揮重要作用。

-

RS觸發器

+關注

關注

3文章

101瀏覽量

17892 -

數字電路

+關注

關注

193文章

1600瀏覽量

80497 -

靜態特性

+關注

關注

0文章

21瀏覽量

9486

發布評論請先 登錄

相關推薦

RS觸發器工作原理_RS觸發器邏輯功能_RS觸發器和SR觸發器的區別

RS觸發器是什么?解讀rs觸發器的作用和數字電路中的rs觸發器的作用

RS觸發器的靜態特性分析

RS觸發器的靜態特性分析

評論