1. 時(shí)鐘資源概述

時(shí)鐘設(shè)施提供了一系列的低電容、低抖動的互聯(lián)線,這些互聯(lián)線非常適合于傳輸高頻信號、最大量減小時(shí)鐘抖動。這些連線資源可以和DCM、PLL等實(shí)現(xiàn)連接。

每一種Spartan-6芯片提供16個(gè)高速、低抖動的全局時(shí)鐘資源用于優(yōu)化性能;這些資源可以背Xilinx工具自動地使用,即使時(shí)鐘頻率相對較低,使用時(shí)鐘資源來消除潛在的時(shí)序冒險(xiǎn)仍然是十分重要的,每一個(gè)Spartan-6 FPGA提供40個(gè)超高速、低抖動的IO局部時(shí)鐘資源(32個(gè)BUFIO2S和8個(gè)BUFPLL)這些IO局部時(shí)鐘資源是為IO Serializer和de-serializer電路服務(wù)的。

Spartan-6 FPGA的時(shí)鐘資源主要由四種類型的連接器構(gòu)成:

全局時(shí)鐘輸入引腳(GCLK)

全局時(shí)鐘多路復(fù)用器(BUFG、BUFGMUX)

IO時(shí)鐘緩沖器(BUFIO2、BUFIO2_2CLK、BUFPLL)

水平方向時(shí)鐘布線緩沖器(BUFH)

有兩種類型的時(shí)鐘網(wǎng)絡(luò):

為FPGA內(nèi)部邏輯資源提供低抖動時(shí)鐘資源的全局時(shí)鐘網(wǎng)絡(luò)

為SelectIIO邏輯資源提供高性能低抖動時(shí)鐘資源的IO局部時(shí)鐘網(wǎng)絡(luò)

BUFGMUX能夠在兩個(gè)全局時(shí)鐘資源之間進(jìn)行復(fù)用,也可以當(dāng)做普通的BUFG時(shí)鐘緩沖使用,這個(gè)時(shí)鐘緩沖只能夠直接驅(qū)動全局時(shí)鐘布線資源,只能夠驅(qū)動時(shí)鐘輸入;當(dāng)然,F(xiàn)PGA內(nèi)部邏輯觸發(fā)器的時(shí)鐘輸入也可以來自那些普通的布線資源,不過那些普通的布線資源會具有較大的時(shí)鐘抖動。

BUFPLL和BUFIO2用來驅(qū)動IO局部時(shí)鐘網(wǎng)絡(luò)的時(shí)鐘資源,這一特性限定了它們的使用目的,他們只能用于ISERDES或OSERDES這資源的輸入時(shí)鐘資源;

BUFIO2能夠驅(qū)動SDR和DDR的ISERDES2和OSERDES2的時(shí)鐘,BUFIO2能夠把GCLK或GTP_DUAL Tile的輸入時(shí)鐘布線到BUFG、DCM、PLL時(shí)鐘輸入。BUFIO2_2CLK能夠用來代替BUFIO2s使用在DDR的ISERDES2和OSERDES2的設(shè)計(jì)時(shí)鐘。

類似地,BUFPLL可以驅(qū)動SDR時(shí)鐘的IO時(shí)鐘網(wǎng)絡(luò),BUFPLL將PLL的CLKOUT0或CLKOUT1和IO局部時(shí)鐘網(wǎng)絡(luò)連接起來。

BUFH通過提供邏輯資源與全局時(shí)鐘布線水平區(qū)域的連接,使得芯片總體的低抖動時(shí)鐘資源更為豐富。

1.1. 全局時(shí)鐘結(jié)構(gòu)

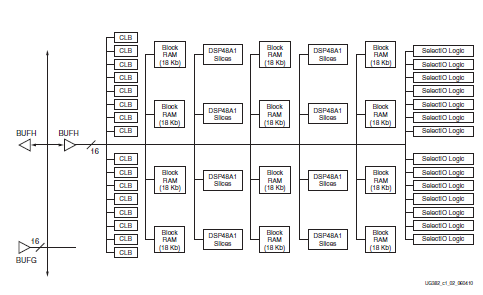

圖 1.1全局時(shí)鐘結(jié)構(gòu)

Spartan-6 FPGA的全局時(shí)鐘網(wǎng)絡(luò)由16個(gè)位于器件中心位置的BUFGMUX驅(qū)動,時(shí)鐘的輸入可以來自FPGA的上、下、左、右的bank,也可以來自PLL或DCM;16個(gè)BUFGMUX驅(qū)動vertical spine并經(jīng)vertical spine 往南北方向傳播,根據(jù)這條線路,時(shí)鐘水平延伸至HCLK時(shí)鐘列并經(jīng)HCLK時(shí)鐘列提供了訪問局部邏輯原語的路徑;每一個(gè)HCLK列左右兩邊各有16個(gè)水平時(shí)鐘緩沖BUFH驅(qū)動左右邏輯資源。

圖 1.2BUFH時(shí)鐘布線路徑

在Spartan-6 FPGA器件上,有32個(gè)GCLK輸入,但是只有16個(gè)全局時(shí)鐘緩沖,也就是說每一個(gè)全局時(shí)鐘緩沖只能被2個(gè)GCLK中的一個(gè)驅(qū)動,在兩個(gè)GCLK(假設(shè)為GCLK_A和GCLK_B共享BUFGMX_C)都需要使用的情況下,為了為用戶提供更多的靈活性,可以讓GCLK_A引腳布線到BUFGMUX_C,而GCLK_B使用BUFIO2間接地布線到另一個(gè)BUFGMUX_D。但是經(jīng)過BUFIO2布線的時(shí)鐘會出現(xiàn)延時(shí)。

表格 1.1 Bank0和Bank1共享全局時(shí)鐘資源不完全統(tǒng)計(jì)情況表

圖 1.3Bank0和Bank1的BUFGMUX的連接情況

圖 1.4Bank2和Bank3的BUFGMUX的連接情況

對于使用GTP Transceiver的設(shè)計(jì)來說,每一個(gè)GTP參考時(shí)鐘是和一個(gè)BUFIO2關(guān)聯(lián)在一起的,這可能影響B(tài)ank0和Bank2上的全局時(shí)鐘引腳的使用;對SDR接口來說,GCLK的引腳輸入與的沖突如表格 1.2所示,對DDR接口來說,GTP需要兩個(gè)BUFIO2,因?yàn)镈DR的需要將時(shí)鐘反轉(zhuǎn),DDR接口對GCLK引腳輸入的沖突如表格 1.3所示。

表格 1.2SDR接口使用中BUFIO2的輸入沖突

表格 1.3DDR接口使用中BUFIO2的輸入沖突

1.2. IO時(shí)鐘結(jié)構(gòu)

1.5IO時(shí)鐘結(jié)構(gòu)

所有的SelectIOn的邏輯資源(輸入寄存器、輸出寄存器、IDDR2、ODDR2、ISERDES2、OSERDES2)必須被來自BUFIO2的時(shí)鐘驅(qū)動;每個(gè)BUFIO2時(shí)鐘域有4個(gè)高速I時(shí)鐘,由4個(gè)專用BUFIO2 緩沖驅(qū)動;Spartan6 FPGA有4個(gè)BUFIO2時(shí)鐘域共32BUFIO2.

1.6BUFIO2時(shí)鐘域

2. 時(shí)鐘輸入

時(shí)鐘輸入引腳接受外部時(shí)鐘信號并且直接將其連接至BUFGMUX或者BUFIO2原語。當(dāng)然,時(shí)鐘引腳也可以用作普通IO。BUFIO2除了能將時(shí)鐘輸入到IO時(shí)鐘網(wǎng)絡(luò),BUFIO2也提供了專用的接往PLL/DCM或BUFG的時(shí)鐘路線

2.1經(jīng)BUFIO2布線的專用時(shí)鐘輸入

對Spartan-6 FPGA而言,專用的時(shí)鐘輸入引腳位于芯片邊沿的中心位置,下圖例舉了4Bank的Spartan-6 FPGA的時(shí)鐘引腳布局。

2.2四Bank Spartan-6 FPGA 時(shí)鐘引腳布局

3. 時(shí)鐘管理技術(shù)

Spartan-6 FPGA的CMT(時(shí)鐘管理單元)提供了非常靈活、高性能的時(shí)鐘;Spartan-6 FPGA的CMT模塊位于豎直的全局時(shí)鐘樹的中間列位置,每個(gè)CMT包含2個(gè)DCM、1個(gè)PLL。

3.1Spartan-6 FPGA CMT位置圖

3.2CMT結(jié)構(gòu)框圖

3.1. DCM的功能

DCM:Digital Clock Management,數(shù)字時(shí)鐘管理單元的英文縮寫。DCM擁有先進(jìn)的時(shí)鐘能力可將時(shí)鐘直接導(dǎo)入全局時(shí)鐘分布網(wǎng)絡(luò),DCM可以解決各種各樣的時(shí)鐘問題,尤其是在高性能、高頻率領(lǐng)域。

消除了時(shí)鐘抖動,提升了整個(gè)系統(tǒng)的性能

調(diào)節(jié)一個(gè)時(shí)鐘信號的相位

對輸入時(shí)鐘進(jìn)行倍頻或分頻,也能夠通過動態(tài)或靜態(tài)的提供乘除因子產(chǎn)生新的時(shí)鐘頻率。

使時(shí)鐘信號更健康,占空比穩(wěn)定在50%

鏡像、轉(zhuǎn)發(fā)、重緩沖一個(gè)時(shí)鐘信號,對輸入時(shí)鐘信號進(jìn)行去抖斜或轉(zhuǎn)換成差分IO電平。

時(shí)鐘輸入抖動過濾

擴(kuò)頻時(shí)鐘產(chǎn)生

振蕩器工作模式

3.3DCM結(jié)構(gòu)框圖

3.2. PLL的功能

PLL:Phase-Locked Loop,鎖相環(huán)的英文縮寫。Spartan-6 FPGA器件包含6個(gè)CMT Tile。PLL的主要目的是作為外部時(shí)鐘或內(nèi)部時(shí)鐘的抖動過濾器或頻率合成器。

3.4PLL結(jié)構(gòu)框圖

-

FPGA

+關(guān)注

關(guān)注

1626文章

21678瀏覽量

602022 -

Spartan-6

+關(guān)注

關(guān)注

4文章

38瀏覽量

17521

發(fā)布評論請先 登錄

相關(guān)推薦

Spartan-6 FPGA工業(yè)影像目標(biāo)設(shè)計(jì)平臺(Xilin

基于Spartan-6的FPGA SP601開發(fā)設(shè)計(jì)方案

一文詳解Spartan-6系列IO Tile結(jié)構(gòu)

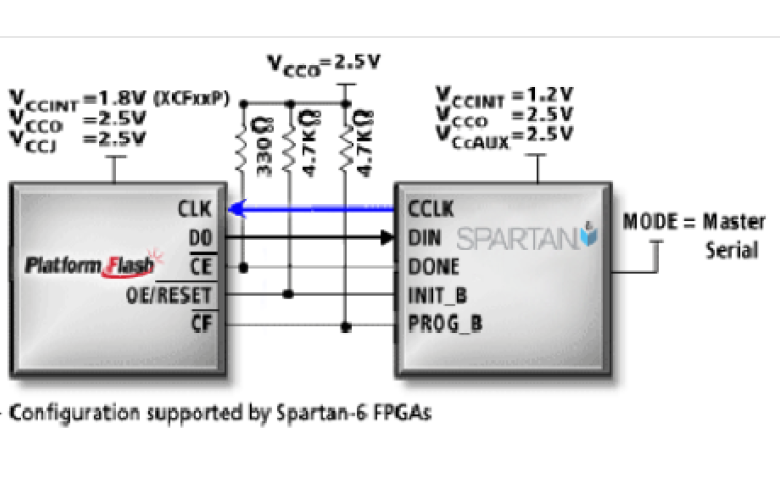

Spartan-6 FPGA Configuration User Guide

Spartan-6 FPGA視頻平臺的演示介紹

ISE 14.7 for Spartan-6 FPGA的使用

Spartan-6 FPGA中的DCM功能介紹

spartan-6 FPGA的設(shè)備引出線和包裝規(guī)格介紹

spartan-6 FPGA的時(shí)鐘資源的用戶指南資料免費(fèi)下載

spartan-6 FPGA可配置邏輯塊的用戶指南資料免費(fèi)下載

Spartan-6 FPGA的配置教程說明

Spartan-6 FPGA的時(shí)鐘資源及結(jié)構(gòu)介紹

Spartan-6 FPGA的時(shí)鐘資源及結(jié)構(gòu)介紹

評論