Model4芯片是一款高性能的全高清顯示和智能控制SOC,采用國產自主 64 位高算力 RISC-V 內核,提供了豐富的互聯外設接口,具備大容量存儲和極強的擴展性。片內存儲BROM 32KB、SRAM 96KB以及DRAM SiP 16bit KGD(兩種規格可選:DDR2 512Mb、 DDR3 1Gb),存儲接口QSPI 支持 SPI NAND Flash / SPI Nor Flash,支持eMMC5.0接口。

如此多的存儲器和存儲接口,究竟有何區別?本文將以半導體存儲類型為主線,帶大家了解各個存儲器的特點、優勢以及聯系。

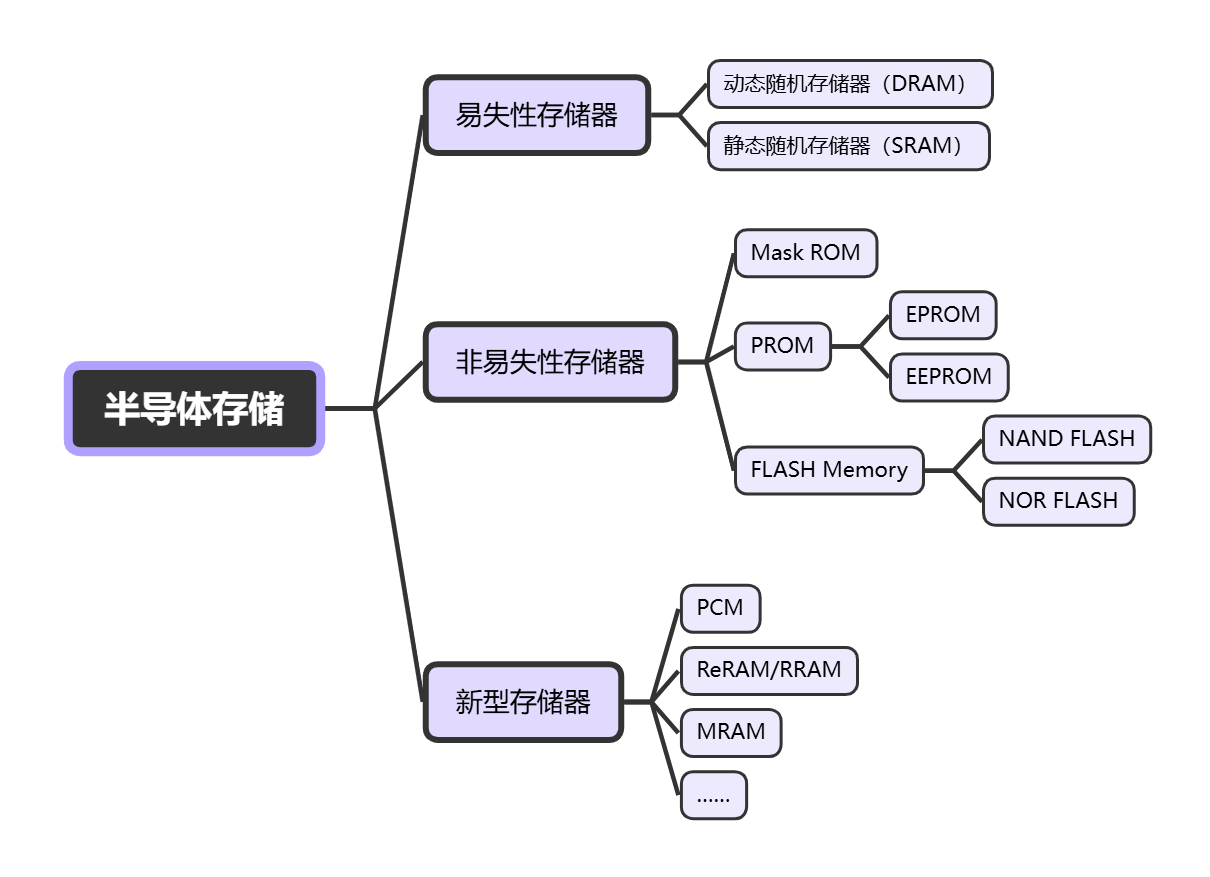

一、半導體存儲分類

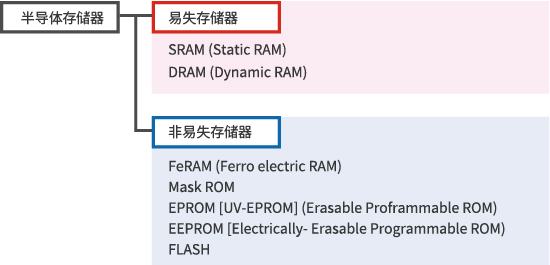

在介紹之前,我們先看一張圖,以便理解。

現代存儲技術,概括起來分為三部分:磁性存儲(磁帶、軟盤等)、光學存儲(DVD、藍光光盤等)、半導體存儲。我們今天要介紹的就是以“半導體集成電路”作為存儲媒介的存儲器——半導體存儲。

半導體存儲主要分為易失性(VM)存儲器與非易失性(NVM)存儲器。

(一)易失性存儲器(VN)

易失性存儲器主要分為DRAM和SRAM兩種。

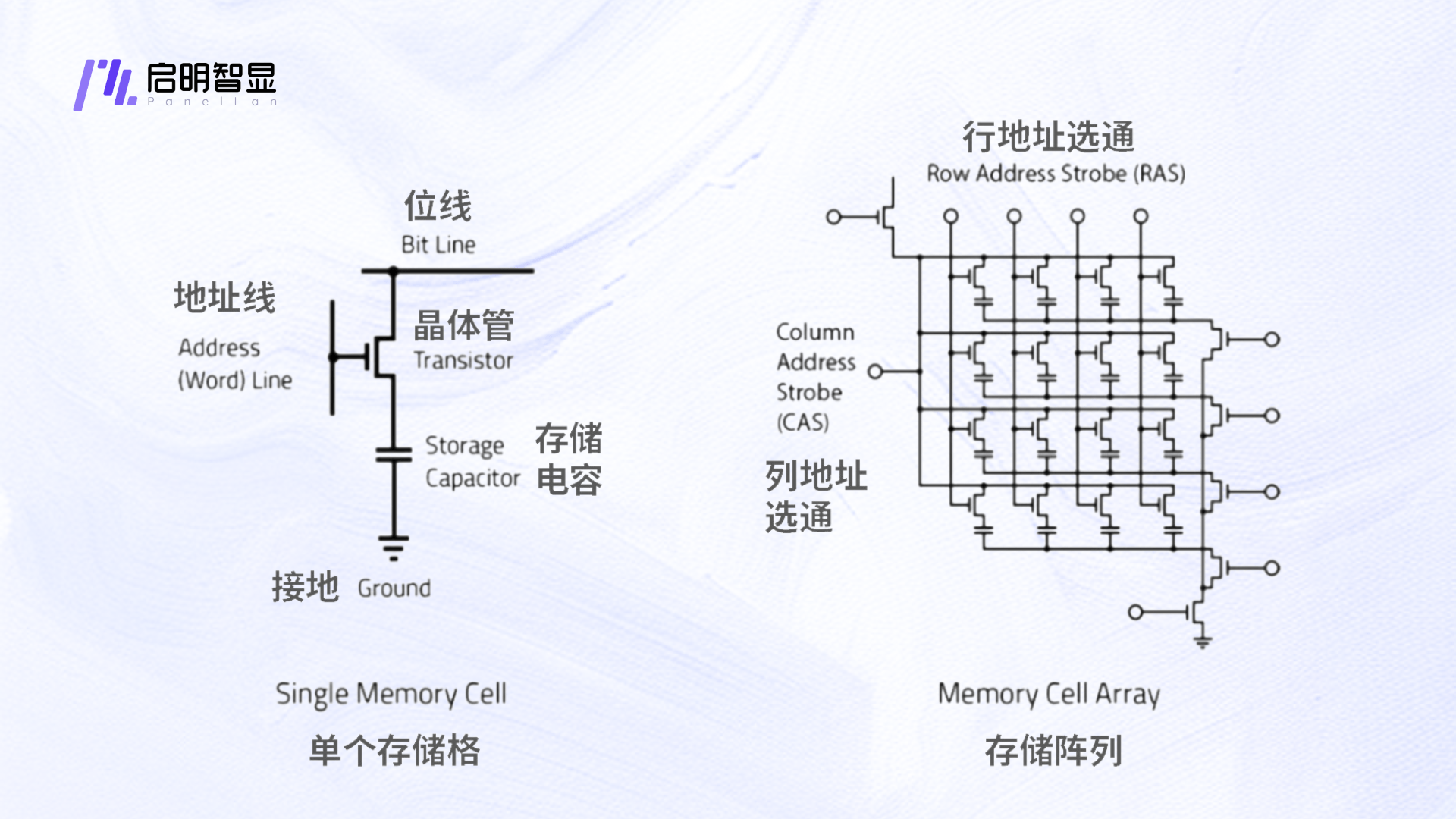

1.DRAM

DRAM由許多重復的位元格(Bit Cell)組成,每一個基本單元由一個電容和一個晶體管構成(又稱1T1C結構)。電容中存儲電荷量的多寡,用于表示“0”和“1”。而晶體管,則用來控制電容的充放電。

由于電容會存在漏電現象。所以,必須在數據改變或斷電前,進行周期性“動態”充電,保持電勢。否則,就會丟失數據。因此,DRAM才被稱為“動態”隨機存儲器。

DRAM一直是計算機、手機內存的主流方案。計算機的內存條(DDR)、顯卡的顯存(GDDR)、手機的運行內存(LPDDR),都是DRAM的一種。(DDR基本是指DDR SDRAM,雙倍速率同步動態隨機存儲器。)

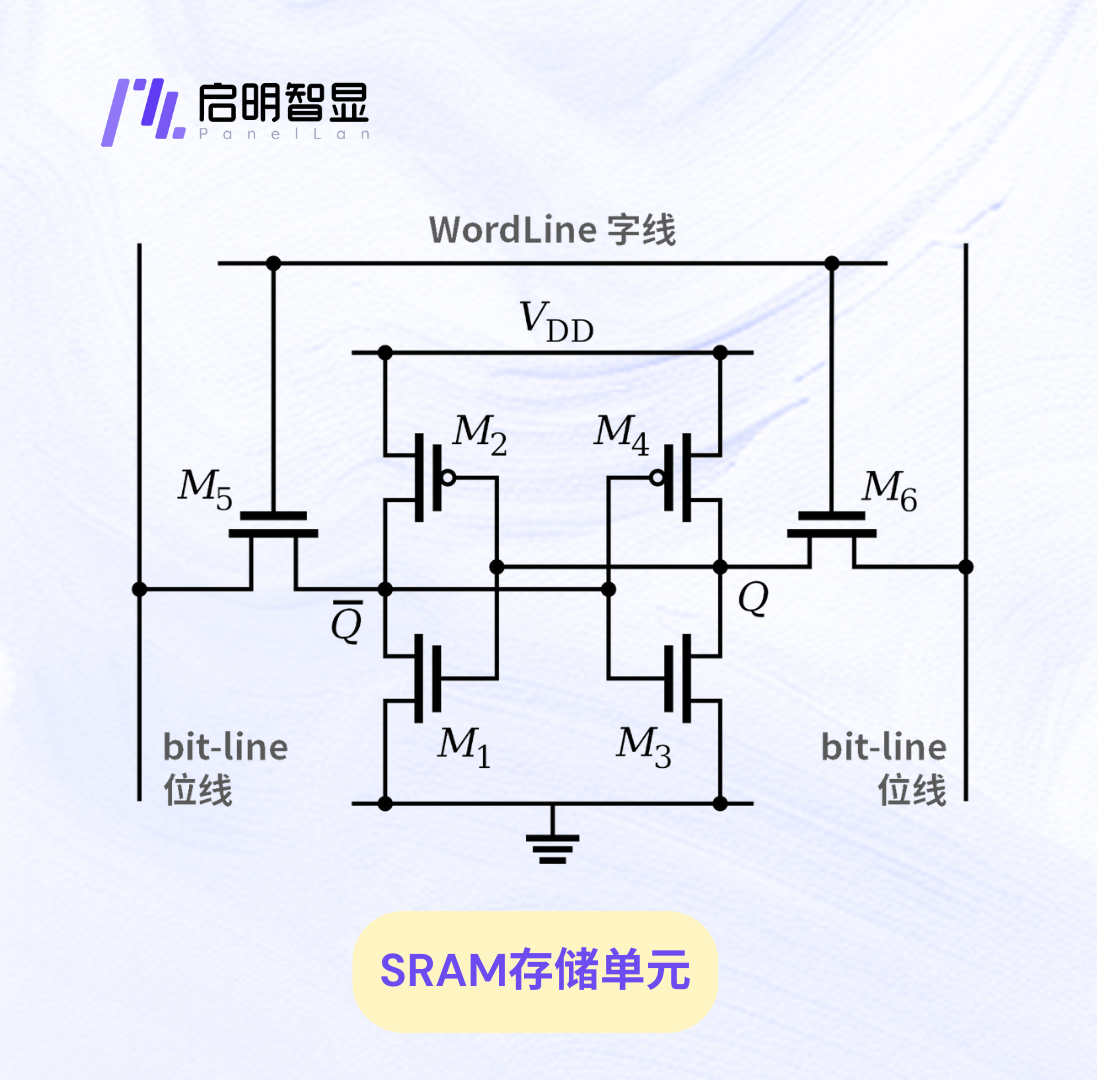

2.SRAM

SRAM是CPU緩存所使用的技術,它的架構相較于DRAM要復雜很多。

SRAM的基本單元,則最少由6管晶體管組成:4個場效應管(M1, M2, M3, M4)構成兩個交叉耦合的反相器,2個場效應管(M5, M6)用于讀寫的位線(Bit Line)的控制開關,通過這些場效應管構成一個鎖存器(觸發器),并在通電時鎖住二進制數0和1。因此,SRAM被稱為“靜態隨機存儲器”。

SRAM不需要定期刷新,響應速度非常快,但價格昂貴,用于CPU的一級緩沖、二級緩沖。Model4中也有SRAM,具備96KB的SRAM,用于程序運行時變量、堆棧的暫存等,非常適用于需要大量數據計算的場合。

(二)非易失性存儲器(NVM)

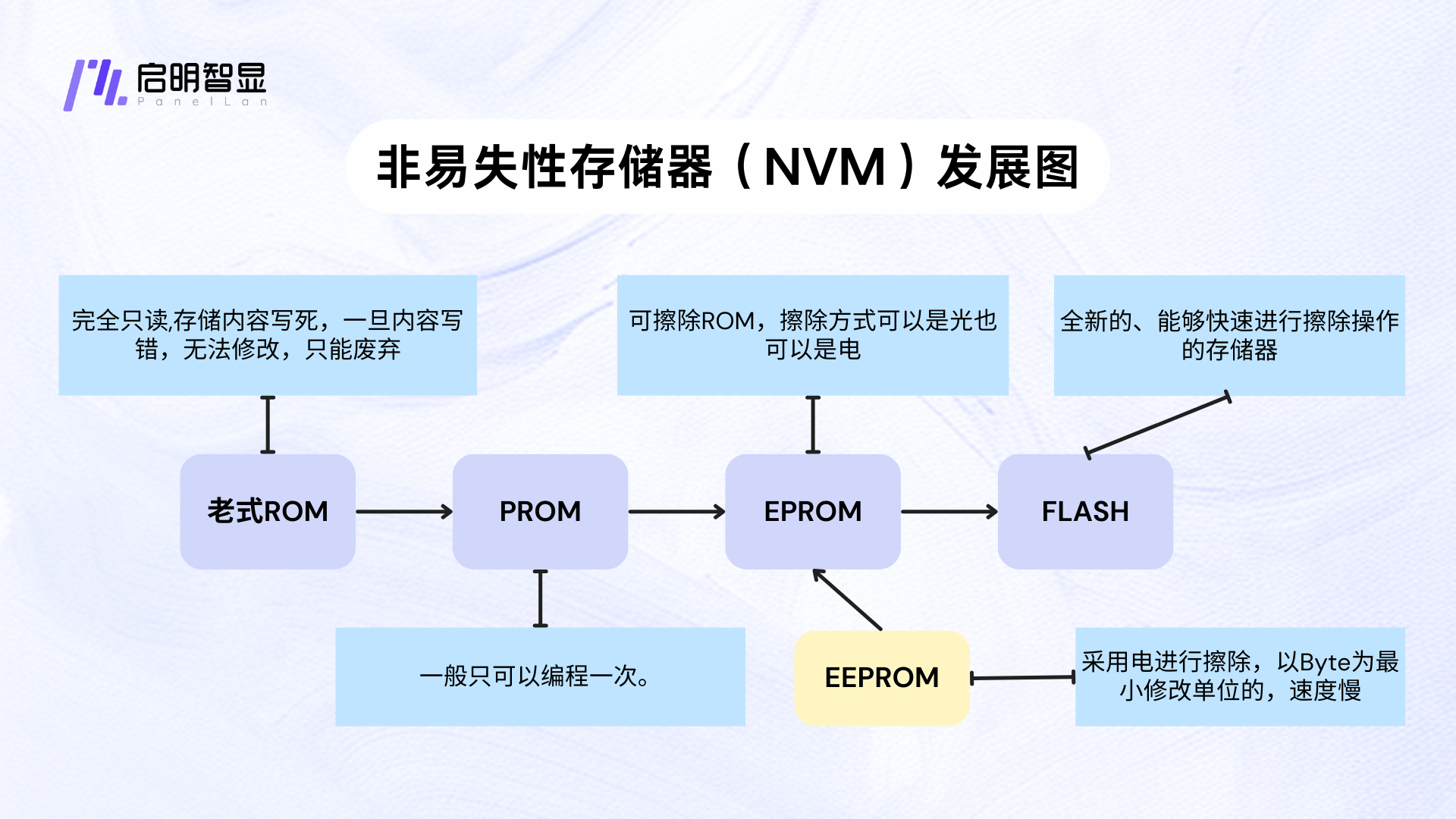

非易失性存儲器產品的技術路線比較多,早起NVM的發展可以簡要概括為下圖:

早期的這些NVM要不就是無法修改,要不就是修改方式都太慢。直到上世紀80年代,日本東芝的技術專家——舛岡富士雄,發明了一種全新的、能夠快速進行擦除操作的存儲器,也就是——Flash(閃存)。

Flash存儲是以“塊”為單位進行擦除的。常見的塊大小為128KB和256KB。1KB是1024個bit,比起EEPROM按bit擦除,快了幾個數量級。目前,FLASH的主流代表產品也只有兩個,即:NOR Flash和NAND Flash。

1. NOR Flash

NOR Flash屬于代碼型閃存芯片,其主要特點是芯片內執行(XIP,Execute In Place),即應用程序不必再把代碼讀到系統RAM中,而是可以直接在Flash閃存內運行。

所以,NOR Flash適合用來存儲代碼及部分數據,可靠性高、讀取速度快,在中低容量應用時具備性能和成本上的優勢。

但是,NOR Flash的寫入和擦除速度很慢,而且體積是NAND Flash的兩倍,所以用途受到了很多限制,市場占比比較低。

近年來,NOR Flash的應用有所回升,市場回暖。低功耗藍牙模塊、TWS耳機、手機觸控和指紋、可穿戴設備、汽車電子和工業控制等領域,使用NOR Flash比較多。

2. NAND Flash

NAND Flash屬于數據型閃存芯片,可以實現大容量存儲。它基于浮柵晶體管設計,通過浮柵來鎖存電荷,由于浮柵是電隔離的,所以即使在去除電壓之后,到達柵極的電子也會被捕獲。這就是閃存非易失性的原理所在。數據存儲在這類設備中,即使斷電也不會丟失。

NAND Flash以頁為單位讀寫數據,以塊為單位擦除數據,故其寫入和擦除速度雖比DRAM大約慢3-4個數量級,卻也比傳統的機械硬盤快3個數量級,被廣泛用于eMMC/EMCP、U盤、SSD等市場。

相對于機械硬盤等傳統存儲介質,采用NAND Flash 芯片的SD 卡、固態硬盤等存儲裝置沒有機械結構,無噪音、壽命長、功耗低、可靠性高、體積小、讀寫速度快、工作溫度范圍廣,是未來大容量存儲的發展方向。隨著大數據時代的到來,NAND Flash 芯片將在未來得到巨大發展。

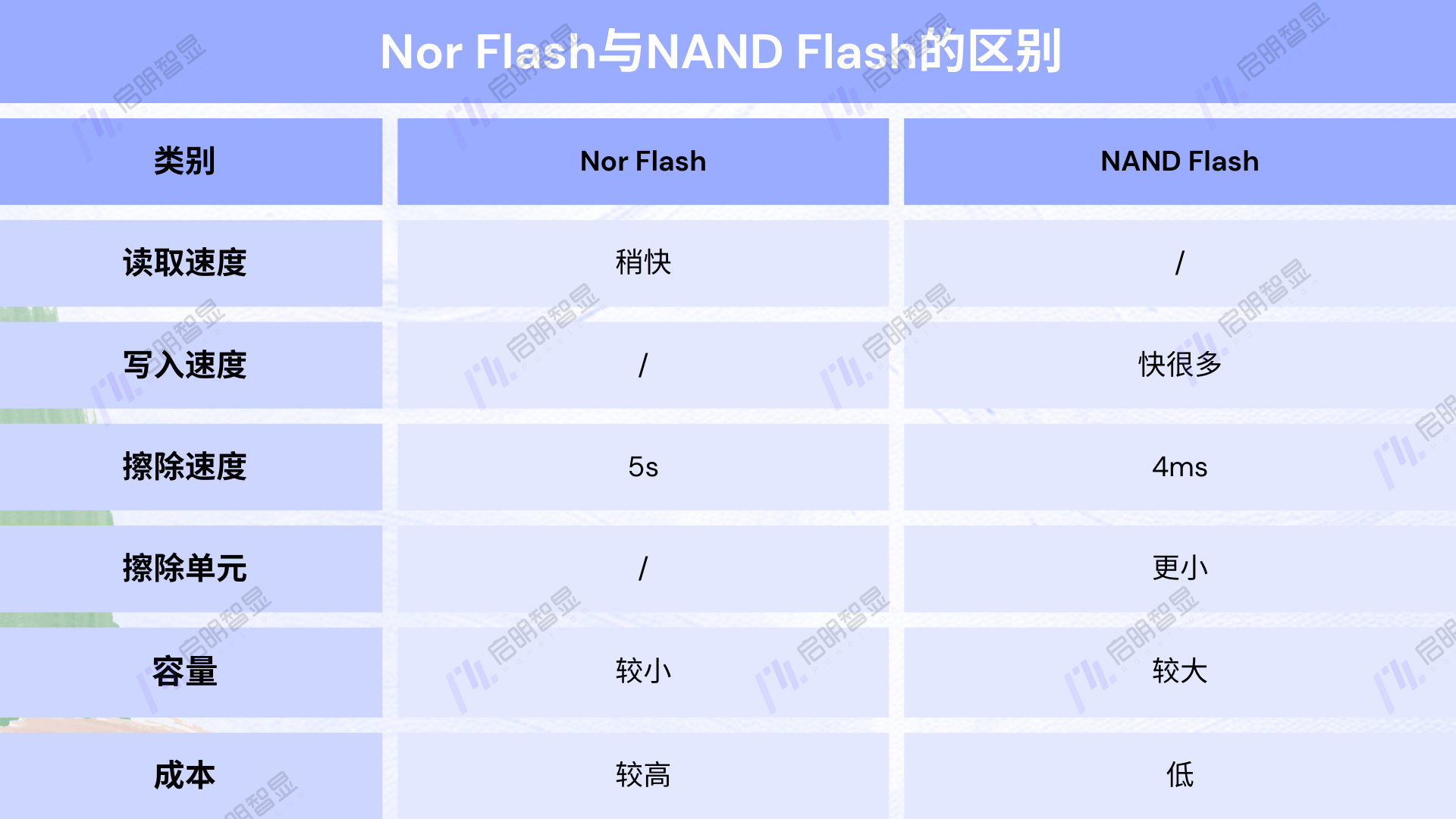

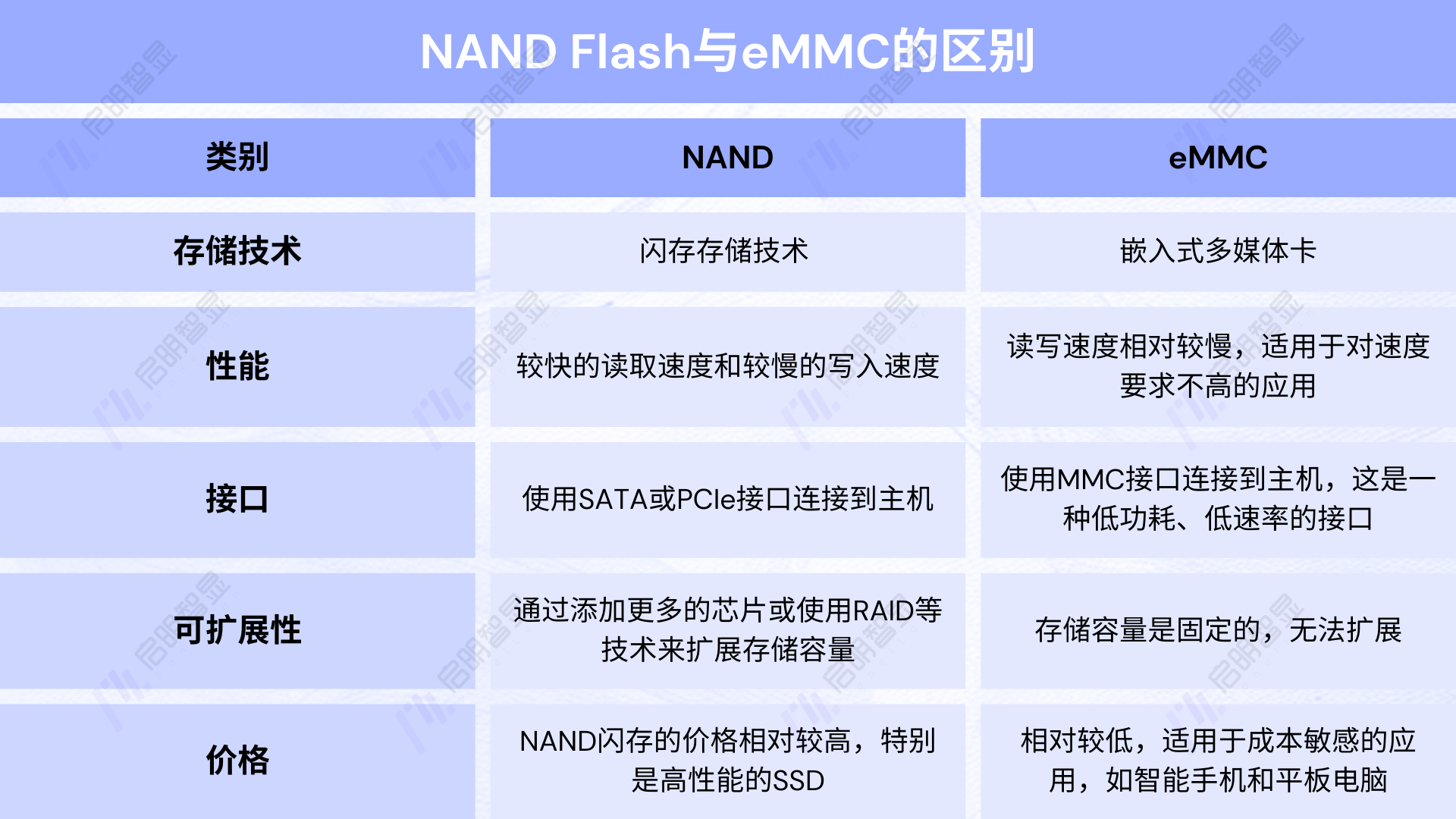

3. Nor Flash與NAND Flash的區別

二、eMMC與UFS

(一)eMMC

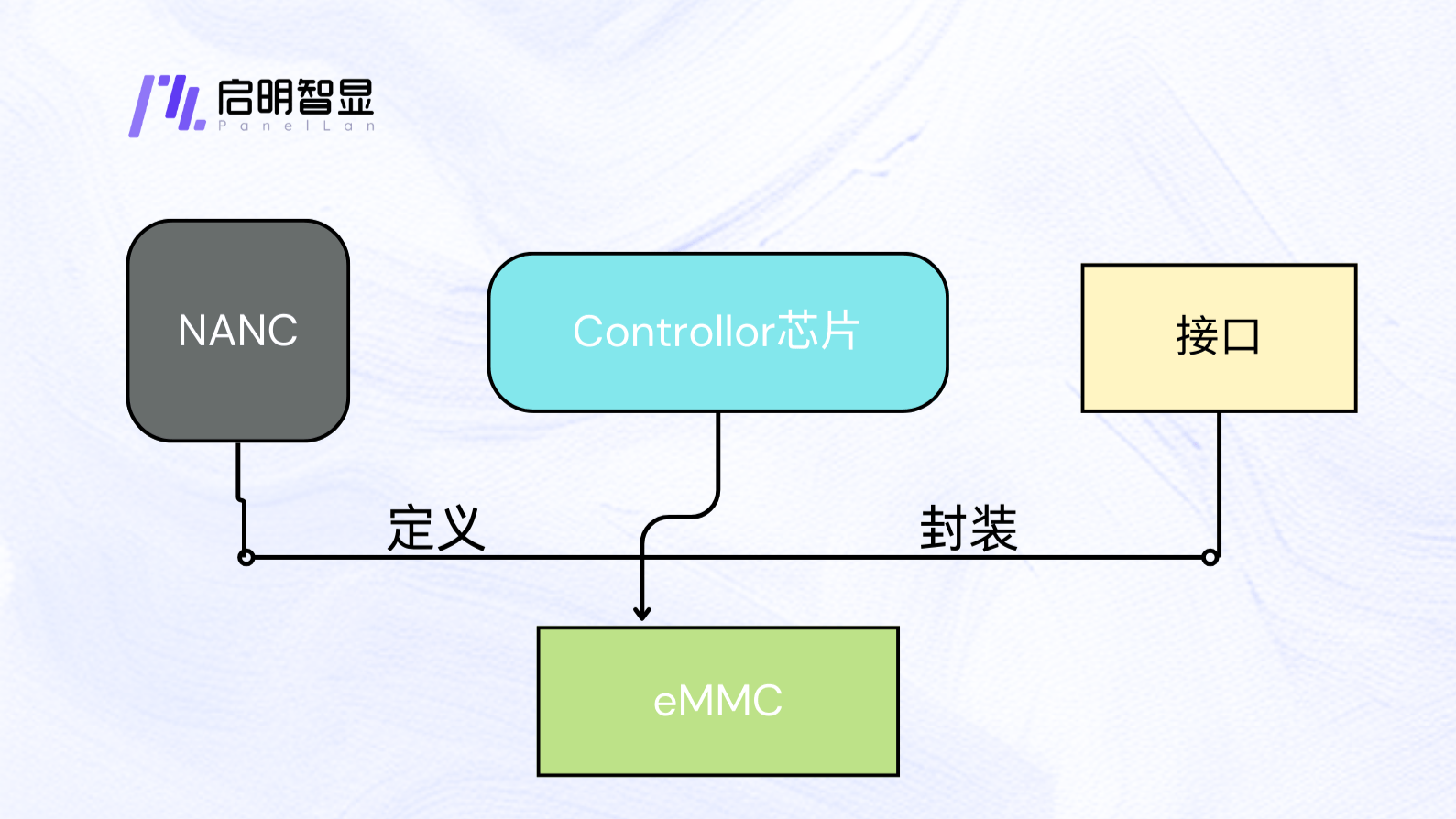

eMMC ( Embedded Multi Media Card) 采用統一的MMC標準接口, 把高密度NAND Flash以及MMC Controller封裝在一顆BGA芯片中。針對Flash的特性,產品內部已經包含了Flash管理技術,包括錯誤探測和糾正,flash平均擦寫,壞塊管理,掉電保護等技術。用戶無需擔心產品內部flash晶圓制程和工藝的變化。同時eMMC單顆芯片為主板內部節省更多的空間。

簡單地說,eMMC=Nand Flash+控制器+標準封裝。

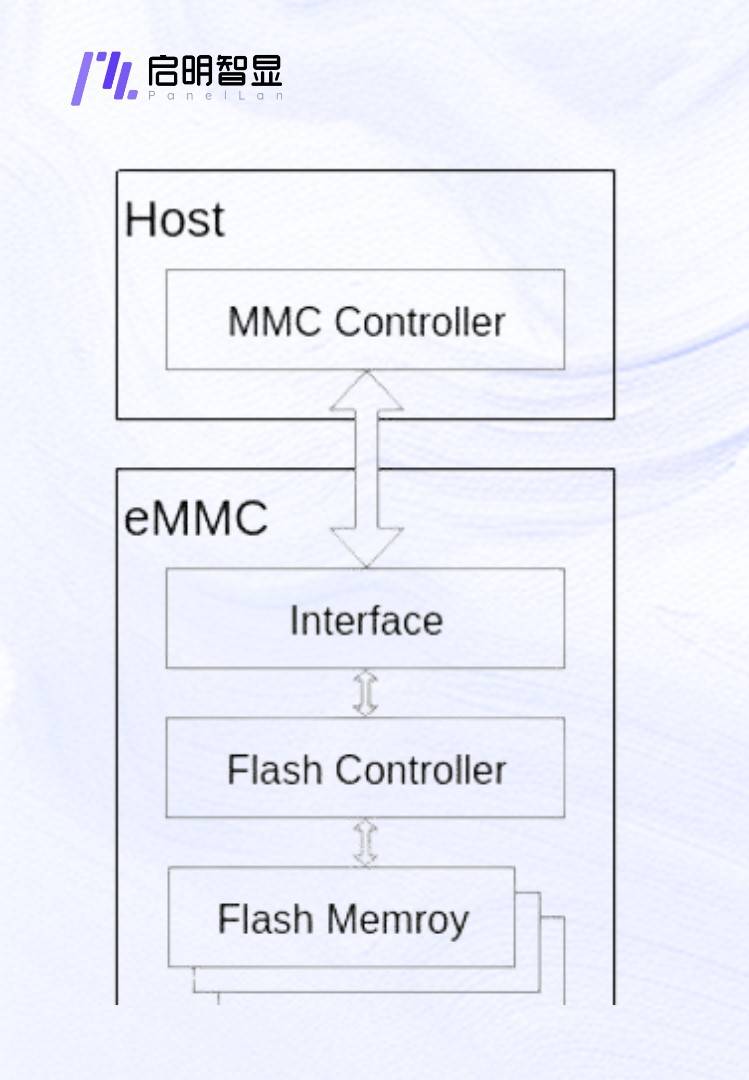

eMMC的整體架構如下圖片所示:

eMMC 則在其內部集成了 Flash Controller,用于完成擦寫均衡、壞塊理、ECC校驗等功能,讓 Host 端專注于上層業務,省去對 NAND Flash 進行特殊的處理。

eMMC具有以下優勢:

1.簡化類手機產品存儲器的設計。

2.更新速度快。

3.加速產品研發速度。

它與NAND Flash有何區別?

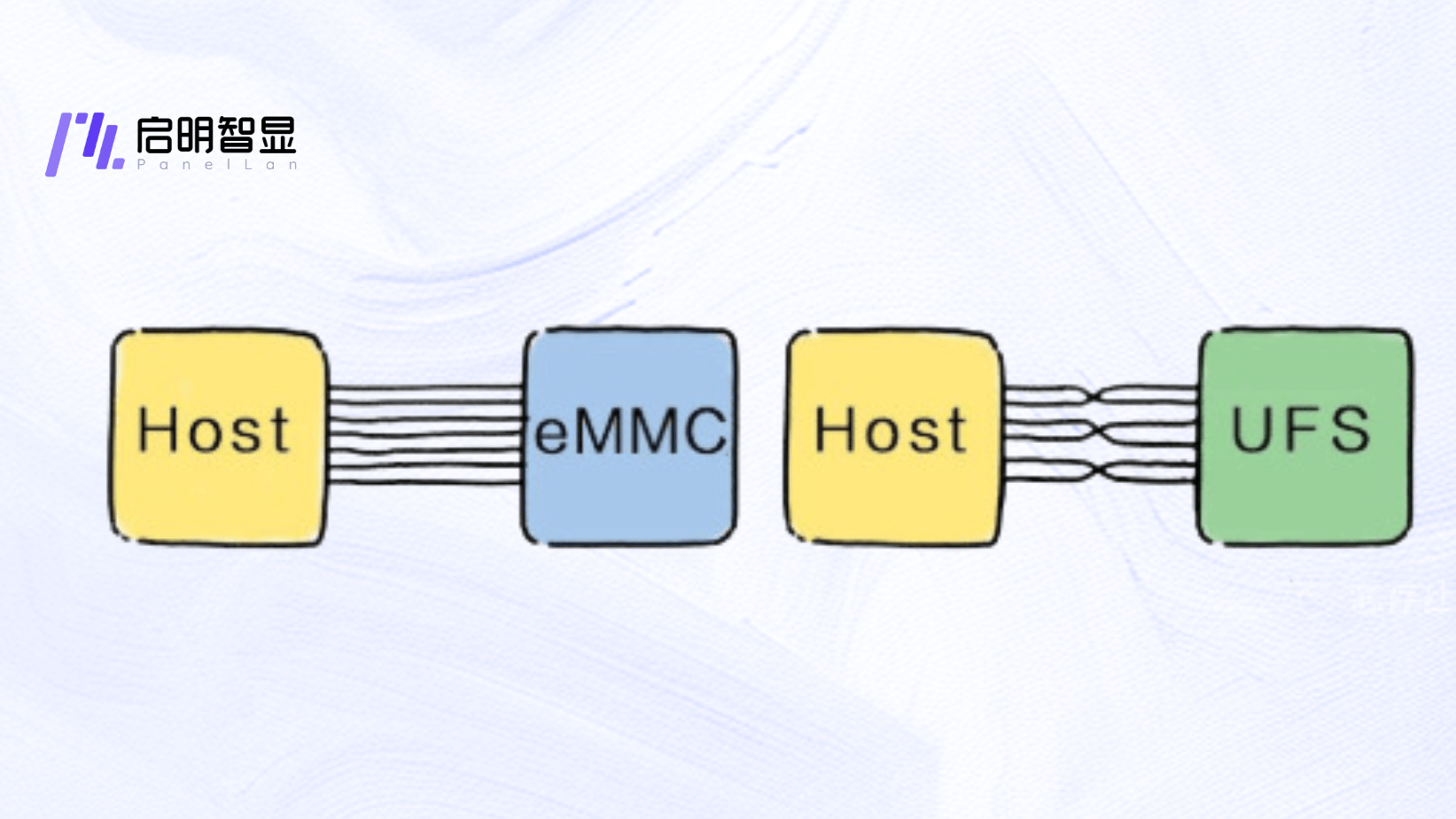

(二)UFS

UFS:Univeral Flash Storage,我們可以將它視為eMMC的進階版,是由多個閃存芯片、主控、緩存組成的陣列式存儲模塊。UFS彌補了eMMC僅支持半雙工運行(讀寫必須分開執行)的缺陷,可以實現全雙工運行,所以性能得以翻番。

三、DDR、LPDDR

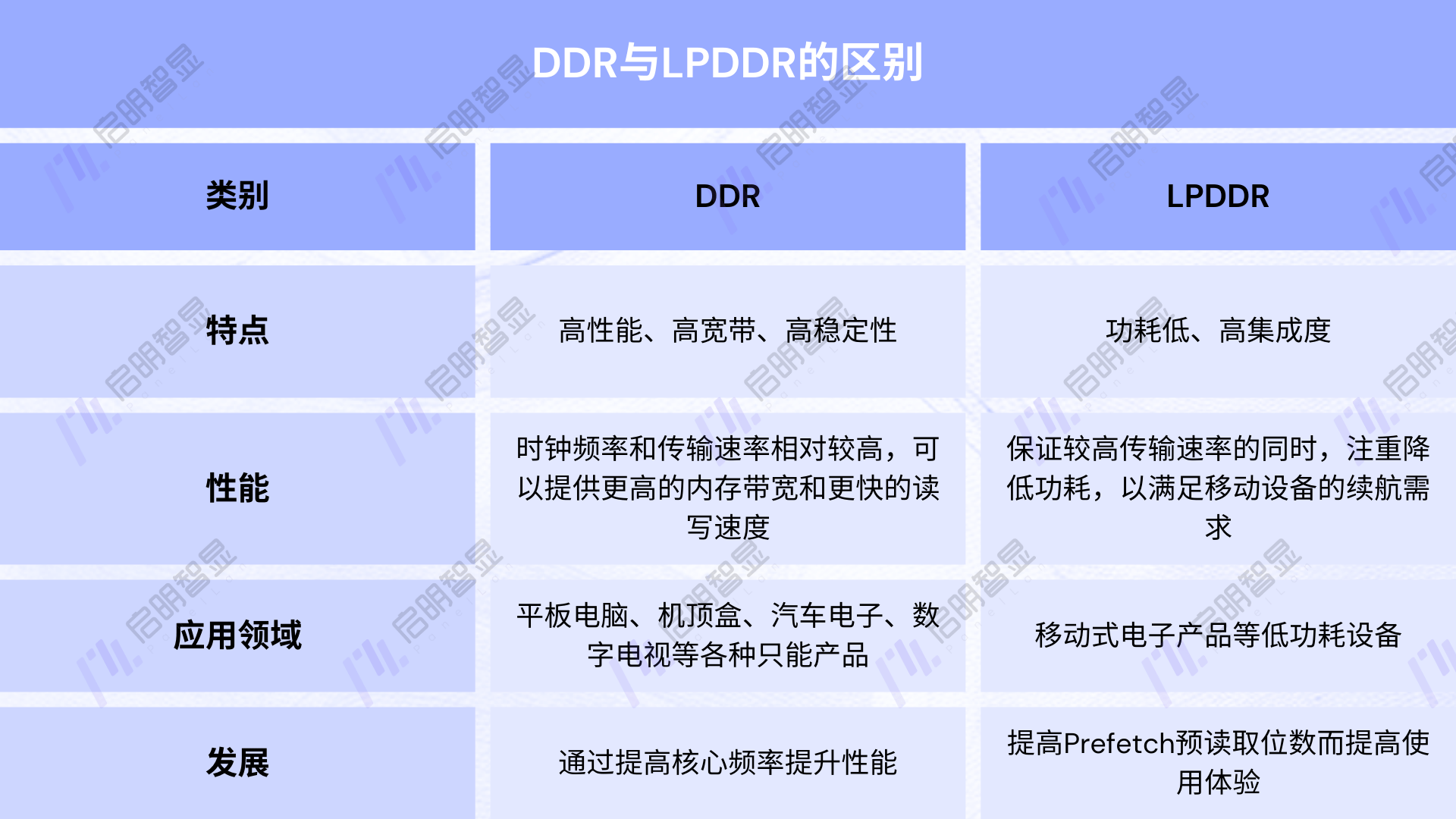

DDR全稱Double Data Rate雙倍速率同步動態隨機存儲器,嚴格的來講,DDR應該叫DDR SDRAM。雖然美國固態技術協會2018年宣布正式發布DDR5標準,但實際上最終的規范要到2020年才能完成,其目標是將內存帶寬在DDR4基礎上翻倍,速率3200MT/s起,最高可達6400MT/s,電壓則從1.2V降至1.1V,功耗減少30%。

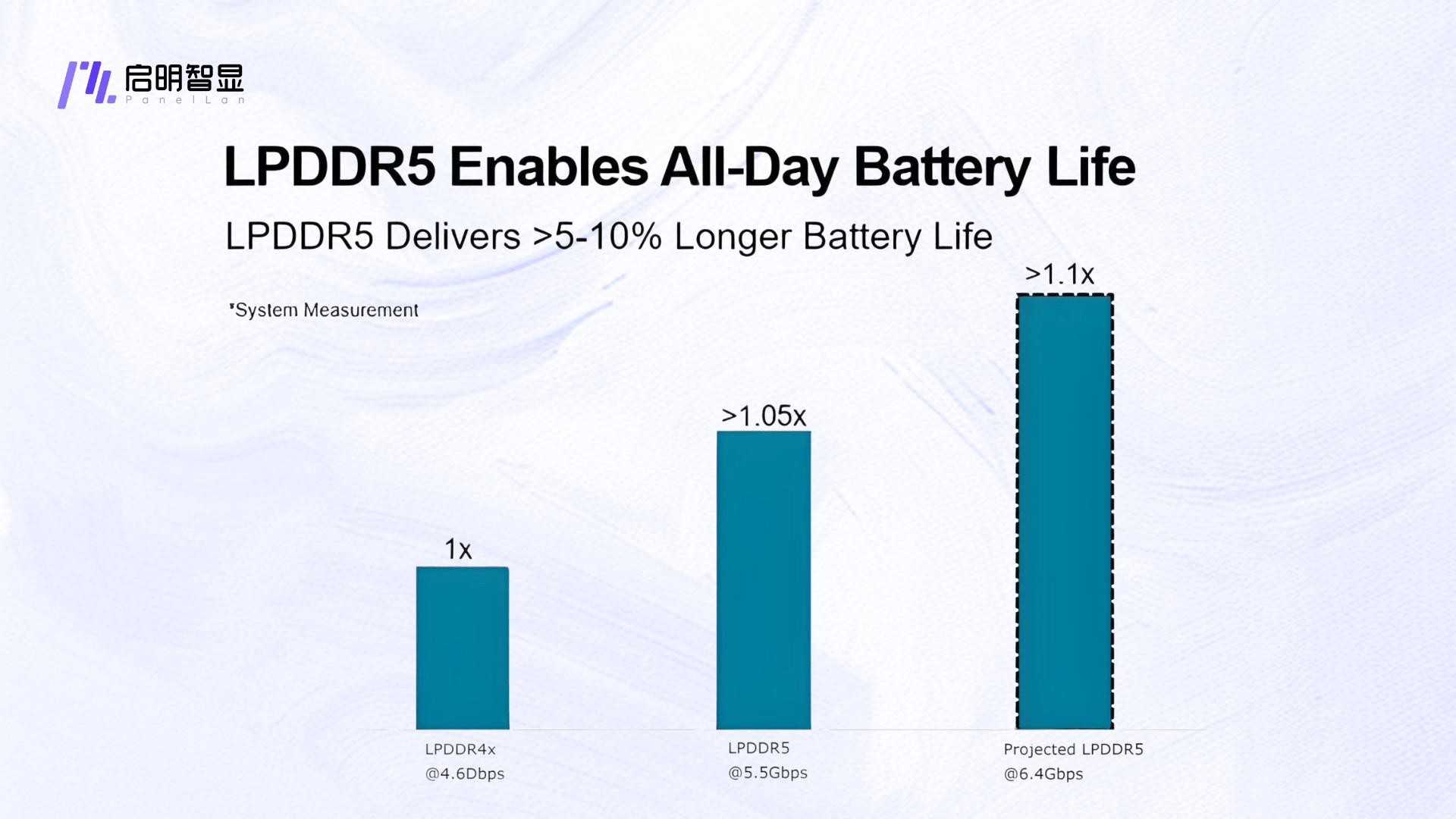

LPDDR是在DDR的基礎上多了LP(Low Power)前綴,全稱是Low Power Double Data Rate SDRAM,簡稱“低功耗內存”是DDR的一種,以低功耗和小體積著稱。目前最新的標準LPDDR5被稱為5G時代的標配,但目前市場上的主流依然是LPDDR3/4X。

DDR與LPDDR的區別:

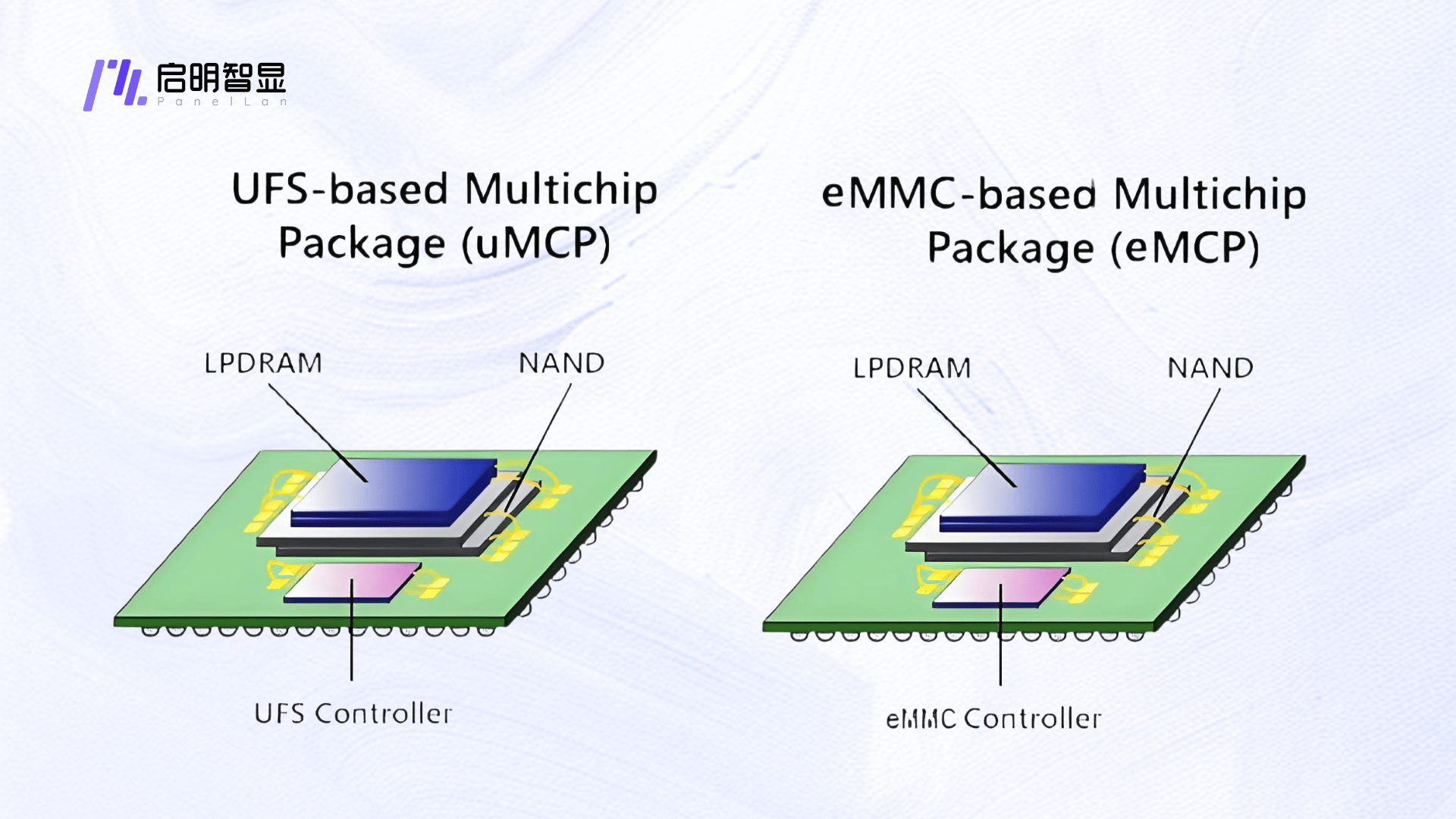

四、eMCP與uMCP

eMCP是結合eMMC和LPDDR封裝而成的智慧型手機記憶體標準,與傳統的MCP相較之下,eMCP因為有內建的NAND Flash控制晶片,可以減少主晶片運算的負擔,并且管理更大容量的快閃記憶體。以外型設計來看,不論是eMCP或是eMMC內嵌式記憶體設計概念,都是為了讓智慧型手機的外型厚度更薄,更省空間。

uMCP是結合了UFS和LPDDR封裝而成的智慧型手機記憶體標準,與eMCP相比,國產的uMCP在性能上更為突出,提供了更高的性能和功率節省。

總結

綜上,我們能看到內存和存儲器不斷地向著低功耗、高性能發展,也理解了各個內存、存儲器的特點與優勢。從而我們也能得出一個結論:Model4芯片充分融合了高性能內存、存儲以及存儲接口,結合高響應速度的96KB的SRAM以及64MB DDR2存儲,支持接入NAND Flash 和Nor Flash,支持eMMC5.0接口,具備高性能、高穩定性的特點。

-

芯片

+關注

關注

450文章

49639瀏覽量

417240 -

存儲器

+關注

關注

38文章

7366瀏覽量

163102 -

內存

+關注

關注

8文章

2903瀏覽量

73548

發布評論請先 登錄

相關推薦

半導體存儲器科普|從內存、存儲器看國產工業級HMI芯片Model4性能

半導體存儲器科普|從內存、存儲器看國產工業級HMI芯片Model4性能

評論