獲得高頻輸出的方法(第一部:鎖相環(huán)電路)

鎖相環(huán)電路概略與愛普生產(chǎn)品陣容

【序文】

近年,伴隨影像傳輸?shù)绕占埃歉删W(wǎng)中流過的通信量有增無減,通信的高速、大容量化進(jìn)展迅速。在這種情況下,高速化通信基礎(chǔ)設(shè)施對高頻且輸出信號穩(wěn)定的基準(zhǔn)信號源的需求十分強(qiáng)烈。

通常,從 MHz 頻帶的 AT 型石英晶體獲得高頻振蕩時(shí)需要將石英片加工得很薄(理由是 AT 型石英晶體的頻率因其厚度而定),這造成在加工方法、機(jī)械性強(qiáng)度和容易起振等方面存在局限。雖然將受加工精度的影響,但石英晶體以基波起振高頻時(shí)的上限一般為 60MHz 左右。因此,本公司把 60MHz 以上定為高頻領(lǐng)域。穩(wěn)定輸出高頻基準(zhǔn)信號并不簡單,愛普生擁有四種方法(技術(shù))實(shí)現(xiàn)高頻領(lǐng)域:第一種方法是使用有較易處理的 20MHz 頻帶起振頻率的AT 型石英晶體單元,利用倍頻電路或鎖相環(huán)(PLL)電路輸出穩(wěn)定的高頻基準(zhǔn)信號;第二種方法是使用表面聲波SAW 諧振器輸出高頻基準(zhǔn)信號,表面聲波 SAW 諧振器利用彈性表面聲波(SAW/Surface Acoustic Wave)以基波直接起振高頻;第三種方法是應(yīng)用愛普生所持有的 QMEMS 技術(shù),制造出僅將振動部分加工變薄的反向臺型 AT 型石英晶體單元,以此產(chǎn)生穩(wěn)定的高頻基準(zhǔn)信號;第四種方法是使用 AT 型石英晶體單元的高頻振動的振動模式(諧波)輸出穩(wěn)定的高頻基準(zhǔn)信號。本次就第一種方法、即倍頻電路(這里所稱的倍頻電路是指抽出高次諧波的模擬倍頻)和鎖相環(huán)電路的概略進(jìn)行解說。

【1】輸出 n 倍高頻的倍頻電路

倍頻電路是指把某一頻率的電氣信號轉(zhuǎn)換為 n 倍高頻的電路。一般的振蕩電路輸出信號具有一定的 Tr、Tf、Voh和 Vol 時(shí),其波形中將包含高諧波成份。倍頻電路利用這些高諧波產(chǎn)生有意加強(qiáng)了 n 次成份的信號,并用濾波器抽出 n 次成份。由于使用高諧波,因此可以獲得抖動小于鎖相環(huán)電路的輸出頻率。然而,若欲只抽出 n 次高諧波,則要求在選擇石英晶體單元和設(shè)計(jì)起振電路時(shí)加以注意。例如需要使用頻帶窄、高衰減的帶通濾波器(BPF),把n/2 次以下的分諧波衰減掉,以便抑制抖動;還要使輸入信號在 n 次高諧波附近不帶噪音(失真)等。因此,為了得到高頻,產(chǎn)品中大多使用鎖相環(huán)電路。在下一章中,我們將說明鎖相環(huán)電路。

【2】鎖相環(huán)電路

這里說明產(chǎn)生穩(wěn)定高頻的另一項(xiàng)技術(shù)――鎖相環(huán)電路。

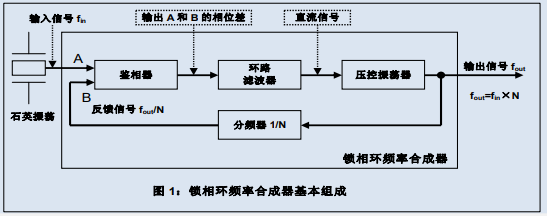

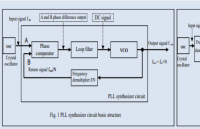

伴隨搭載無線通信儀器的設(shè)備的普及,用于無線通信的半導(dǎo)體集成電路技術(shù)有了飛躍性的進(jìn)展。其中,鎖相環(huán)電路技術(shù)的進(jìn)步尤為突出。鎖相環(huán)電路產(chǎn)生與輸入的基準(zhǔn)信號相同步的輸出信號。該電路的基本組成是鑒相器、環(huán)路濾波器和壓控振蕩器(VCO)。它將正確地產(chǎn)生與輸入信號相同步的信號。與倍頻電路不同的是,鎖相環(huán)電路不直接使用輸入信號制作輸出信號。在鎖相環(huán)電路中,由壓控振蕩器(VCO)產(chǎn)生與輸入信號相同頻率的同步信號。

在鎖相環(huán)電路的壓控振蕩器輸出和鑒相器的輸入之間連接分頻器,通過使輸入信號與分頻后的信號相同步,從而將壓控振蕩器的輸出頻率控制在分頻倍數(shù)的頻率。使用石英晶體振蕩器等能夠產(chǎn)生穩(wěn)定頻率,并轉(zhuǎn)換分頻器的分頻數(shù),就能使壓控振蕩器的輸出達(dá)到石英晶體振蕩器同等精度且等于分頻倍數(shù)頻率的信號。這就是頻率合成器的原理。

應(yīng)用該原理,把 AT 型石英晶體單元輸出的 MHz 頻帶頻率輸入到鎖相環(huán)頻率合成器,就能夠產(chǎn)生用于無線通信的 GHz 頻帶載波信號。

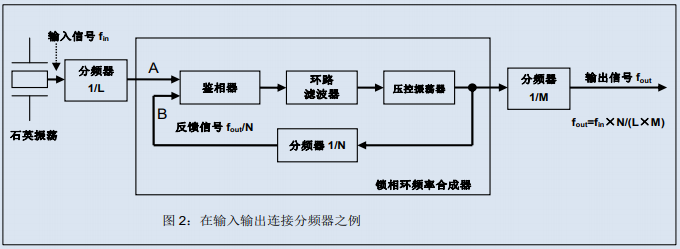

使用鎖相環(huán)頻率合成器獲得大于輸入頻率幾倍的頻率時(shí),分頻器的使用方法是關(guān)鍵。獲得輸入頻率的 N 倍輸出的電路結(jié)構(gòu)如圖 1 所示。為了對輸出頻率進(jìn)行精密設(shè)定,還可以如圖 2 所示,在鎖相環(huán)頻率合成器的輸入前及輸出后設(shè)置分頻電路。

為了提高鎖相環(huán)頻率合成器的頻率設(shè)定分辨率,通常把分頻器直接連接在石英晶體振蕩單元之后。但是,若為了提高頻率設(shè)定分辨率而取較大的分頻數(shù),則將造成用于比較相位的頻率變小,引發(fā)鎖相環(huán)響應(yīng)慢、環(huán)路增益下降的情況,并對輸出波形的抖動和相位噪音特性造成不良影響。為解決上述問題,也可使用小數(shù)分頻鎖相環(huán)。

【3】整數(shù)分頻鎖相環(huán)與小數(shù)分頻鎖相環(huán)的特征

鎖相環(huán)電路可分為整數(shù)分頻和小數(shù)分頻的兩大類。雙方均利用波源輸出高頻,在此說明大特征。

整數(shù)分頻鎖相環(huán)可以名副其實(shí)地產(chǎn)生輸入頻率整數(shù)倍的輸出頻率。例如,希望從 1MHz 的波源獲得 100MHz 的輸出時(shí),分頻器的計(jì)數(shù)器設(shè)定值為 100。

與此相對,小數(shù)分頻鎖相環(huán)可以產(chǎn)生輸入頻率小數(shù)倍的輸出頻率。這事實(shí)上意味著可以任意選擇頻率,即能夠獲得微小的頻率設(shè)定分辨率。它可以獲得微小的頻率分辨率,發(fā)揮這個(gè)特征可以對初始頻率公差進(jìn)行精密控制。

然而,與上述優(yōu)點(diǎn)相反,小數(shù)分頻的電路設(shè)計(jì)復(fù)雜,集成電路面積也比整數(shù)分頻大,因此容易產(chǎn)生特有的失真,致使小數(shù)分頻的相位噪音與整數(shù)分頻相比較差。隨著近幾年技術(shù)的發(fā)展,小數(shù)分頻鎖相環(huán)的缺點(diǎn)被不斷改進(jìn),失真逐漸減少。

【4】愛普生的產(chǎn)品陣容與特征

以上說明了為獲得高頻輸出而采用的鎖相環(huán)電路。鎖相環(huán)電路的最大特征是能夠獲得任意的頻率,即可以獲得包括高頻在內(nèi)的所需頻率。

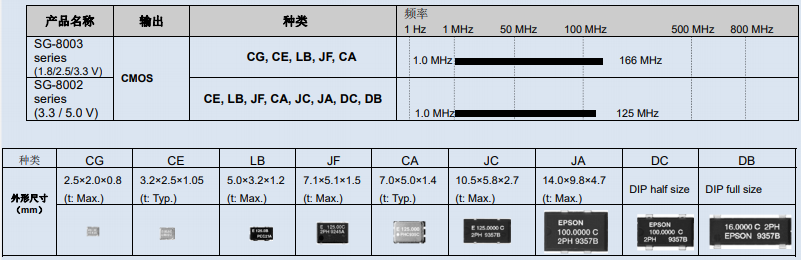

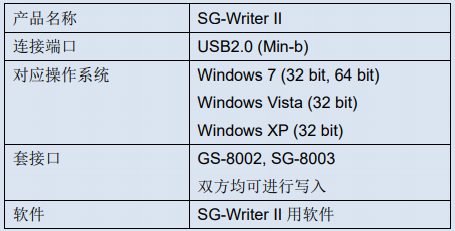

愛普生 SG-8000 系列采用先前介紹的整數(shù)分頻鎖相環(huán)電路,為用戶準(zhǔn)備了尺寸及形狀極為豐富的產(chǎn)品陣容(表 1)。我們還為用戶準(zhǔn)備了 SG-8000 系列的編程工具――ROM Writer(SG-Writer II),用于寫入頻率(表 2)。

SG-8000系列使用AT型石英晶體單元。AT型石英晶體單元具有呈三次曲線的溫度特性,能夠保持一定的溫度穩(wěn)定度。因此,SG-8000系列在常溫條件下不需要溫度補(bǔ)償電路就能夠?qū)崿F(xiàn)針對溫度變化而相對穩(wěn)定的溫度特性,即不出現(xiàn)頻率間斷性跳動的情況。溫度特性呈線形的全硅MEMS等振蕩器需要使用溫度補(bǔ)償電路使溫度保持穩(wěn)定,導(dǎo)致有可能出現(xiàn)頻率的間斷性跳動。

這些石英晶體所具有的高精度特性以及通過鎖相環(huán)電路技術(shù)而實(shí)現(xiàn)的可獲得任意頻率的方便性,希望能夠得到多方惠顧。

最后說明上述獲得高頻輸出的倍頻和鎖相環(huán)電路的注意之處。

倍頻電路:應(yīng)注意分諧波混入電路以及因 n/2 以下成份而引起的抖動。

鎖相環(huán)電路:應(yīng)注意環(huán)路頻帶,在鎖相環(huán)電路之后串聯(lián)其它鎖相環(huán)電路時(shí)應(yīng)注意抖動增幅和跟蹤。

表 1:程控石英晶體振蕩器的產(chǎn)品陣容

表 2:SG-8000 系列用編程工具

-

pll

+關(guān)注

關(guān)注

6文章

767瀏覽量

134860 -

鎖相環(huán)電路

+關(guān)注

關(guān)注

0文章

15瀏覽量

11965 -

高頻輸出

+關(guān)注

關(guān)注

0文章

6瀏覽量

929

發(fā)布評論請先 登錄

相關(guān)推薦

PLL設(shè)計(jì)的簡易方法介紹

請問我能從PLL,DCM或級聯(lián)PLL DCM獲得多大的輸出頻率限制?

使用pll的時(shí)鐘輸出的正確方法是什么?

怎么使用PLL來獲得更高的電平?

PLL知識

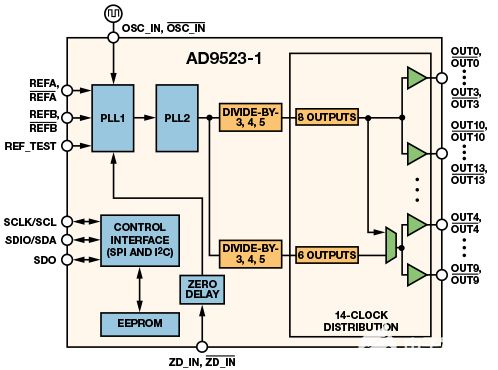

Mouser備貨Analog Devices公司最高頻率PLL

鎖相環(huán)PLL的設(shè)計(jì)方法和調(diào)試說明

具 PLL 的 5 輸出超低抖動時(shí)鐘分配器提供獨(dú)特的多芯片輸出同步方法

雙環(huán)路時(shí)鐘發(fā)生器清除抖動,提供多個(gè)高頻輸出

實(shí)現(xiàn)高頻輸出的方法

獲得高頻輸出的方法AT技術(shù)

獲得高頻輸出的方法PLL技術(shù)

獲得高頻輸出的方法PLL技術(shù)

評論