時(shí)鐘抖動(dòng)和相位噪聲是數(shù)字系統(tǒng)和通信系統(tǒng)中兩個(gè)至關(guān)重要的概念,它們之間存在著緊密而復(fù)雜的關(guān)系。以下是對(duì)時(shí)鐘抖動(dòng)和相位噪聲關(guān)系的詳細(xì)探討,旨在全面解析兩者之間的相互作用和影響。

一、定義與基本概念

時(shí)鐘抖動(dòng)(Clock Jitter) :

時(shí)鐘抖動(dòng)是指時(shí)鐘信號(hào)在時(shí)間上的偏離,表現(xiàn)為時(shí)鐘信號(hào)邊緣(如上升沿或下降沿)與其理想位置之間的隨機(jī)或周期性變化。時(shí)鐘抖動(dòng)可以是周期性的,也可以是隨機(jī)性的,它可能由溫度變化、電磁干擾、電源噪聲、器件不穩(wěn)定性等多種因素引起。時(shí)鐘抖動(dòng)會(huì)直接影響數(shù)據(jù)傳輸?shù)臏?zhǔn)確性和時(shí)序性能,進(jìn)而可能導(dǎo)致系統(tǒng)性能下降。

相位噪聲(Phase Noise) :

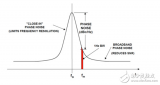

相位噪聲是指信號(hào)頻率中相位差的隨機(jī)變化引起的頻率不穩(wěn)定性。它描述了信號(hào)相位隨時(shí)間的變化情況,是信號(hào)質(zhì)量的一個(gè)重要指標(biāo)。相位噪聲一般通過頻譜分析儀來測(cè)量,表現(xiàn)為信號(hào)頻譜中的噪聲邊帶或旁瓣。相位噪聲的產(chǎn)生原因多樣,包括器件非線性、溫度變化、時(shí)鐘漂移等。

二、時(shí)鐘抖動(dòng)與相位噪聲的關(guān)系

1. 相互影響

時(shí)鐘抖動(dòng)導(dǎo)致相位噪聲 :

時(shí)鐘抖動(dòng)會(huì)直接影響到時(shí)鐘信號(hào)的相位穩(wěn)定性。當(dāng)時(shí)鐘信號(hào)發(fā)生抖動(dòng)時(shí),其相位會(huì)隨之發(fā)生隨機(jī)或周期性的變化,這種相位的不穩(wěn)定性正是相位噪聲的體現(xiàn)。因此,時(shí)鐘抖動(dòng)是相位噪聲的一個(gè)重要來源。隨著時(shí)鐘抖動(dòng)的增大,相位噪聲也會(huì)相應(yīng)增加,從而影響信號(hào)的質(zhì)量和系統(tǒng)的性能。

相位噪聲反映時(shí)鐘抖動(dòng) :

相位噪聲作為信號(hào)頻率穩(wěn)定性的度量,也間接反映了時(shí)鐘信號(hào)的抖動(dòng)情況。相位噪聲越大,說明信號(hào)的相位穩(wěn)定性越差,這往往與較大的時(shí)鐘抖動(dòng)相對(duì)應(yīng)。因此,通過測(cè)量和分析相位噪聲,可以間接評(píng)估時(shí)鐘信號(hào)的抖動(dòng)水平。

2. 共同作用對(duì)系統(tǒng)性能的影響

時(shí)鐘抖動(dòng)和相位噪聲共同作用于系統(tǒng),對(duì)數(shù)據(jù)傳輸、信號(hào)處理和系統(tǒng)性能產(chǎn)生深遠(yuǎn)影響。具體來說:

- 數(shù)據(jù)傳輸錯(cuò)誤 :時(shí)鐘抖動(dòng)和相位噪聲會(huì)導(dǎo)致數(shù)據(jù)傳輸過程中的時(shí)序問題,如數(shù)據(jù)采樣點(diǎn)偏離理想位置,從而增加數(shù)據(jù)傳輸錯(cuò)誤的風(fēng)險(xiǎn)。

- 信號(hào)質(zhì)量下降 :相位噪聲會(huì)引起信號(hào)頻譜的擴(kuò)展和不規(guī)則變化,導(dǎo)致信號(hào)質(zhì)量下降。這會(huì)影響信號(hào)的傳輸性能和接收機(jī)的解調(diào)能力。

- 系統(tǒng)性能下降 :時(shí)鐘抖動(dòng)和相位噪聲的增大會(huì)降低系統(tǒng)的整體性能,如增加誤碼率、降低信號(hào)解調(diào)精度等。在需要高精度同步和時(shí)序控制的系統(tǒng)中,這種影響尤為顯著。

三、減少時(shí)鐘抖動(dòng)和相位噪聲的方法

為了降低時(shí)鐘抖動(dòng)和相位噪聲對(duì)系統(tǒng)性能的影響,可以采取以下多種方法:

1. 優(yōu)化時(shí)鐘源

- 選擇低抖動(dòng)晶振 :使用具有低抖動(dòng)特性的晶振作為時(shí)鐘源,如TCXO(溫補(bǔ)晶體振蕩器)、VCXO(壓控晶體振蕩器)等。

- 穩(wěn)定電源供應(yīng) :采用低噪聲的電源設(shè)計(jì),并加強(qiáng)電源的濾波和去耦,以減少電源噪聲對(duì)時(shí)鐘信號(hào)的影響。

2. 優(yōu)化時(shí)鐘分布網(wǎng)絡(luò)

- 合理布局布線 :在FPGA或ASIC設(shè)計(jì)中,合理布局時(shí)鐘信號(hào)線和其他信號(hào)線,避免長(zhǎng)距離傳輸和信號(hào)間的串?dāng)_。

- 使用時(shí)鐘緩沖器 :在時(shí)鐘信號(hào)傳輸路徑中適當(dāng)放置時(shí)鐘緩沖器,以減小信號(hào)衰減和傳輸延遲。

3. 應(yīng)用時(shí)鐘同步技術(shù)

- 使用PLL/DLL :利用鎖相環(huán)(PLL)或延遲鎖定環(huán)(DLL)等同步技術(shù),對(duì)時(shí)鐘信號(hào)進(jìn)行精確同步和相位調(diào)整,以減小抖動(dòng)和相位噪聲。

- 時(shí)鐘恢復(fù)技術(shù) :在接收端采用時(shí)鐘恢復(fù)技術(shù),從接收信號(hào)中提取穩(wěn)定的時(shí)鐘信號(hào),以提高系統(tǒng)的同步性能和抗抖動(dòng)能力。

4. 加強(qiáng)電磁屏蔽與隔離

- 電磁屏蔽 :使用電磁屏蔽材料包裹關(guān)鍵信號(hào)線和組件,以減少外部電磁干擾對(duì)時(shí)鐘信號(hào)的影響。

- 信號(hào)隔離 :采用隔離技術(shù)將時(shí)鐘信號(hào)與其他敏感信號(hào)隔離開來,降低信號(hào)間的相互干擾。

5. 軟件補(bǔ)償與校準(zhǔn)

- 算法補(bǔ)償 :在軟件層面采用算法對(duì)時(shí)鐘信號(hào)的偏差進(jìn)行預(yù)測(cè)和補(bǔ)償,以提高系統(tǒng)的時(shí)序性能。

- 校準(zhǔn)機(jī)制 :建立定期校準(zhǔn)機(jī)制對(duì)時(shí)鐘信號(hào)進(jìn)行校準(zhǔn)和調(diào)整,以確保其穩(wěn)定性和準(zhǔn)確性。

四、總結(jié)與展望

時(shí)鐘抖動(dòng)和相位噪聲是數(shù)字系統(tǒng)和通信系統(tǒng)中兩個(gè)不可忽視的問題。它們之間存在著緊密的關(guān)系并共同作用于系統(tǒng)性能。通過深入理解和分析時(shí)鐘抖動(dòng)和相位噪聲的產(chǎn)生原因和相互關(guān)系以及它們對(duì)系統(tǒng)性能的影響,我們可以采取有效的措施來降低其影響并提高系統(tǒng)的整體性能。未來隨著技術(shù)的不斷發(fā)展和創(chuàng)新,相信會(huì)有更多先進(jìn)的方法和技術(shù)被應(yīng)用于時(shí)鐘抖動(dòng)和相位噪聲的抑制和消除中,為數(shù)字系統(tǒng)和通信系統(tǒng)的發(fā)展提供更有力的支持。

-

時(shí)鐘抖動(dòng)

+關(guān)注

關(guān)注

1文章

62瀏覽量

15917 -

相位噪聲

+關(guān)注

關(guān)注

2文章

180瀏覽量

22835 -

時(shí)鐘信號(hào)

+關(guān)注

關(guān)注

4文章

445瀏覽量

28509

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

怎么將相位噪聲轉(zhuǎn)換為抖動(dòng)?

低相位噪聲&抖動(dòng)

測(cè)量較低時(shí)鐘頻率的相位噪聲和相位抖動(dòng)

時(shí)鐘抖動(dòng)(CLK)和相位噪聲之間的轉(zhuǎn)換

振蕩器相位噪聲到時(shí)間抖動(dòng)的轉(zhuǎn)換

時(shí)鐘抖動(dòng)性能和相位噪聲測(cè)量

相位噪聲是與哪種類型的抖動(dòng)相對(duì)應(yīng),彼此之間又有著怎樣的數(shù)學(xué)關(guān)系

相位噪聲處理:時(shí)鐘抖動(dòng)或結(jié)束時(shí)鐘抖動(dòng)的最佳方法是什么?資料下載

相位噪聲與時(shí)間抖動(dòng)概述及其關(guān)系

時(shí)鐘抖動(dòng)使隨機(jī)抖動(dòng)和相位噪聲不再神秘

相位噪聲與時(shí)間抖動(dòng)有著什么關(guān)系?

相噪是與哪種類型的抖動(dòng)相對(duì)應(yīng)?如何理解相位噪聲與時(shí)間抖動(dòng)的關(guān)系?

相位噪聲到抖動(dòng)的轉(zhuǎn)換(上)

時(shí)鐘抖動(dòng)與相位噪聲的關(guān)系

時(shí)鐘抖動(dòng)與相位噪聲的關(guān)系

評(píng)論