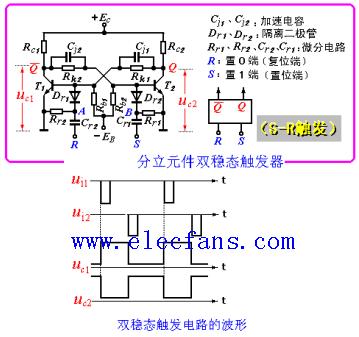

雙穩態觸發器(Bistable Trigger)是一種具有兩個穩定狀態的數字電路,常用于存儲一位二進制信息。它在數字電路設計中具有重要應用,如存儲器、計數器、寄存器等。

一、雙穩態觸發器的類型

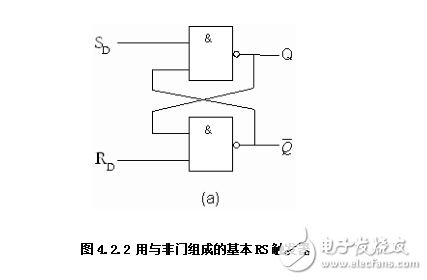

基本RS觸發器是一種最簡單的雙穩態觸發器,由兩個交叉耦合的反相器組成。它有兩個輸入端:置位(Set)端和復位(Reset)端。當置位端為高電平時,觸發器輸出為高電平;當復位端為高電平時,觸發器輸出為低電平。基本RS觸發器存在競爭冒險問題,因此需要改進。

- 鐘控RS觸發器(Clocked RS Flip-Flop)

鐘控RS觸發器在基本RS觸發器的基礎上增加了一個時鐘輸入端,通過時鐘信號控制觸發器的狀態轉換。當置位端和復位端同時為高電平時,觸發器保持當前狀態不變。鐘控RS觸發器可以有效避免競爭冒險問題。

- D觸發器(D Flip-Flop)

D觸發器是一種具有數據輸入端的雙穩態觸發器,其輸出與數據輸入端相同。D觸發器在時鐘信號的上升沿或下降沿觸發,將數據輸入端的電平存儲到觸發器中。D觸發器廣泛應用于數據傳輸和同步。

- JK觸發器(JK Flip-Flop)

JK觸發器是一種具有兩個輸入端的雙穩態觸發器,分別稱為J端和K端。JK觸發器具有多種工作模式,如置位、復位、保持和翻轉。JK觸發器可以通過組合實現其他類型的觸發器,如T觸發器和T'觸發器。

- T觸發器(T Flip-Flop)

T觸發器是一種具有一個輸入端的雙穩態觸發器,其輸出在輸入端為高電平時翻轉。T觸發器常用于實現移位寄存器和計數器。

- 同步RS觸發器(Synchronous RS Flip-Flop)

同步RS觸發器是一種具有同步特性的雙穩態觸發器,其狀態轉換由時鐘信號和置位端、復位端共同控制。同步RS觸發器可以有效避免亞穩態問題,提高電路的穩定性。

- 邊沿觸發器(Edge-Triggered Flip-Flop)

邊沿觸發器是一種在時鐘信號的上升沿或下降沿觸發的雙穩態觸發器。邊沿觸發器具有較高的抗干擾能力,常用于高速數字電路設計。

- 負邊沿觸發器(Negative-Edge Triggered Flip-Flop)

負邊沿觸發器是一種在時鐘信號的下降沿觸發的雙穩態觸發器。負邊沿觸發器在某些特定應用中具有優勢,如實現負邊沿觸發的計數器。

- 正邊沿觸發器(Positive-Edge Triggered Flip-Flop)

正邊沿觸發器是一種在時鐘信號的上升沿觸發的雙穩態觸發器。正邊沿觸發器在大多數數字電路設計中得到廣泛應用。

- 雙穩態觸發器的變體

除了上述基本類型外,雙穩態觸發器還有許多變體,如帶使能端的觸發器、帶清零端的觸發器、帶預置端的觸發器等。這些變體在特定應用中具有優勢,可以根據實際需求進行選擇。

二、雙穩態觸發器的工作原理

雙穩態觸發器的工作原理主要基于邏輯門和反饋回路。以下是幾種常見觸發器的工作原理:

- 基本RS觸發器

基本RS觸發器由兩個交叉耦合的反相器組成,其輸出端分別連接到輸入端。當置位端為高電平時,觸發器輸出為高電平;當復位端為高電平時,觸發器輸出為低電平。基本RS觸發器存在競爭冒險問題,需要改進。

- 鐘控RS觸發器

鐘控RS觸發器在基本RS觸發器的基礎上增加了一個時鐘輸入端。當置位端和復位端同時為高電平時,觸發器保持當前狀態不變。時鐘信號控制觸發器的狀態轉換,有效避免競爭冒險問題。

- D觸發器

D觸發器具有數據輸入端,其輸出與數據輸入端相同。在時鐘信號的上升沿或下降沿觸發時,D觸發器將數據輸入端的電平存儲到觸發器中。

-

存儲

+關注

關注

13文章

4266瀏覽量

85686 -

二進制

+關注

關注

2文章

794瀏覽量

41602 -

數字電路

+關注

關注

193文章

1601瀏覽量

80511

發布評論請先 登錄

相關推薦

雙穩態觸發器可分為什么類型

雙穩態觸發器可分為什么類型

評論