來源:C Lighting

線邊緣粗糙度(LER)

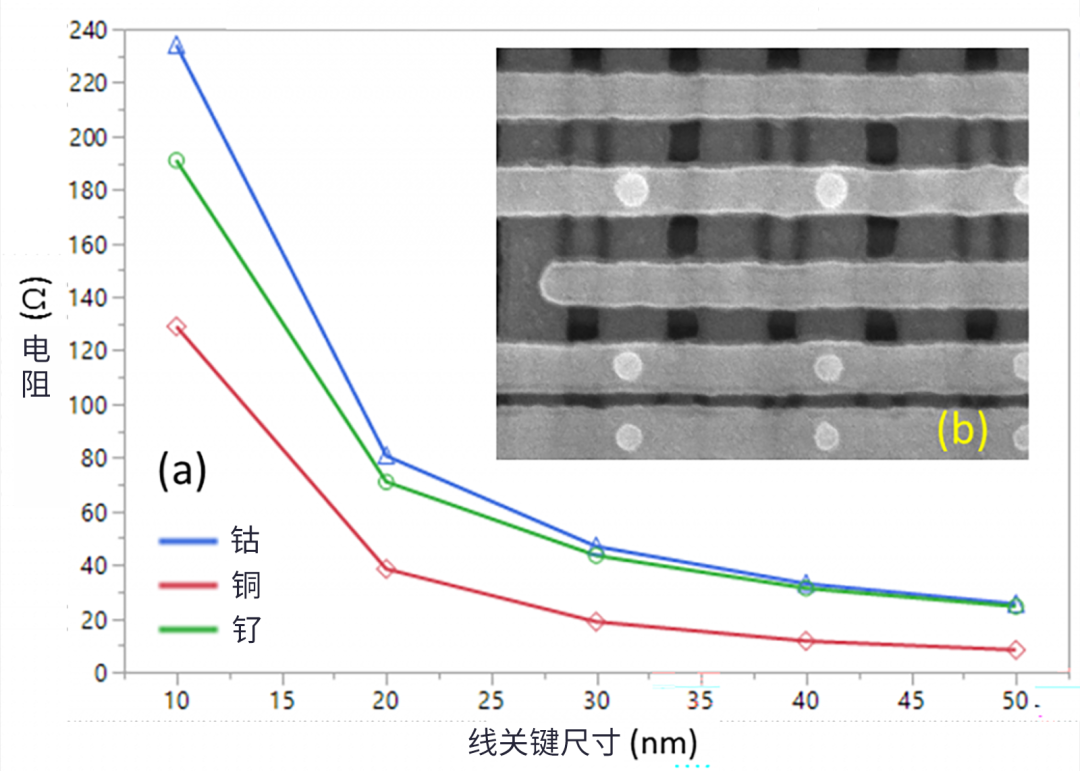

線邊緣粗糙度(LER)指的是柵極圖案邊緣的隨機變化,即印刷圖案邊緣的粗糙度。當最小特征尺寸減小到幾十納米以下時,LER對MOSFET性能的影響就無法忽視了。LER會在溝道長度方向上產生一些幸運(lucky)通道(即局部短溝道),從而導致器件之間的不匹配。例如,在Intel的65納米器件中,當LER的標準偏差三倍值(3σ)大于標稱柵極關鍵尺寸(critical dimension)的10%時,實驗觀察到了導通驅動電流(on-state drive current)下降了2%。

由于LER引起的變異與短溝道效應(SCE:short channel effect)高度相關,因此具有較強短溝道效應抵抗力的器件結構在給定的LER輪廓下受到的性能變異影響較小。例如,由FinFET和三柵MOSFET組成的六晶體管(6-T)靜態隨機存取存儲器(SRAM)單元,或者超薄體器件,如全耗盡硅絕緣體MOSFET(FDSOI MOSFET),由于它們改進了柵極到溝道的電容耦合(與傳統平面體MOSFET相比),因此對LER引起的工藝變異有更好的免疫力。

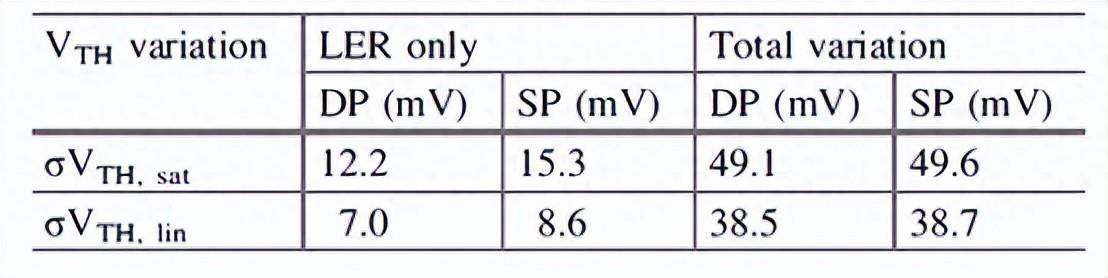

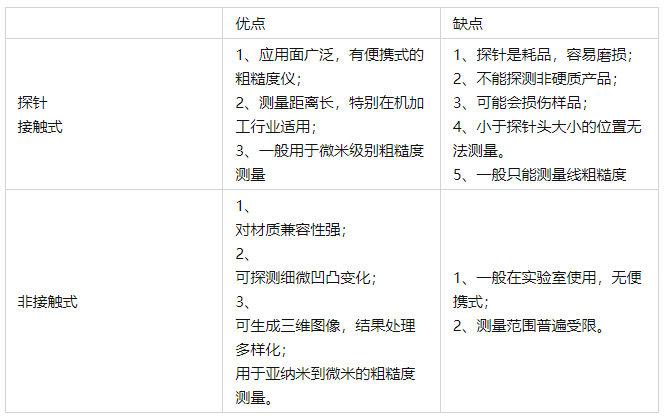

此外,如表1所示,通過利用雙重圖案技術(DP),28納米三柵體(tri-gate)MOSFET中的LER引起的閾值電壓(VTH)變異可以減少大約20%。值得注意的是,盡管LER引起的VTH變異減少了,總的隨機變異量只略有減少。這表明在三柵體MOSFET中,隨機摻雜波動(RDF:random dopant fluctuation)或工作函數變異(WFV:work function variation)等其他隨機變異源要比LER更為顯著。然而,盡管在 FinFET 器件中,由LER引起的VTH變化有所減小,但fin邊緣粗糙度(即沿溝道長度方向的 LER)已與 WFV 一起成為最關鍵的隨機變化源之一。

表1:三柵極 MOSFET 中 LER 引起的 VTH 變化(取決于光刻技術)

LER的物理來源

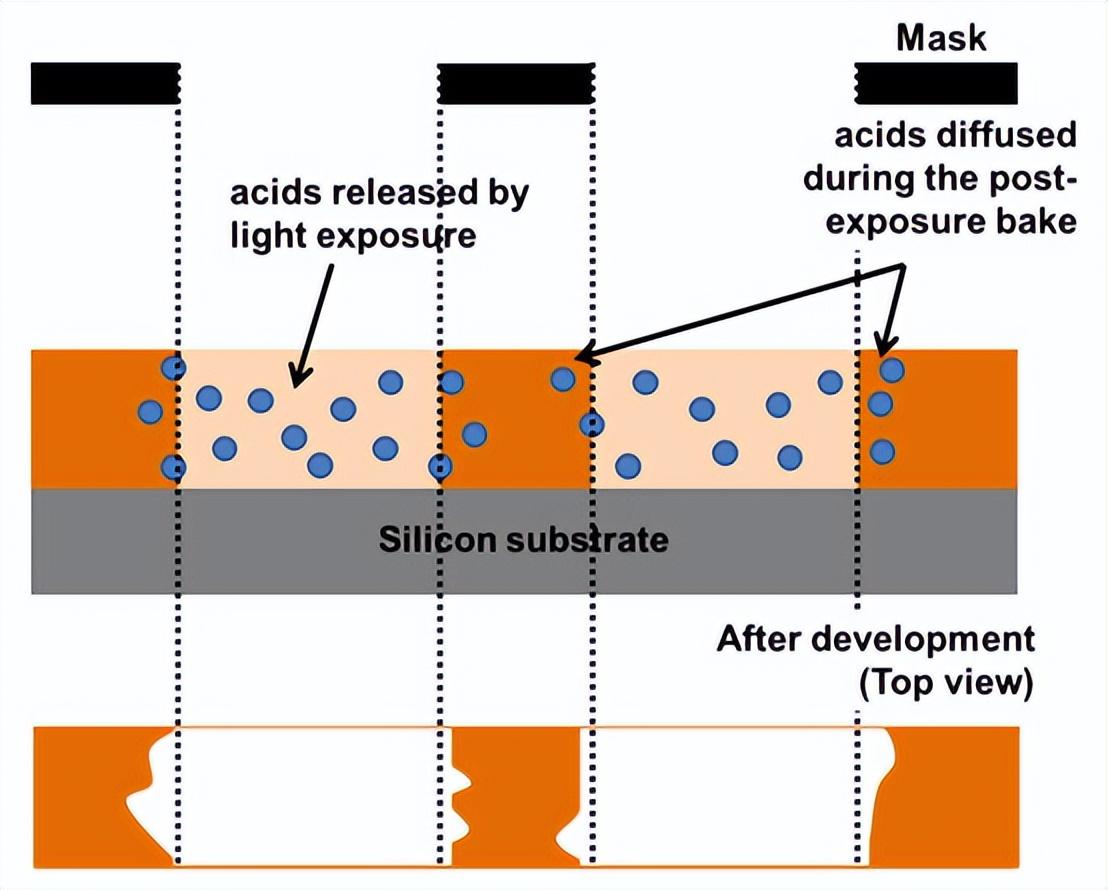

在光刻步驟中,掩膜上繪制的圖案會轉移到抗蝕層上,因為抗蝕層的溶解度會因抗蝕層是否受光照射而變化。為了提高對光的敏感度,通常會使用化學放大法。在這一過程中,化學放大的抗蝕劑暴露在光下以產生酸。在曝光后的烘烤步驟中,這些酸會催化聚合物的去保護作用。抗蝕劑的去保護部分很容易被顯影劑溶解,從而產生抗蝕圖案。最終的 LER 曲線包含了前面每個加工步驟的所有累積變化。

2.1 掩模圖案的LER

在考慮LER(線邊緣粗糙度)時,掩模圖案本身的任何粗糙度似乎都是LER的根本原因。如果掩模圖案本身就存在LER,并且光刻技術能夠無失真地轉移這種LER,那么投射到PR(Photo Resist)層上的圖案就會具有與掩模圖案完全相同的LER輪廓。實際上,掩模邊緣的波動是不可避免的,掩模圖案本身就有一定的粗糙度。然而,這種粗糙度相對于原始圖案的尺寸來說足夠小,以至于可以忽略不計。從技術上來講,在當前193納米光刻技術下,幾乎不可能轉移微小的圖案(即掩模圖案的粗糙度)。因此,掩模圖案固有的LER不會對PR圖案的LER造成貢獻。

盡管如此,掩模圖案的粗糙度仍然是一個值得關注的因素,尤其是在更高精度的需求下。隨著技術的進步,更先進的光刻技術可能會使掩模圖案的微小粗糙度成為問題。例如,在EUV光刻中,掩模圖案的精確度變得更加關鍵,因為EUV光刻技術可以實現更精細的特征尺寸。在這些情況下,掩模圖案的粗糙度可能會對最終的光阻圖案產生影響。

總的來說,雖然掩模圖案的粗糙度通常不足以直接導致光阻圖案的LER,但在更先進的制造工藝中,它可能成為一個需要注意的問題。制造商通常會采取措施來最小化掩模圖案的粗糙度,并確保光刻過程中其他因素得到控制,以減少LER的影響。

2.2 曝光劑量的變化

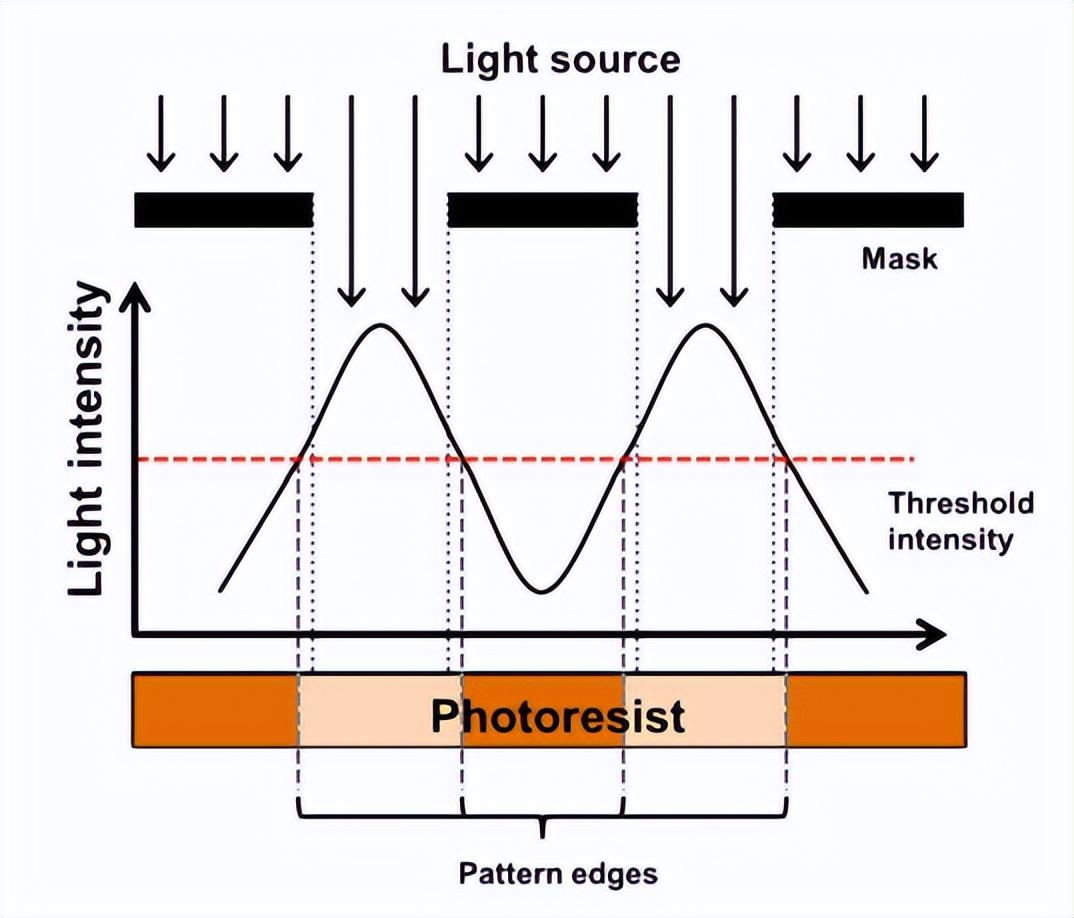

光刻技術所能達到的分辨率主要取決于所使用的投影透鏡的尺寸,因為投影透鏡的孔徑(或直徑)決定了衍射階次。理論上,需要一個無限大的透鏡來收集所有的衍射階次;然而,實際上的透鏡具有有限的尺寸。這一現實往往限制了光刻技術的分辨率。其結果是,到達光阻表面的曝光光線強度并不是階躍函數的形狀,而是sinc函數的形狀(即,曝光光線的強度具有一定的梯度)。

圖1:光刻步驟示意圖。展示了光線強度對LER的影響,由于光強度的梯度,Pattern邊緣與Mask邊緣并不完全匹配。

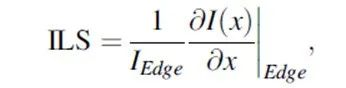

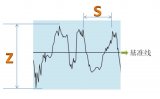

我們假設,如果曝光光線的強度等于或高于閾值強度,則光阻會被酸激活,從而可以容易地溶解出去。光阻圖案的邊緣是曝光光線強度等于閾值劑量的點。為了定量理解特征邊緣處的空中圖像對比度,引入了圖像對數斜率(Image Log-Slope, ILS)的概念:

其中

是邊緣處的光強和邊緣處的光強斜率。ILS描述了曝光光線強度從完全暴露到未暴露區域過渡的陡峭程度。較高的ILS意味著邊緣更加清晰,從而有助于減少LER。

在制造過程中,隨著光刻工藝中每個步驟的完成,每個步驟中的曝光光強度往往會因激光輸出功率的變化、光學系統的振動、晶片載物臺的微小上下移動和/或光量化導致的總劑量波動等不良影響而波動。由于光刻膠圖案的邊緣是由光強決定的,因此曝光光強的波動是 LER 的根本原因之一。如果圖案邊緣的光強斜率較陡,邊緣的波動就會減小。因此,要減輕 LER,明暗對比度必須很大(即光強梯度陡峭)。

曝光劑量的變化會對光刻結果產生顯著影響。例如,即使是很小的劑量變化也可能導致光阻圖案的邊緣移動,進而影響LER。劑量控制的非準確性可能是由于光源強度的變化、透鏡系統的不完美、掩模與光阻兩者之間的距離變化等多種因素造成的。

劑量的變化可以通過多種方式來量化和控制。一種常用的方法是通過劑量掃描實驗來確定最佳曝光劑量,以獲得所需的圖案尺寸和形狀。此外,還可以使用劑量反饋控制系統來實時調整曝光劑量,以減少因劑量變化引起的LER。值得注意的是,即使圖像對比度持續增加,LER 也會在5 nm處達到飽和。超過這一點,任何殘余的LER都來自抗蝕劑固有的材料粗糙度。

總之,曝光劑量的變化是影響光刻技術中LER的重要因素之一。通過優化曝光條件、改善透鏡設計以及采用先進的劑量控制技術,可以有效地減少這種影響,從而提高光刻圖案的質量。

2.3 化學放大(CA:Chemically Amplified)光阻中的LER生成

在CMOS制造過程中,化學放大被用來提高光阻的靈敏度。化學放大光阻包含圖3所示的光酸化發生器(photoacid generator)。當化學放大光阻薄膜中的光酸化生成器吸收來自光的能量時,它們分解成酸陽離子和其他陰離子。這一分解過程被稱為去保護反應。在曝光后的烘烤步驟中,生成的酸在光阻薄膜內擴散,并幫助催化去保護反應。酸是不會被消耗掉,而是在去保護反應中持續存在,因此能夠反復催化這些反應。由于酸可以改變聚合物的溶解性,去保護的聚合物區域可以選擇性地被顯影劑去除,從而使掩模上的圖案能夠轉移到光阻薄膜上。

然而,由于酸在光阻薄膜內隨機擴散,這會導致LER的產生。在曝光后的烘烤步驟中,(i)烘烤溫度,(ii)去保護反應的局部程度,以及(iii)反應副產品的濃度都會影響酸的擴散系數。Acid molecule的擴散距離通常是幾十納米。但是,很難完全控制擴散速率,因為在烘烤過程中溫度、局部反應程度和副產品濃度都不是恒定的。因此,有可能某些酸會擴散到目標邊緣之外。如果未曝光區域被這些酸充分的去保護,它們將被顯影劑溶解,從而導致LER中的higher frequency成分增加。

圖2:在化學放大的抗蝕劑中,LER是在曝光后的烘烤步驟中由于酸擴散而形成的。

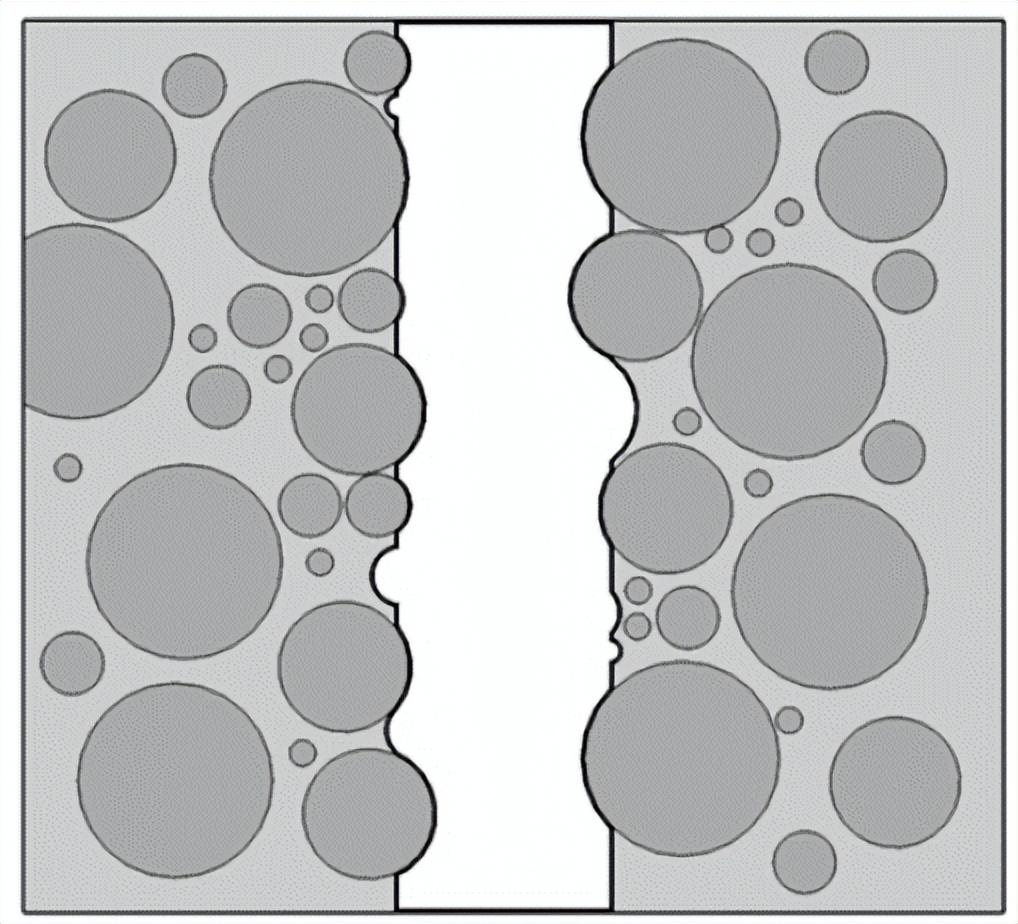

2.4 光阻的固有粗糙度

即使排除了其他LER(線邊粗糙度)的來源,光阻本身的非均勻性也會沿側邊造成LER。例如,即使曝光光強度是沒有變化的,光阻的光子吸收也會隨物理位置的不同而有所變化。假定光子吸收均勻,光刻膠聚合物鏈中的隨機溶解和不同尺寸會在圖案邊緣產生粗糙(見圖 2.4)。此外,沿著曝光圖案的邊緣,一些聚合物分子會涂抹到顯影液中,但仍固定在抗蝕劑薄膜的其他部分。在去離子水沖洗過程中,這些部分溶解的聚合物鏈將會重新沉積在抗蝕劑上,并重新確定圖案的邊緣。

固有粗糙度的來源:

光子吸收的非均勻性:即使光強均勻,光阻的內部的光子吸收也會因位置不同而有所差異,這會導致局部曝光量的變化。

聚合物鏈的尺寸差異:光阻聚合物鏈的長度和形狀的不一致性也會導致溶解性的差異,進而影響圖案邊緣的平滑度。

溶解過程的隨機性:在顯影過程中,聚合物鏈的溶解是隨機的,這會導致邊緣粗糙度。

聚合物分子的溶脹和再沉積。溶脹:在顯影過程中,聚合物分子可能會從曝光區域的部分溶解并溶入顯影劑中。再沉積:在去離子水沖洗步驟中,這些部分溶解的聚合物鏈將可能會重新沉積在光阻表面,這會影響圖案邊緣的形狀,增加粗糙度。

圖3:光刻膠中不同尺寸的聚合物造成的LER

雙重圖案化對LER的影響

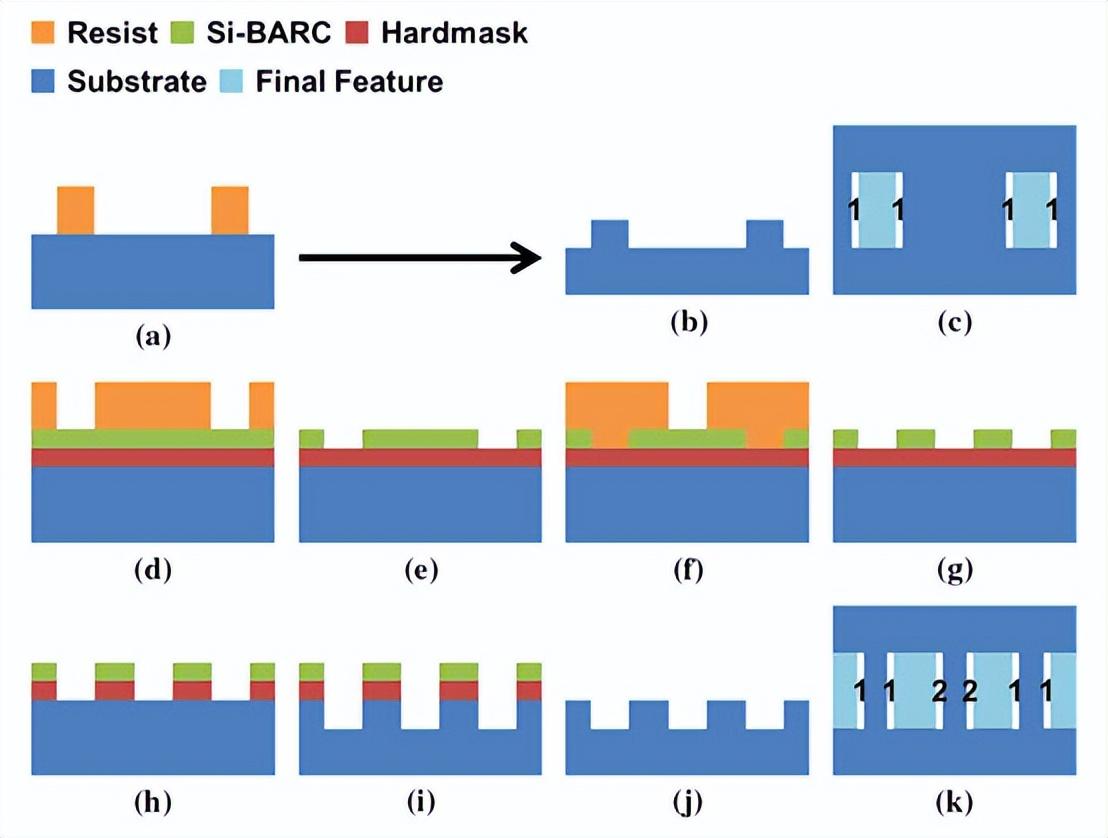

3.1 雙重圖案化與雙重蝕刻

為了提高光阻圖案的分辨率而不更換光源(例如,從193納米到極紫外光刻 EUV),在小于32納米節點的光刻過程中添加了雙重圖案化技術。雙重圖案化技術已在22/20納米技術及以上廣泛采用。請注意,雙重圖案化和雙重蝕刻(2P2E:double patterning and double etching)是雙重圖案化技術的一個例子。2P2E是一種用于提高分辨率的技術,通過兩次圖案化和兩次蝕刻的過程來實現更細的圖案。這種技術能夠使用相同的光源、光阻和節距尺寸實現更精細的圖案。

在雙重圖案化技術中,首先將硅基底抗反射層(Si-BARC)和旋涂氧化層(SOC)涂覆在襯底上。這些層在第一次和第二次光刻步驟中保留了原始圖案,并在第二次蝕刻步驟中作為硬掩模發揮關鍵作用。在Si-BARC上旋涂一層光阻,然后通過第一次光刻步驟投射第一個圖案(圖4d)。通過隨后的第一次蝕刻步驟,光阻上的圖案轉移到Si-BARC上,而在傳統工藝中則是蝕刻底層襯底(圖4e, b)。接下來,為了第二次光刻步驟,另一層進行光阻的旋涂以填充Si-BARC上的第一個圖案,然后執行第二次光刻步驟(圖4f)。較薄的Si-BARC膜可對與在版圖上涂覆第二層光刻膠堆棧相關的涂層均勻性問題產生最小影響。第二次蝕刻步驟用于將光阻上的圖案轉移到Si-BARC層上(圖4g)。最后,圖案從Si-BARC轉移到SOC,再從SOC轉移到襯底(圖4h-j)。因此,雙重圖案化和雙重蝕刻技術能夠在使用相同光源、光阻、節距大小和顯影方法的情況下實現比傳統光刻更精細的圖案。

圖4:a、b為1P1E技術和d-j為2P2E 技術的圖案化工藝順序。1P1E和2P2E的最終特征的頂視圖分別顯示在(c)和(k)中。請注意,每個線邊緣都用“1”(“2”) 表示,以表明線邊緣受到第一 (第二) 圖案化步驟的影響。

由于線邊粗糙度輪廓通過多次蝕刻過程傳遞,襯底上的LER輪廓與光阻、Si-BARC和SOC上的原始LER輪廓不同。隨著蝕刻過程的完成,圖案的邊緣趨于平滑。通過統計和實驗數據已經確認,基于雙重圖案化和雙重蝕刻技術的LER輪廓的相關長度大于傳統的LER輪廓的相關長度。因此,多次蝕刻過程會導致具有較低空間頻率和平坦峰谷的更平滑線邊,從而減少LER ,使線邊更加平滑。此外,額外的熱處理,比如在第一次和第二次光刻之間的后烘烤和曝光后烘烤,會進一步增加LER輪廓的相關長度,平滑線邊輪廓。

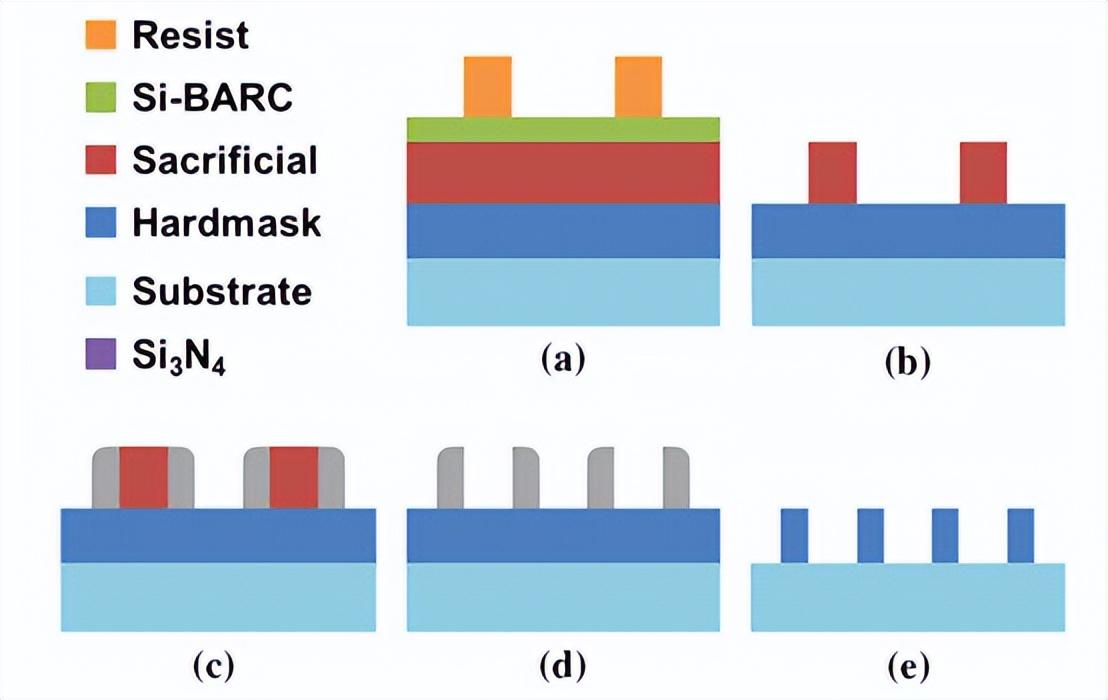

3.2 自對準雙重圖案化

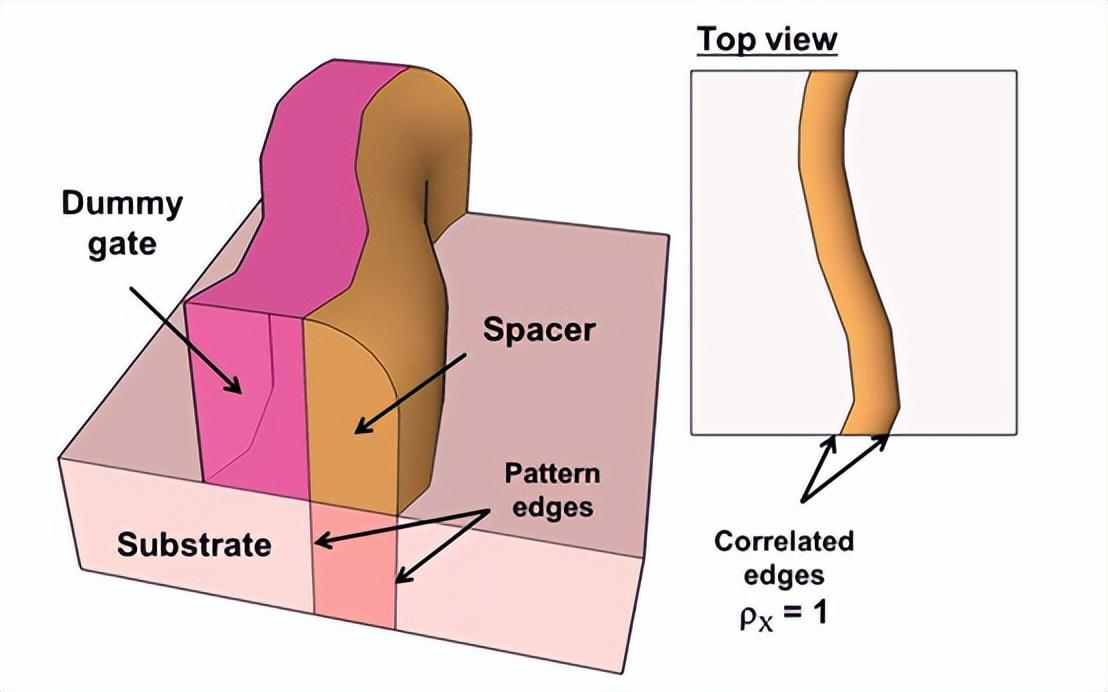

雖然使用雙重圖案化和雙重蝕刻技術需要兩次單獨的光刻步驟以便使光阻圖案的分辨率加倍,但有一種完全不同的方法稱為自對準雙重圖案化,它只需要一次曝光。自對準雙重圖案化可以通過薄膜沉積、蝕刻和化學機械拋光(CMP)而不需額外的光刻步驟使光阻圖案的分辨率加倍。自對準雙重圖案化的工藝流程參看圖5。通過光刻和蝕刻步驟,按照特定的節距將涂覆的光阻圖形化(注意,最終圖案的節距將會減半)。接下來,光阻上的圖案通過等離子蝕刻轉移到犧牲層上。然后,犧牲層形成具有1:3的占空比(即:線/空間=1/3)的虛擬柵極。通過硅氮化物(Si?N?)的沉積和各向異性蝕刻,形成具有與虛擬Gate相同關鍵尺寸的間隔層(即,占空比為1:1)。通過各向同性蝕刻步驟消除虛擬柵,只留下堆疊薄膜上的間隔層(Spacer)圖案。最后,使用Si?N?間隔層作為蝕刻掩模,將間隔層圖案轉移到硬掩模上。因此,使用自對準雙重圖案化,光阻的原始節距在最終圖案中減少了50%。換句話說,一個光阻線條可以創造兩個Spacer,從而將空間頻率加倍。

圖5:自對準雙重圖案化技術工藝流程

在FinFET的制造過程中,鰭狀體可以通過兩種方式之一進行圖案化:(1) 使用光阻作為掩模(即:“光阻定義”),和 (2) 使用間隔層作為掩模(即:“間隔層定義”)。傳統的光阻定義線條創建的邊緣具有非關聯的粗糙度,可以假設ρX=0。這是因為對于每個光阻的邊緣來說,聚合物聚集物的侵蝕是隨機進行的。另一方面,間隔層定義的線生成的邊緣相當相關。這是由于先進行了保形薄膜沉積過程,接著是高度均勻的各向異性蝕刻過程。這些步驟導致沿虛擬光阻定義特征的側壁形成了間隔層掩模(圖6)。如果間隔層寬度(對應于沉積薄膜的厚度)可以忽略(與LWR空間頻率的倒數值相比),間隔層定義的線將具有均勻的寬度。因此,可以假設ρX = 1。總之,如果在FinFET制造過程中使用自對準雙重圖案化技術,由LWR(而不是LER)引起的性能變化可以幾乎消除。

圖6:自對準雙重圖案化技術示意圖。此方法可以幾乎消除LWR量,實現完美相關的線邊緣。

【近期會議】

10月30-31日,由寬禁帶半導體國家工程研究中心主辦的“化合物半導體先進技術及應用大會”將首次與大家在江蘇·常州相見,邀您齊聚常州新城希爾頓酒店,解耦產業鏈市場布局!https://w.lwc.cn/s/uueAru

11月28-29日,“第二屆半導體先進封測產業技術創新大會”將再次與各位相見于廈門,秉承“延續去年,創新今年”的思想,仍將由云天半導體與廈門大學聯合主辦,雅時國際商訊承辦,邀您齊聚廈門·海滄融信華邑酒店共探行業發展!誠邀您報名參會:https://w.lwc.cn/s/n6FFne

聲明:本網站部分文章轉載自網絡,轉發僅為更大范圍傳播。 轉載文章版權歸原作者所有,如有異議,請聯系我們修改或刪除。聯系郵箱:viviz@actintl.com.hk, 電話:0755-25988573

審核編輯 黃宇

-

MOSFET

+關注

關注

142文章

6887瀏覽量

211510 -

半導體

+關注

關注

334文章

26171瀏覽量

209187 -

光刻

+關注

關注

8文章

310瀏覽量

30009 -

柵極

+關注

關注

1文章

161瀏覽量

20798

發布評論請先 登錄

相關推薦

CAD中如何使用塊標注粗糙度?

白光干涉儀可以測曲面粗糙度嗎?

什么是表面粗糙度?如何測量表面粗糙度?

怎么選擇適用的測量粗糙度儀器

表面粗糙度儀有哪些?

怎么選擇適用的測量粗糙度的儀器設備

Line Edge Roughness (LER) 線邊緣粗糙度

Line Edge Roughness (LER) 線邊緣粗糙度

評論