芯片引腳懸空時的電平狀態(高電平或低電平)并不是一個固定答案,它取決于多個因素,包括芯片類型、生產廠家、引腳特性以及周圍電路環境等。

首先,從邏輯門電路的角度來看,當引腳懸空時,其電平狀態可能會受到周圍電路環境和噪聲的影響,表現出隨機性。在一些情況下,引腳懸空可能會被視為高電平或低電平,但這并不是絕對的,而是取決于具體的電路設計和環境。

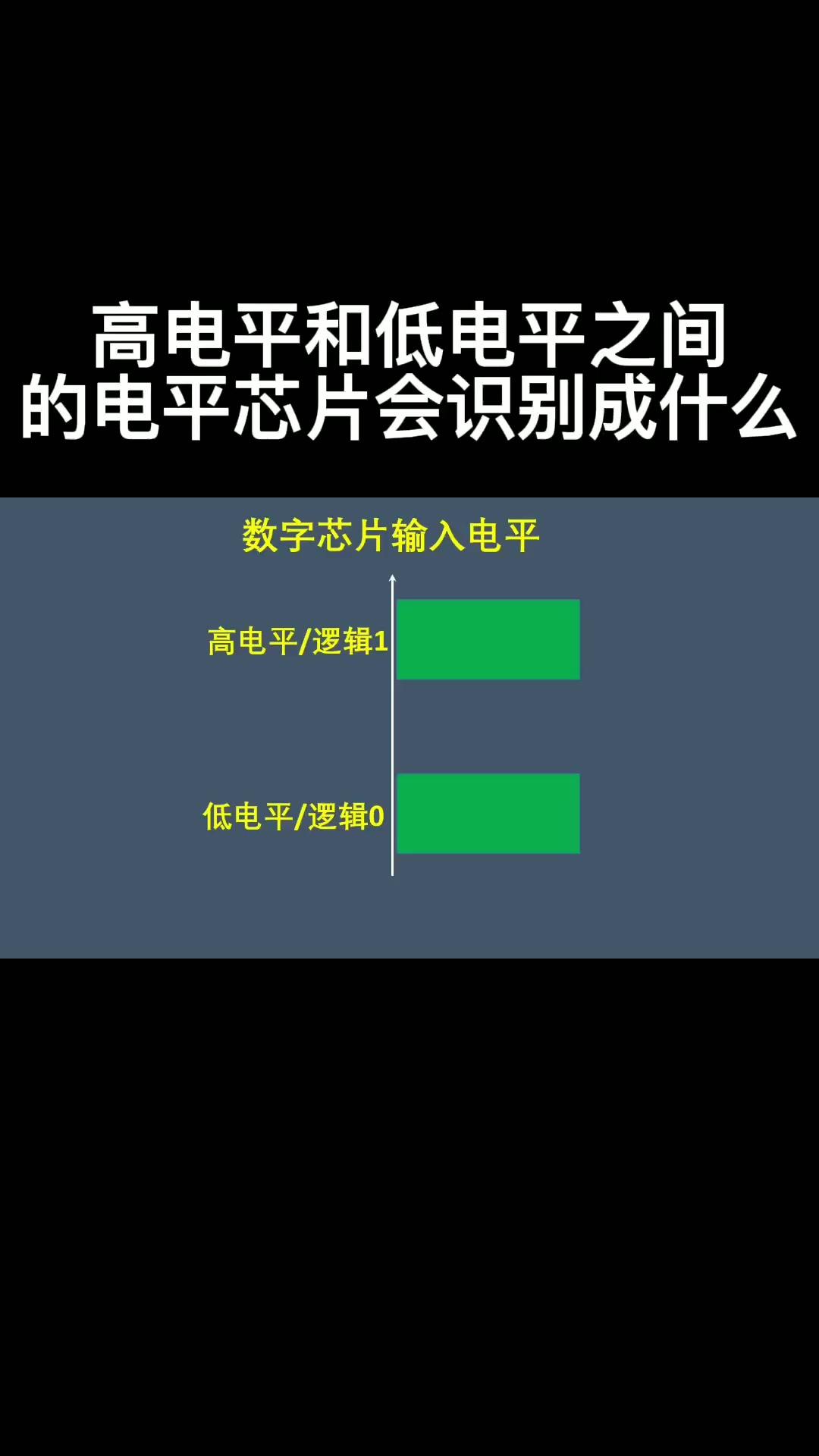

其次,對于某些芯片來說,其內部可能集成了上拉電阻或下拉電阻,這些電阻會在引腳懸空時提供一個確定的電平狀態。上拉電阻會將懸空引腳拉至高電平(如VCC),而下拉電阻則會將其拉至低電平(如GND)。但是,這種設計并不是所有芯片都具備的,需要根據具體的芯片數據手冊來確認。

此外,還有一些芯片引腳是設計為開漏輸出的,這種引腳在懸空時無法自行確定電平狀態,需要外部加上拉電阻來提供一個確定的電平。如果外部沒有加上拉電阻,那么懸空引腳的狀態將是未知的。

綜上所述,芯片引腳懸空時的電平狀態無法一概而論,需要根據具體情況來判斷。在設計和使用電路時,應該盡量避免引腳懸空的情況,以確保電路的穩定性和可靠性。如果必須讓引腳懸空,那么應該仔細查閱芯片數據手冊,了解該引腳的具體特性和要求,并采取相應的措施來確保電路的正常工作。

最后需要提醒的是,對于CMOS芯片來說,由于其輸入阻抗較高且對靜電敏感,因此引腳懸空時更容易受到噪聲和靜電的干擾,導致誤動作。因此,在設計CMOS電路時更應該注意避免引腳懸空的情況,并采取適當的保護措施來確保電路的穩定性和可靠性。

-

芯片

+關注

關注

454文章

50460瀏覽量

421967 -

下拉電阻

+關注

關注

4文章

147瀏覽量

20499 -

低電平

+關注

關注

1文章

113瀏覽量

13254 -

高電平

+關注

關注

6文章

147瀏覽量

21340

發布評論請先 登錄

相關推薦

高電平和低電平是什么意思?區別是什么?

低電平和高電平的區別

電子設計(4)高電平、低電平復位電路

單片機檢測IO口高電平、低電平、懸空三種狀態。

高電平、低電平復位電路

芯片引腳懸空是高電平還是低電平

芯片引腳懸空是高電平還是低電平

評論