R-S鎖存器(Reset-Set Latch)是一種基本的數字邏輯電路,用于存儲一位二進制信息。它由兩個交叉耦合的反相器(NOT gate)和兩個晶體管組成。R-S鎖存器在數字電路設計中具有廣泛的應用,如存儲數據、實現同步等。

- R-S鎖存器的基本概念

R-S鎖存器是一種存儲一位二進制數據的電路,它有兩個穩定狀態:Set狀態(S)和Reset狀態(R)。在Set狀態下,輸出Q為高電平,輸出Q'(Q的反相)為低電平;在Reset狀態下,輸出Q為低電平,輸出Q'為高電平。R-S鎖存器具有兩個輸入端:Set輸入(S)和Reset輸入(R),分別用于將鎖存器置為Set狀態和Reset狀態。

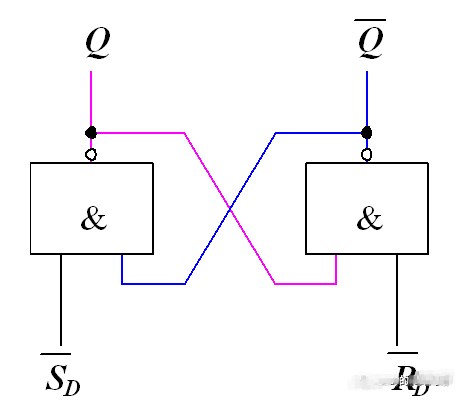

- R-S鎖存器的電路結構

R-S鎖存器的基本電路結構由四個晶體管組成,具體如下:

- 兩個NPN晶體管:Q1和Q2,分別連接到輸出Q和Q'。

- 兩個PNP晶體管:Q3和Q4,分別連接到輸出Q'和Q。

晶體管Q1和Q2的基極分別連接到輸入S和R,晶體管Q3和Q4的基極分別連接到輸出Q和Q'。這種交叉耦合的結構使得R-S鎖存器具有兩個穩定狀態。

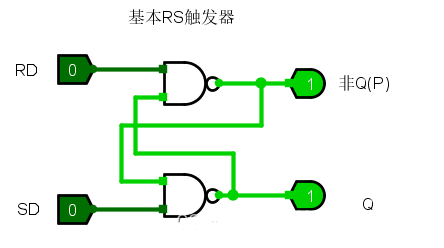

- R-S鎖存器的工作原理

R-S鎖存器的工作原理可以分為以下幾個步驟:

(1)初始狀態:假設R-S鎖存器處于Reset狀態,即輸出Q為低電平,輸出Q'為高電平。此時,晶體管Q1處于截止狀態,晶體管Q2處于飽和狀態;晶體管Q3處于飽和狀態,晶體管Q4處于截止狀態。

(2)Set操作:當輸入S為高電平時,晶體管Q1導通,輸出Q變為高電平。由于晶體管Q1和Q4的交叉耦合,晶體管Q4截止,輸出Q'變為低電平。此時,R-S鎖存器進入Set狀態。

(3)Reset操作:當輸入R為高電平時,晶體管Q2導通,輸出Q'變為高電平。由于晶體管Q2和Q3的交叉耦合,晶體管Q3截止,輸出Q變為低電平。此時,R-S鎖存器進入Reset狀態。

(4)保持狀態:當輸入S和R都為低電平時,R-S鎖存器保持當前狀態不變。

- R-S鎖存器的優缺點

優點:

- 結構簡單:R-S鎖存器由四個晶體管組成,結構簡單,易于實現。

- 存儲能力強:R-S鎖存器可以存儲一位二進制數據,具有基本的存儲功能。

缺點:

- 存在競爭冒險:當輸入S和R同時為高電平時,R-S鎖存器可能進入不穩定狀態,導致輸出不確定。

- 功耗較高:由于晶體管的導通和截止,R-S鎖存器的功耗相對較高。

- R-S鎖存器的應用

R-S鎖存器在數字電路設計中具有廣泛的應用,如:

- 數據存儲:R-S鎖存器可以用于存儲數據,實現數據的暫存和傳遞。

- 同步控制:R-S鎖存器可以用于實現同步控制,確保數據在不同時鐘域之間的正確傳輸。

- 寄存器設計:R-S鎖存器可以作為寄存器的基本單元,用于實現更復雜的寄存器結構。

- R-S鎖存器的改進

為了解決R-S鎖存器的競爭冒險問題,可以采用以下改進措施:

- 使用D鎖存器:D鎖存器是一種改進的R-S鎖存器,它通過引入一個使能端(Enable),在使能端為高電平時,D鎖存器的輸出跟隨輸入D,避免了競爭冒險問題。

- 使用JK鎖存器:JK鎖存器是一種更高級的鎖存器,它通過引入兩個輸入J和K,可以實現更靈活的控制邏輯,避免了競爭冒險問題。

-

RS

+關注

關注

3文章

138瀏覽量

109754 -

二進制

+關注

關注

2文章

761瀏覽量

41478 -

鎖存器

+關注

關注

8文章

903瀏覽量

41317 -

數字邏輯電路

+關注

關注

0文章

100瀏覽量

15748

發布評論請先 登錄

相關推薦

RS鎖存器的工作原理和應用實例

Rs鎖存器的工作原理、優缺點及應用

Rs鎖存器的工作原理、優缺點及應用

評論