SR鎖存器作為數字電路中的一個基礎元件,其設計和使用過程中存在約束項的原因是多方面的。這些約束項旨在確保SR鎖存器能夠穩定、可靠地工作,避免產生不可預測或錯誤的狀態。

一、SR鎖存器的基本工作原理

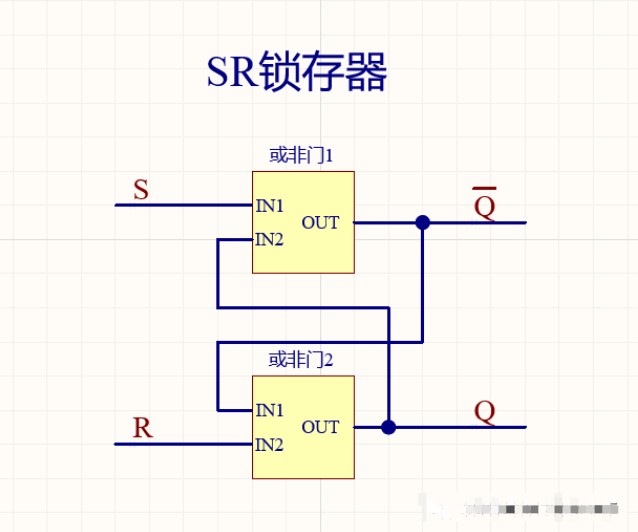

SR鎖存器由兩個交叉連接的反饋環組成,通常包含兩個邏輯門(如或非門或非門),通過控制輸入信號S(Set,置位)和R(Reset,復位)來控制其狀態。SR鎖存器有兩個輸出端Q和Q',其中Q表示當前狀態,Q'是Q的補碼。其基本工作原理可以概括為:

- 當S=1且R=0時,鎖存器被設置為1狀態,即Q=1、Q'=0。

- 當S=0且R=1時,鎖存器被重置為0狀態,即Q=0、Q'=1。

- 當S=0且R=0時,鎖存器保持當前狀態不變。

二、約束項存在的原因

1. 避免不確定狀態

原因闡述 :

- S和R同時為1的情況 :當S和R同時為高電平時(在某些設計中為低電平,取決于邏輯門類型),SR鎖存器會進入一種不確定狀態。這是因為S和R的同時有效違反了鎖存器的正常操作條件,導致輸出Q和Q'無法穩定地保持在一個明確的狀態。這種不確定狀態可能導致數據錯誤、邏輯混亂甚至系統崩潰。

- 競爭冒險 :在信號傳輸過程中,由于信號傳輸延遲和電路中的非理想因素(如噪聲、器件差異等),S和R信號可能在極短的時間內同時達到有效電平,從而產生競爭冒險現象。這種競爭冒險同樣會導致鎖存器進入不確定狀態。

解決措施 :

- 設計約束:在電路設計階段就明確S和R不能同時為有效狀態的約束條件,并在實際電路中通過邏輯門電路或其他控制元件來確保這一約束得到遵守。

- 時序控制:在信號傳輸過程中加入適當的時序控制機制,以確保S和R信號的變化是順序發生的,而不是同時發生的。

2. 維持穩定性

原因闡述 :

- 保持原有狀態的需求 :在數字電路中,鎖存器經常需要保持其存儲的數據不變,以便在后續操作中使用。當S和R均為0時,鎖存器應維持其原有狀態不變。這是通過反饋環的正反饋機制實現的。如果反饋環的設計或實現存在問題,可能導致鎖存器無法穩定地保持其狀態。

解決措施 :

- 反饋環設計:優化反饋環的設計,確保其能夠穩定地維持鎖存器的狀態。

- 噪聲抑制:采取噪聲抑制措施,如增加濾波電路、使用低噪聲器件等,以減少噪聲對鎖存器穩定性的影響。

3. 同步控制

原因闡述 :

- 與時鐘信號的同步 :在某些應用中,SR鎖存器需要與時鐘信號同步工作。時鐘信號用于控制鎖存器的狀態更新時機。如果S和R信號的變化與時鐘信號不同步,可能導致鎖存器在錯誤的時刻更新狀態,從而影響整個電路的正常工作。

解決措施 :

- 時鐘同步機制:設計時鐘同步機制,確保S和R信號的變化在時鐘信號的特定邊緣(如上升沿或下降沿)發生。

- 同步電路設計:采用同步電路設計方法,將鎖存器與其他電路元件的操作同步到時鐘信號的邊緣上。

4. 功耗和速度優化

原因闡述 :

- 功耗考慮 :在設計SR鎖存器時,需要權衡功耗和速度之間的關系。較低的功耗通常意味著較慢的速度,而較高的速度則可能帶來較高的功耗。因此,設計者需要在滿足性能要求的前提下盡可能降低功耗。

- 速度需求 :在某些高速應用中,SR鎖存器需要具有較快的響應速度和較低的時延。這要求設計者優化鎖存器的電路設計以提高其速度性能。

解決措施 :

- 低功耗設計:采用低功耗設計技術如動態功耗管理、電源門控等以降低功耗。

- 高速電路設計:優化鎖存器的電路布局和信號路徑以減少時延并提高響應速度。

三、總結

SR鎖存器約束項的存在是為了確保鎖存器能夠穩定、可靠地工作并避免產生不可預測或錯誤的狀態。這些約束項包括避免S和R同時為有效狀態以防止不確定狀態的產生、維持鎖存器的穩定性、與時鐘信號的同步以及優化功耗和速度等方面。通過遵守這些約束項并采取相應的解決措施,可以設計出高性能、高可靠性的SR鎖存器以滿足各種應用需求。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

邏輯門

+關注

關注

1文章

141瀏覽量

24025 -

數字電路

+關注

關注

193文章

1600瀏覽量

80497 -

輸入信號

+關注

關注

0文章

446瀏覽量

12536

發布評論請先 登錄

相關推薦

兩種SR鎖存器的約束條件

基本約束條件: SR鎖存器是一種基本的數字邏輯電路,用于存儲一位二進制信息。它有兩個輸入端:S(Set)和R(Reset),以及兩個輸出端:

sr鎖存器不定狀態的產生原因

一、引言 SR鎖存器(Set-Reset Latch)是數字電路中的一種基本存儲元件,用于存儲一個比特(bit)的數據。它由兩個互補的門電路組成,通常是兩個非門(或非門、與非門)構成,

sr鎖存器如何確定q的值

SR鎖存器是一種重要的數字電路元件,用于存儲和鎖定一個比特的信息。其輸出端口Q的值是根據輸入端口S(置位)和R(復位)的信號來確定的。 一、SR

SR鎖存器的特性表、工作原理及應用

SR鎖存器(Set-Reset Latch)是一種基本的數字邏輯電路,用于存儲一位二進制信息。它具有兩個穩定狀態:置位狀態(Set)和復位狀態(Reset)。

SR鎖存器的Q非和Q*是什么關系

SR鎖存器是一種基本的數字邏輯電路,用于存儲一位二進制信息。它由兩個觸發器(Set和Reset)組成,分別控制輸出Q和Q非。在這篇文章中,我

SR鎖存器有約束項的原因

SR鎖存器有約束項的原因

評論