或許,你會認為DPDK(Data Plan Development Kit)是一個應用在網絡應用層上的高速數據傳輸標準;或許,你認為DPDK是Intel制定的一套規格;或許,你認為DPDK在CPU和ASIC界是受限的保密的;亦或許,你都沒有聽說過DPDK,考慮到它的發展歷史,確實很有可能。所以,如果以上的這些假設中有一項是正確的,那么你應該讀讀下面的內容。

最初,DPDK是一個數據層的庫集,后來Intel開發了專門針對Intel X86微處理器的可以快速分組處理NIC(網絡接口控制)的驅動,這就是DPDK的前世。而今生的DPDK,在去年四月份,已經成為一個Linux基金項目,并且可以在DPDK.org上看到。

DPDK主要包括以下幾個大家常用的主要庫:

當需要最小化CPU周期數時(一般小于80)發送和接收數據包;

開發快速分組算法;

運行第三方快捷路徑堆棧。

迄今為止,DPDK聽起來確實像是一個特殊的網絡開發工具,但是,也正如Atomic Rules的CTO Shep Siegel所說:“如果你可以使你的數據傳輸問題看起來僅僅是一個數據包傳輸問題的話,那么,在你的開發流程中,DPDK可能就是一條比較有幫助捷徑”。

Arkville:

并且,關于近期更多DPDK的細節,Siegel的團隊可能更為了解,主要是因為他的團隊剛發布了Arkville,這是一個支持DPDK的FPGA/GPP的數據傳輸IP塊和DPDK PMD(Poll Mode Driver,與Linux基金開源DPDK庫17.05發行版協作,允許Linux DPDK應用分流服務器循環到FPGA門)。同時,Atomic Rules的Arkville發行版還兼容Xilinx Vivado2017.1(這是今年四月份剛剛發布Vivado設計工具的最新版本)。此外,Atomic Rules提供了兩個簡單的demo設計(均可通過Vivado 2017.1進行編譯):

4端口,4隊列10GbE demo(Arkville + 4 x 10 GbE MAC)

單端口單隊列 100GbE demo(Arkville + 1 x 100 GbE MAC)

以上這兩個例子都是數據移動器。準確來說,Arkville是一個數據包導管道,這個管道有一個CPU端的DPDK接口,一個FPGA端的AXI接口,同時,在Arkville管道上還有一個可以很方便地增加用戶用于處理這些數據包的硬件設計點,同時這也是CPU分流邏輯的所在。

Atomic Rules開發的Arkville IP和所有的Xilinx UltraScale器件都協作良好,但是,與Xilinx UltraScale+ 的全可編程器件協作的更好,這主要歸功于全可編程器件內部集成兩個PCIe Gen3 x 16控制器(包括Kintex UltraScale+和Virtex UltraScale+ FPGA系列器件和Zynq UltraScale+ MPSoC系列器件)。

為什么呢?

正如BittWare企業的VPCraig Lund主管所說 “100G的以太網是不太可能的,但是你是否可以在服務器端通過使用PCIe來達到這個速率 [使用一個PCIe Gen3 x 16接口]是不明確的。從PCIe的參數來看,這看起來似乎簡單,但事實并非如此” 。Lund還說到,如果你正在處理一個最小尺寸的數據包,那么可以采用大量超過14百萬每秒來實現。但是如果你正在處理一個大的數據包,那將需要更多的帶寬,這或許正是一個對單PCIe Root 復合體生產力的挑戰,不過從實際出發,確實一個不夠。

應用Atomic Rules的ArkvilleIP,BittWare開發出了自己的產品——XUPP3R PCIe卡,同時它還組合了一個Xilinx的Virtex UltraScale+ VU13P FPGA芯片。BittWare的XUPP3R PCIe板卡的眾多獨特特征之一就是它有兩個PCIe Gen3 x 16 端口:一個在邊緣連接器時有效,另一個是一個可選的連續擴展口。其中第二個PCIe Gen3x16口可以用作增加帶寬的第二PCIe槽。

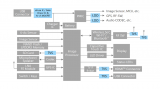

然而,盡管Lund沒有多說,這里卻不僅僅需要兩個PCIe Gen3 x 16插槽,而是需要兩個PCIe Gen2 Root復合體,也就意味著需要一個兩組插槽的母板,然后兩個CPU工作處理數據通路。以下簡化的方框圖可以說明Lund的觀點:

BittWare不僅開發了具有兩個PCIe Gen3 x 16端口的XUPP3R PCIe卡,此外,BittWare還使用它的XUPP3R PCIe卡和Arkville IP共同開發了兩個產品:

StreamSleuth,一個100GbE的網絡數據包處理器具。

StreamSurge,一個1U盒子,內有Intel E5 v4 單插座服務器和由XUPP3R PCIe 卡設計的NIC以及BittWare的StreamSurge IP。

不過,需要對號的是:Arkville是Atomic Rules提供的一個IP,XUPP3R PCIe卡是BittWare提供的產品,兩者不可混淆。

總結:

目前,大量數據爆發,除了固件運輸之外,最方便的總線(PCIe/ETH)線路傳輸,不僅速率高同時安全性高,但是隨著形勢的發展,對其速率的要求越來越高,期望Xilinx FPGA可以為提高數據傳輸速率方面做出更多貢獻。

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601858 -

cpu

+關注

關注

68文章

10825瀏覽量

211151 -

大數據

+關注

關注

64文章

8863瀏覽量

137300

發布評論請先 登錄

相關推薦

PCBA供應商如何在競爭中脫穎而出?

智能穿戴企業如何在激烈的競爭中脫穎而出?

即將到來的AI時代,誰將笑傲江湖

巨大的汽車電子市場中國IC如何脫穎而出?

人工智能芯片領域中脫穎而出的芯片生力軍有哪些

中興云終端脫穎而出,榮獲德國iF設計大獎!

Maxim Integrated讓您的產品脫穎而出!

如何在安防大數據時代讓視頻監控脫穎而出

FPGA將在眾多AI芯片中脫穎而出

疫情期間脫穎而出 Neolix無人車業務激增

為何只有丹麥“脫穎而出”,成為風電大國?

“脫穎而出”的同步磁阻電機有何優勢

運動相機為什么會脫穎而出

CPU與FPGA的優勢如何在大數據時代脫穎而出

CPU與FPGA的優勢如何在大數據時代脫穎而出

評論