引言

隨著集成電路規模的不斷擴大,從設計到流片(Tape-out)的全流程中,驗證環節的核心地位日益凸顯。有效的驗證不僅是設計完美的基石,更是確保電路在實際應用中穩定運行的保障。尤為關鍵的是,邏輯或功能錯誤是導致流片失敗的首要原因,占比高達50%。功能驗證正是解決這一難題的利器,它助力工程師精準識別邏輯設計漏洞、性能不達標問題以及設計代碼中的功能缺陷,從而最大限度地規避流片風險。

針對超大規模集成電路(VLSI)設計,目前功能驗證有兩種方法:動態仿真驗證和形式驗證(Formal Verification)。形式驗證采用數學方法來比較原設計和修改設計之間的邏輯功能的異同,而動態仿真驗證是對兩設計施加相同的激勵后,觀測電路對激勵的反應異同。

面對大型設計,傳統的動態仿真驗證方法在覆蓋率和效率上面臨挑戰。為了達到100%的覆蓋率,動態仿真驗證所需要的矢量就會越多,這時形式驗證在這方面就有優勢了,成為現代IC設計驗證流程中的關鍵一環。本文就以 “芯天成EsseFCEC”工具為例,來介紹形式驗證的流程和基本概念。

01

什么是形式驗證

形式驗證是一種基于嚴格數學推理的設計驗證技術,它摒棄了物理測試與模擬的依賴,專注于通過靜態、全面的邏輯分析來確保設計的正確性。此方法顯著降低了對龐大測試集的需求,并力求實現接近完美的驗證覆蓋率。

形式驗證作為EDA、數學及編程語言等多學科交叉的產物,自上世紀90年代起便嶄露頭角,最初應用于RTL代碼與門級網表的LEC(邏輯等價性檢查),隨后逐步擴展到各類EDA工具,以應對不同驗證場景的需求。

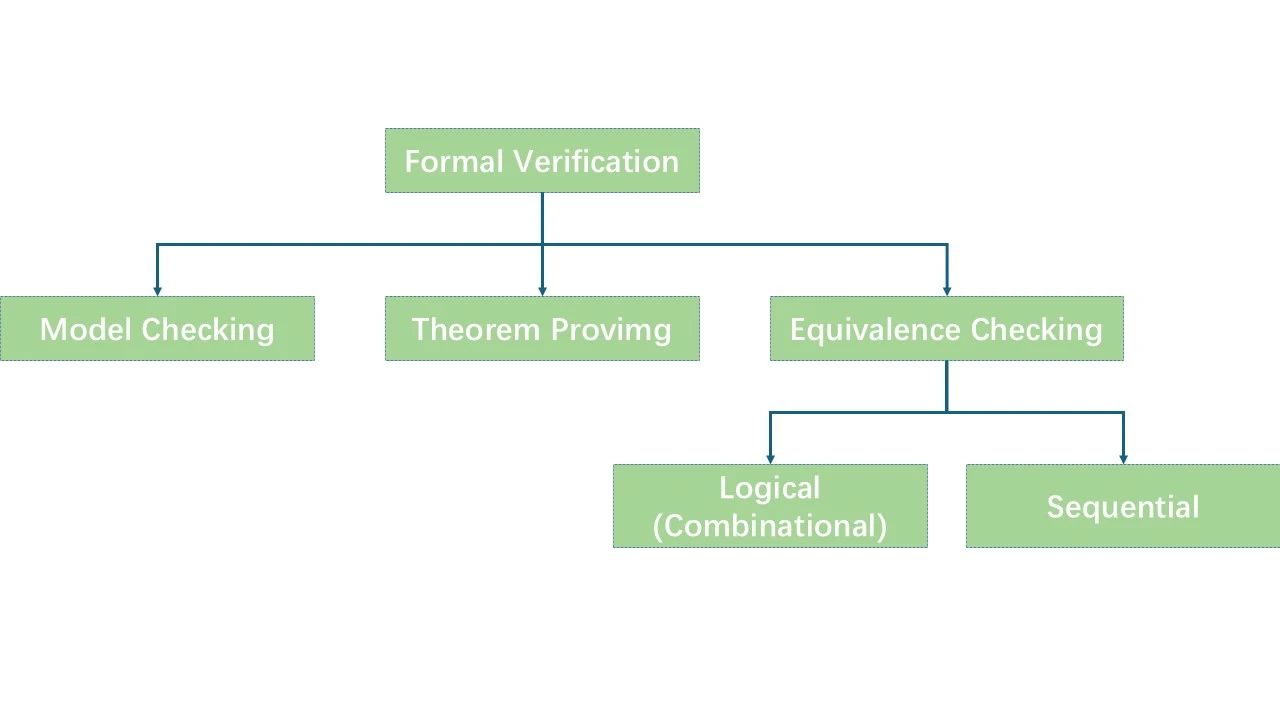

目前,形式驗證主要分為兩個技術方向:等價性檢查和屬性檢查。其中。等價性檢查,作為核心驗證手段,通過對比功能驗證后的HDL設計與綜合后的網表功能,確保兩者在功能層面上的完全一致,從而保證門級電路與寄存器傳輸級(Register Transfer Level, RTL)模型之間的一致性。這一方法有效防范了綜合工具潛在的缺陷及人為誤操作,對于提升設計質量至關重要。

形式驗證的實施涉及多個關鍵環節:

屬性定義(Properties):精確闡述設計需遵循的特性與規范,涵蓋時序邏輯、狀態轉換規則及各項約束條件。

規約語言:采用如SystemVerilog Assertions(SVA)、Property Specification Language(PSL)等形式化規約語言,將屬性與約束轉化為可驗證的表達式。

定理證明器(Theorem Provers):依托形式化邏輯與推理機制,自動驗證屬性是否成立,為設計邏輯的正確性提供堅實保障。

模型檢查器(Model Checkers):全面探索系統狀態空間,尋找可能違反預定性質的執行路徑,確保設計在所有可能情況下均能滿足既定要求。

形式驗證的基本流程是一個連貫且系統化的過程。這一過程從明確驗證目標開始,設計團隊首先需要界定哪些部分或功能需要接受形式驗證的嚴格審查。接著,采用形式規約語言(如SystemVerilog Assertions、PSL)定義屬性和規約,作為驗證基礎。進入驗證環境配置階段,團隊選擇適合的驗證工具(定理證明器、模型檢查器),并依據設計特性和需求進行優化配置,以確保驗證效率與準確性。

驗證執行為核心,定理證明器通過數學推理驗證屬性與規約的正確性,模型檢查器則全面探索系統狀態空間,檢查違規執行序列。驗證結束后,團隊分析驗證結果,識別并修正設計中的錯誤或不一致。此過程可能多次迭代,直至設計完全符合驗證要求。

02

形式驗證工具的挑戰

形式驗證的流程雖然復雜且嚴謹,但它為設計團隊提供了一種高效且可靠的驗證方法。通過遵循這一流程,設計團隊可以顯著降低設計錯誤的風險,提高產品的質量和可靠性。然而,隨著現代芯片設計的復雜性和規模不斷增長,形式驗證在實際應用中面臨多重挑戰:

復雜性增加,性能不足:現代芯片設計的復雜性和規模不斷增長,對驗證工具的性能提出了更高要求。現有工具在處理大規模設計時可能面臨性能瓶頸,導致驗證過程耗時過長。

多樣化的設計環境:不同的設計團隊可能使用不同的設計語言和平臺,這要求驗證工具具備廣泛的兼容性和集成能力。然而,多樣化的設計環境可能導致兼容性和集成性方面的挑戰。

可擴展性需求增加:隨著技術的不斷進步和新的設計需求的出現,驗證工具需要具備良好的可擴展性,以快速適應新的設計規范和標準。這對工具的開發和維護提出了更高要求。

復雜的設計錯誤檢測:在復雜的設計中,子系統之間的交互和邏輯路徑可能非常復雜,驗證工具需要能夠準確地檢測這些復雜場景中的錯誤和不一致之處。這要求工具具備強大的錯誤檢測能力和智能化的分析手段。

03

芯天成EsseFormal形式驗證軟件

芯天成EsseFormal形式驗證軟件是一款功能全面的驗證解決方案,專為數字芯片設計領域的復雜驗證挑戰而設計。其核心包含五種工具套件,每一種都針對特定的驗證需求提供高效、精準的支持。

EsseFECT(形式化等價性驗證):該工具專注于驗證C-to-RTL的轉換過程中,設計的等價性是否得以保持。這確保了設計在不同抽象層次間的轉換無誤,是確保設計一致性的重要環節。

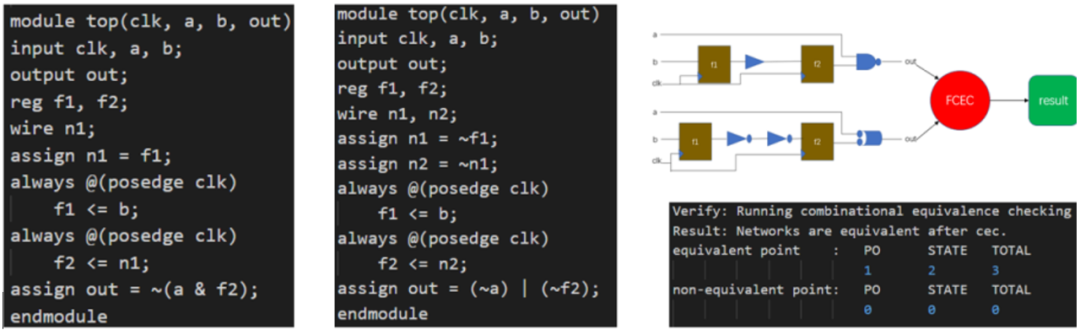

EsseFCEC(組合邏輯等價性驗證):作為EsseFormal的明星產品,EsseFCEC專門用于驗證芯片設計中各電路模塊之間的組合邏輯等價性。它不僅支持RTL到Netlist的轉換驗證,還涵蓋版本間差異的比較,確保設計更改不會引入錯誤。其強大的綜合優化技術支持(如Clock-gating、multibit register banking和FSM recoding)顯著提升了驗證效率和性能。此外,對DesignWare元件庫的支持以及大位寬datapath驗證的能力,進一步拓寬了EsseFCEC的應用范圍。

EsseFPV(模型檢查):通過遍歷設計的狀態空間,EsseFPV能夠發現設計中可能存在的違反預定義屬性的行為,是確保設計行為符合預期的關鍵工具。

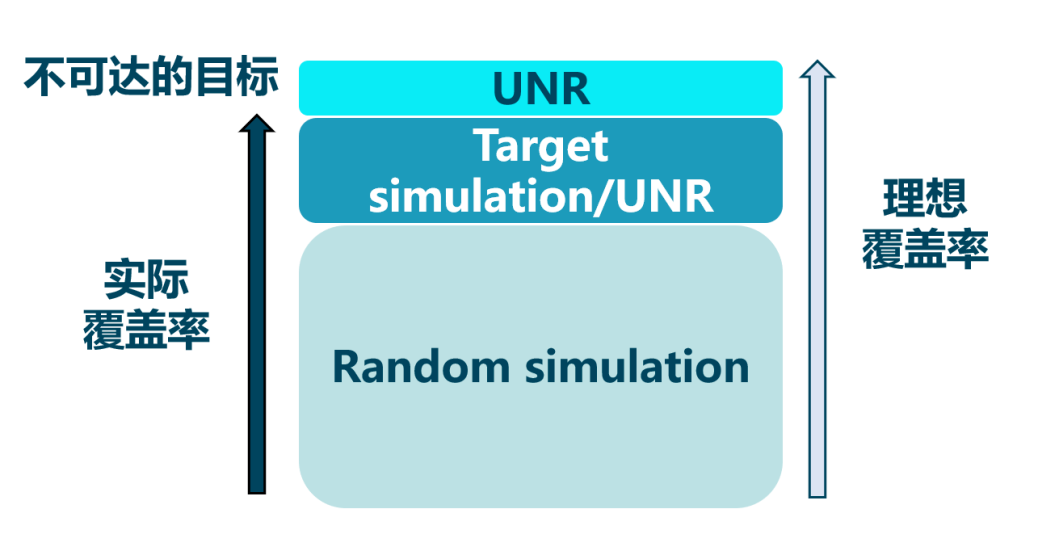

EsseCC與EsseUNR(實用驗證Apps):這兩個工具提供了額外的實用功能。EsseCC是一個高效的連接性檢查驗證工具,為用戶提供快速的錯誤檢測以及信號到信號的預期設計行為驗證。EsseCC以RTL電路和連接規范作為輸入,快速檢查設計是否符合連接規范。而EsseUNR是一款高效的覆蓋不可達性檢查工具。使用傳統的驗證方式,在驗證后期,通過編寫測試用例提升驗證覆蓋率的難度陡然上升。該工具具有更高效、更準確、更易上手的優點,可對未覆蓋的代碼進行全面的不可達性檢查。

芯天成EsseFormal的定制化和集成化特點,使得它能夠精準匹配不同用戶的特定需求,從而顯著降低驗證時間,提高驗證的完整性和準確性。其簡潔易用的圖形用戶界面,讓驗證過程更加直觀和高效,即使是初次接觸形式驗證的用戶也能快速上手。

04

驗證發展方向:覆蓋率的提升

在當前的硬件設計領域中,隨著設計復雜度的急劇增加,驗證已成為確保芯片功能和性能可靠性的關鍵環節。驗證技術的發展方向,尤其是覆蓋率的提升,成為了行業關注的焦點。思爾芯的軟件仿真芯神馳PegaSim通過其創新性的解決方案,與國微芯的形式驗證工具進行無縫集成,為提升驗證的全面性和效率樹立了新的標桿。

覆蓋率是衡量驗證完整性的重要指標,它反映了驗證過程中測試向量對設計代碼覆蓋的廣度和深度。然而,在復雜的硬件設計中,往往存在難以觸及的代碼區域,即所謂的“不可達部分”。這些區域若未經充分驗證,就可能成為潛在的設計漏洞。因此,提升覆蓋率,特別是針對不可達部分的驗證,對于確保設計質量和可靠性至關重要。

思爾芯的軟件仿真PegaSim通過與國微芯的形式驗證工具相結合,實現了對覆蓋率中不可達部分進行深入驗證。這一解決方案不僅增強了軟件仿真過程中的代碼覆蓋率,還通過增加激勵或優化代碼的方式,進一步提高了驗證的全面性和準確性。同時,PegaSim還支持對指定模塊或特定代碼行進行精細化的覆蓋不可達性檢查,幫助設計團隊精準定位并消除無意義或冗余的代碼,從而優化內在邏輯,提升整體設計質量。

面對日益復雜的硬件設計,單一的驗證方法已難以滿足全面驗證的需求。因此,驗證技術的發展趨勢是多種驗證方法的融合與互補。軟件仿真、硬件仿真、原型驗證、以及形式驗證等方法各有千秋,它們在不同的驗證階段和側重點上發揮著不可替代的作用。通過綜合運用這些驗證方法,可以實現對硬件設計的全方位、多角度檢驗,從而確保設計的正確性和可靠性。

-

集成電路

+關注

關注

5367文章

11166瀏覽量

358418 -

IC

+關注

關注

36文章

5787瀏覽量

174397 -

芯片設計

+關注

關注

15文章

980瀏覽量

54622

發布評論請先 登錄

相關推薦

Zettabyte與緯創攜手打造臺灣首個超大規模AI數據中心

谷歌正在考慮在越南建設超大規模數據中心

超大規模集成電路(VLSI)中不可或缺的5種二極管

如何利用低功耗設計技術實現超大規模集成電路(VLSI)的電源完整性?

SAS 24G+規范發布,為超大規模數據中心HDD和SSD

燧原科技與清程極智攜手共創AI未來:共筑超大規模智算集群新篇章

Cerebras推WSE-3芯片,性能翻倍,助力超大規模AI模型訓練

晶晟微納發布N800超大規模AI算力芯片測試探針卡

中國電信規劃在上海建設首個國產超大規模算力液冷集群

Cadence推出新版Palladium Z2應用

一文了解SOC的DFT策略及全芯片測試的內容

形式驗證如何加速超大規模芯片設計?

形式驗證如何加速超大規模芯片設計?

評論