山東濟南,2017年10月10日訊,山東高云半導體科技有限公司(以下簡稱“山東高云半導體”)今天宣布推出基于中密度晨熙?家族的GW2A系列FPGA芯片的DDR類儲存器接口IP核初級版(Gowin Memory Interface IP),包括相關IP軟核、參考設計及開發板等完整解決方案。

高云DDR類儲存器接口IP核初級版目前是一個通用的DDR2存儲器接口IP,兼容JESD79-2標準。該IP包含通用的DDR2內存控制器(Memory Controller,MC)與對應的物理層接口(Physical Interface,PHY)。后續升級版會支持晨熙?家族的GW2AR系列內嵌DDR類儲存器式FPGA,功能升級將延及DDR1、DDR3內存控制器與對應的物理層接口。

高云DDR類儲存器接口IP核初級版為用戶提供一個通用的用戶命令接口,另一端通過PHY連接至內存芯片,完成用戶對存儲器的訪存要求。“高云DDR類儲存器接口軟核品種豐富,能支持目前市場上的主流DDR類儲存器。”高云半導體軟核研發部門負責人高級經理高彤軍先生解釋說,“目前推向市場的IP核初級版已經能夠滿足我們很多客戶的應用要求,但是還遠遠沒有達到高云器件的潛力,我們最終目標速度是達到800Mbps到1Gbps的范圍。”

“我們提供簡明易用的IP調用界面,同時提供可用于驗證DDR2控制器IP性能的開發板和參考設計。”高云半導體市場副總裁兼中國區銷售總監黃俊先生表示,“高云半導體會持續在IP核的開發方面加大投入,旨在提高用戶FPGA的設計余量和整體系統的可靠性,同時縮短用戶的設計周期,可以讓廣大用戶盡快熟悉國產FPGA的架構,逐漸認同國產FPGA品牌的品質和良好的技術支持服務。”

IP主要特征

DDR2 MC與PHY的時鐘比例為1:2;

支持存儲器數據路徑寬度為8、16、24、32、40、48、56、64和72位;

支持單列UDIMM和SODIMM內存模塊;

支持x4、x8和x16兩種數據寬度的內存芯片;

可編程突發長度4或8;

可配置的CL;

可配置的CWL;

可配置的tFAW;

可配置的tRAS;

可配置的tRCD;

可配置的tRFC;

可配置的tRRD;

可配置的tRTP;

可配置的tWTR;

支持動態片上終端ODT的控制;

支持自動刷新和用戶啟動刷新,自動刷新間隔可配置。

IP工作頻率

DDR2 SDRAM數據速率目前為500Mbps~560Mbps;

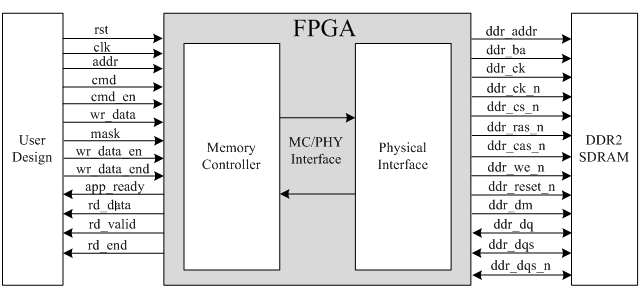

IP整體結構

高云DDR類儲存器接口IP核的基本結構,包含Memory Controller、Physical Interface等主要模塊。圖中的User Design block 是FPGA中需要與外部DDR2 SDRAM芯片所連接的用戶設計。

GW2AR、GW2A系列FPGA

GW2AR系列為內嵌DDR類儲存器式FPGA,GW2A系列FPGA支持外掛DDR類儲存器。其中,GW2AR-18K LQ176內嵌128M DDR1;GW2A-18KBGA封裝與 GW2A-55K BGA封裝支持外掛DDR2。

開發板與參考設計

高云DDR類儲存器接口IP核初級版, 參考設計及開發板支持GW2A-18K/55K BGA封裝FPGA對接通用DDR2存儲器,后續升級版會支持GW2AR系列內嵌DDR類儲存器式FPGA,功能升級將延及DDR1、DDR3內存控制器與對應的物理層接口。

關于山東高云半導體:

山東高云半導體科技有限公司于2014年3月成立,位于濟南高新區齊魯軟件園,作為廣東高云半導體科技股份有限公司的全資子公司,山東高云半導體致力于國產FPGA解決方案并推動其產業化,旨在推出具有核心自主知識產權的民族品牌FPGA芯片。

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601826 -

IP核

+關注

關注

4文章

326瀏覽量

49428 -

高云半導體

+關注

關注

20文章

123瀏覽量

50467

發布評論請先 登錄

相關推薦

瑞薩電子發布全新DDR5 MRDIMM內存接口芯片組

10月25日|英飛凌儲存器解決方案線上技術論壇

萊迪思半導體推出全新MachXO5D-NX FPGA和Sentry解決方案

益昂半導體推出用于車載網絡的NemoTM系列芯片

高云半導體與香港理工大學共探FPGA技術在智能電網領域的應用

高云半導體舉辦22nm研討會,展示先進半導體技術成果

回顧:高云半導體成功舉辦22nm產品及方案研討會

昂科燒錄器支持GOWIN高云半導體的非易失性FPGA GW2AN-UV9XUG256

具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數據表

具有同步降壓控制器、2A LDO和緩沖基準的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內存電源解決方案數據表

完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表

高云半導體推出GW2A系列FPGA芯片的DDR類儲存器接口解決方案

高云半導體推出GW2A系列FPGA芯片的DDR類儲存器接口解決方案

評論