背景

數(shù)據(jù)中心采用FPGA做加速器已經(jīng)成為主流,像MS的Catapult,Amazon基于Xilinx FPGA的AWS F1,Intel的Altera,Baidu公司等。數(shù)據(jù)中心具有大規(guī)模并行數(shù)據(jù)處理,高數(shù)據(jù)吞吐量,低延時,能效高等特點。但是存在兩個問題,第一個是軟件的問題,軟件移植和保證一定加速的工作負荷;第二個是硬件的問題,配備眾核處理器,25-100G的網(wǎng)絡接口卡,一些DRAM/HBM通道,容易時序收斂等。

現(xiàn)介紹一種GRVI Phalanx FPGA加速器結(jié)構(gòu)。其中,GRVI是一種基于FPGA的有效的RISC-V運算單元,即RISC-V RV321軟處理器核;Phalanx是一種并行FPGA加速器框架,由PE集群,SRAM,加速器,DRAM,I/O控制器等組成,減少在開發(fā)和管理FPGA加速器時所需付出的消耗和努力;還需要Hoplite NoC,它是一種基于FPGA優(yōu)化的定向2D環(huán)形片上網(wǎng)絡系統(tǒng),用到的技術還有局部內(nèi)存共享和全局信息流通等。

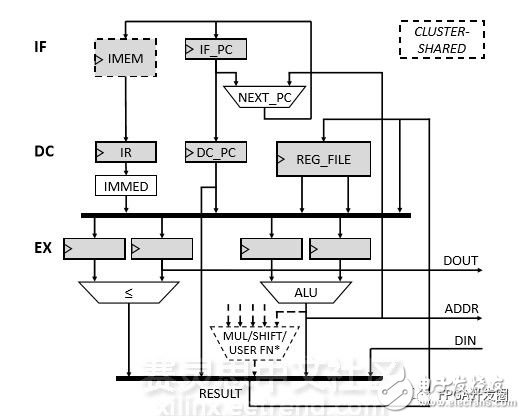

圖.1 GRVI運行單元

先看一下GRVI Phalanx的1680個核的運算單元,運算單元是基于32位的RISCV微處理器架構(gòu),在一個多核心的芯片中,去掉了每一個核心中的不必要的資源,目的是減小每一個單元的芯片面積。因此,每一個GRVI處理單元都是三級流水的,采用用戶模式下的RV321核心,減掉了部分不必要的位和其他模塊,具體結(jié)構(gòu)如圖.1所示。每個GRVI運行單元需要320個LUT,而且能夠跑在375MHz的頻率下,看到博主Jan Gray所設計的眾核處理器芯片(詳情見“GRVI Phalanx: A Massively Parallel RISC-V FPGA Accelerator Framework: A 1680-core, 26 MB SRAM Parallel Processor Overlay on Xilinx UltraScale+ VU9P”),其特點是每一個GRVI運行單元都是手動排布的,將單個處理器單元在Xilinx FPGA的UltraScale+的架構(gòu)下重復1680次,并將生成的文件下載到板卡Xilinx VCU118 Eval Kit上的Virtex UltraScale+VU9P FPGA芯片中。

將一大堆的處理器核心一股腦的扔進Xilinx 的Virtex UltraScale+ VU9P FPGA芯片中聽起來很有趣,但是如果不給每一個核心都匹配一些內(nèi)存的話,也不能給這么多核心的處理器核心委以重任。因此,每一個在集群中的GRVI處理器單元都會配備8個RISCV處理器核心和32到128 Kbyte的RAM,以及另外的一些加速器。整個加速芯片的功耗為31-40W,單個核心的功耗為24mW,最大的吞吐量是0.4TIPS,內(nèi)存帶寬能夠達到2.5TB/s。同一個芯片中的核心集群之間都會相互連接,芯片和外部的I/O端口的通信是通過HOPLITE路由連接到一個NOC(片上網(wǎng)絡)來實現(xiàn)的,NOC節(jié)點之間的數(shù)據(jù)通信速度可達100Gbps,HOPLITE路由是一個經(jīng)過FPGA優(yōu)化的定向路由,是專門為2D環(huán)形網(wǎng)絡所設計的,如圖2所示。

圖.2 一個400MHz的4*6*256 Hoplite NoC,100 Gb/s links

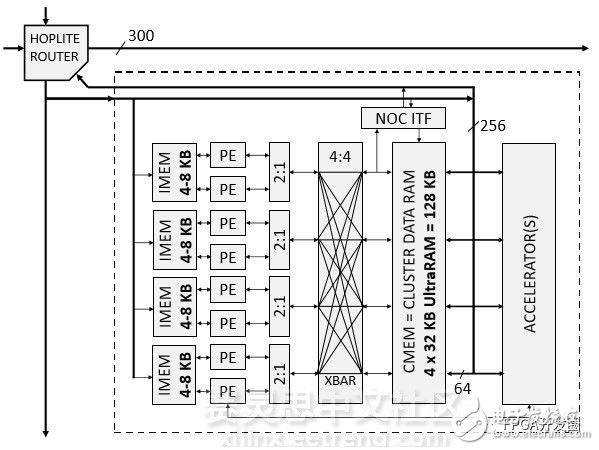

GRVI Phalanx集群單元如圖3所示,軟件部分需要有多線程的C++的編譯器,信息傳遞的執(zhí)行時間在RISC-V的RV321MA GCC編譯器中分層排布,為的是在將來的計劃中支持像OpenCL,P4和其他的一些編程工具。

圖.3 GRVI Phalanx集群

還有其他的案例,擁有80個核心的GRVI Phalanx被實例化到可編程的Zynq Z-7020 SOC中,此案例是在Digilent PYNQ-Z1開發(fā)板中作為教學所用的一種。

更令人驚喜的是,硬件開發(fā)云端的出現(xiàn),讓硬件設計人員不用買昂貴的開發(fā)板也可以進行開發(fā)工作,只需要動動自己觸手可及的鼠標和鍵盤,通過亞馬遜的平臺:Amazon AWS EC2 F1.2XL and F1.16XL instances,找到相關的Verilog芯片開發(fā)代碼就可以進行自己的創(chuàng)作了。

總結(jié)

數(shù)據(jù)中心的加速器要從軟件和硬件上同時進行,軟件是要有加速算法,需要考慮算法的可移植性和穩(wěn)定性;硬件方面可以使用文中分析的多核處理器的解決方案,當然要考慮軟件移植性、編譯工具的易用性、硬件本身的設計困難和硬件的性能、功耗、易維護性等方面。Xilinx的FPGA在數(shù)據(jù)中心的并行運算中扮演著一個重要的角色。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602022 -

Xilinx

+關注

關注

71文章

2164瀏覽量

121039

原文標題:驚呆! 數(shù)據(jù)中心加速神器---1680核處理器+FPGA !

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

機器學習實戰(zhàn):GNN加速器的FPGA解決方案

GRVI Phalanx實現(xiàn)千核處理器

數(shù)據(jù)中心加速器也許會是FPGA最高的細分市場

FPGA預計是數(shù)據(jù)中心加速器市場中年均增長率最高的細分市場

AI加速器能不能實現(xiàn)綠色數(shù)據(jù)中心

Rapanda流加速器-實時流式FPGA加速器解決方案

Alveo U30數(shù)據(jù)中心加速器卡數(shù)據(jù)手冊

Alveo U200和U250數(shù)據(jù)中心加速器卡數(shù)據(jù)手冊

Alveo U50數(shù)據(jù)中心加速器卡數(shù)據(jù)手冊

Alveo數(shù)據(jù)中心加速器卡入門指南

Alveo U280 ES1數(shù)據(jù)中心加速器卡用戶指南

Alveo U50數(shù)據(jù)中心加速器卡安裝指南

數(shù)據(jù)中心加速器就看GRVI Phalanx FPGA加速器

數(shù)據(jù)中心加速器就看GRVI Phalanx FPGA加速器

評論