CMOS晶體管,全稱為互補(bǔ)金屬氧化物半導(dǎo)體晶體管,是現(xiàn)代電子設(shè)備中不可或缺的組成部分,尤其在計(jì)算機(jī)處理器和集成電路制造中扮演著核心角色。

一、CMOS晶體管的工作原理

CMOS晶體管的工作原理基于互補(bǔ)金屬氧化物半導(dǎo)體技術(shù),它利用N型(n-channel Metal-Oxide-Semiconductor, NMOS)和P型(p-channel Metal-Oxide-Semiconductor, PMOS)金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管(MOSFET)的互補(bǔ)特性來(lái)實(shí)現(xiàn)低功耗的邏輯功能。

1. NMOS與PMOS的基本工作原理

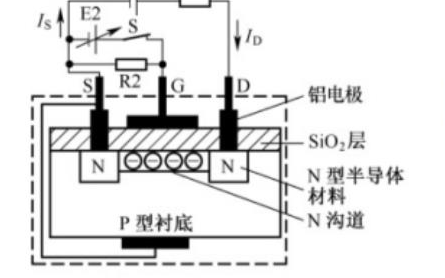

- NMOS晶體管 :NMOS晶體管在P型硅襯底上制造,其源極和漏極摻雜有n型材料(如磷),形成n+區(qū)。柵極則通過(guò)一層薄薄的二氧化硅絕緣層與硅襯底隔離。當(dāng)柵極電壓高于源極電壓時(shí),柵極下方的P型硅表面會(huì)形成一層n型反型層(也稱為導(dǎo)電溝道),允許電子從源極流向漏極,晶體管處于導(dǎo)通狀態(tài)。反之,若柵極電壓低于源極電壓,則無(wú)法形成導(dǎo)電溝道,晶體管截止。

- PMOS晶體管 :與NMOS相反,PMOS晶體管在N型硅襯底上制造,其源極和漏極摻雜有p型材料(如硼),形成p+區(qū)。同樣,柵極也通過(guò)二氧化硅絕緣層與硅襯底隔離。當(dāng)柵極電壓低于漏極電壓時(shí),柵極下方的N型硅表面會(huì)形成一層p型反型層,允許空穴從源極流向漏極,晶體管導(dǎo)通。若柵極電壓高于漏極電壓,則晶體管截止。

2. 互補(bǔ)工作原理

CMOS技術(shù)的核心在于NMOS和PMOS晶體管的互補(bǔ)性。在CMOS電路中,這兩種晶體管通常以推挽形式(Push-Pull Configuration)工作,即一個(gè)晶體管導(dǎo)通時(shí),另一個(gè)晶體管截止,反之亦然。這種互補(bǔ)性使得CMOS電路在靜態(tài)狀態(tài)下(即無(wú)輸入變化時(shí))幾乎不消耗功率,因?yàn)榇藭r(shí)只有一個(gè)晶體管處于導(dǎo)通狀態(tài),而另一個(gè)晶體管處于截止?fàn)顟B(tài),兩者之間幾乎沒(méi)有電流流動(dòng)。

3. 邏輯門(mén)的工作原理

CMOS技術(shù)廣泛應(yīng)用于構(gòu)建各種邏輯門(mén),如反相器(NOT門(mén))、與門(mén)(AND門(mén))、或門(mén)(OR門(mén))等。以反相器為例,它是最簡(jiǎn)單的CMOS邏輯電路之一,由一個(gè)NMOS和一個(gè)PMOS晶體管并聯(lián)組成。當(dāng)輸入信號(hào)為低電平時(shí)(如0V),NMOS晶體管導(dǎo)通,PMOS晶體管截止,輸出端呈現(xiàn)高電平(如VDD)。反之,當(dāng)輸入信號(hào)為高電平時(shí),PMOS晶體管導(dǎo)通,NMOS晶體管截止,輸出端呈現(xiàn)低電平。這種互補(bǔ)的工作方式實(shí)現(xiàn)了邏輯上的“非”運(yùn)算。

二、CMOS晶體管的結(jié)構(gòu)

CMOS晶體管的結(jié)構(gòu)復(fù)雜而精細(xì),涉及多個(gè)層次和工藝步驟。以下將從材料、器件結(jié)構(gòu)和制造工藝三個(gè)方面進(jìn)行詳細(xì)介紹。

1. 材料

CMOS晶體管主要使用硅(Si)作為基底材料,并通過(guò)摻雜不同的雜質(zhì)來(lái)形成n型和p型半導(dǎo)體區(qū)域。此外,柵極通常由導(dǎo)電的多晶硅制成,而柵極與硅基底之間則通過(guò)一層薄薄的二氧化硅作為絕緣層。這些材料的選擇和組合對(duì)于CMOS晶體管的性能至關(guān)重要。

2. 器件結(jié)構(gòu)

CMOS晶體管的器件結(jié)構(gòu)主要包括源極、漏極、柵極和襯底四個(gè)部分。其中,源極和漏極是電流流動(dòng)的起點(diǎn)和終點(diǎn),柵極則通過(guò)控制導(dǎo)電溝道的形成與否來(lái)控制電流的流動(dòng)。在NMOS晶體管中,源極和漏極為n+區(qū),而柵極則通過(guò)絕緣層與P型硅襯底隔離。在PMOS晶體管中,源極和漏極為p+區(qū),柵極同樣通過(guò)絕緣層與N型硅襯底隔離。

3. 制造工藝

CMOS晶體管的制造是一個(gè)復(fù)雜而精細(xì)的過(guò)程,涉及多個(gè)步驟和工藝。以下是一個(gè)簡(jiǎn)化的制造工藝流程:

- 襯底準(zhǔn)備 :首先選擇合適的硅襯底,并進(jìn)行清洗和預(yù)處理。

- 摻雜形成源極和漏極 :通過(guò)離子注入或擴(kuò)散等工藝在硅襯底上形成n+或p+區(qū)作為源極和漏極。

- 柵極氧化 :在硅襯底表面沉積一層薄薄的二氧化硅作為柵極絕緣層。

- 多晶硅沉積 :在柵極氧化層上沉積一層多晶硅作為柵極材料。

- 圖形化 :通過(guò)光刻和蝕刻等工藝將多晶硅層和柵極氧化層圖形化為所需的柵極形狀。

- 源極和漏極金屬化 :在源極和漏極區(qū)域沉積金屬層以形成電連接。

- 后續(xù)工藝 :包括互連線的形成、保護(hù)層的沉積以及測(cè)試等步驟。

在整個(gè)制造過(guò)程中,需要嚴(yán)格控制工藝參數(shù)和環(huán)境條件以確保CMOS晶體管的性能和質(zhì)量。例如,柵極氧化層的厚度和均勻性對(duì)晶體管的閾值電壓和漏電流等參數(shù)有重要影響;多晶硅柵極的摻雜濃度和形狀則會(huì)影響晶體管的開(kāi)關(guān)速度和功耗等性能。

三、CMOS晶體管的優(yōu)勢(shì)與應(yīng)用

CMOS晶體管以其低功耗、高集成度、高可靠性和可擴(kuò)展性等優(yōu)勢(shì)在現(xiàn)代電子設(shè)備中得到了廣泛應(yīng)用。以下是CMOS晶體管的主要優(yōu)勢(shì)和應(yīng)用領(lǐng)域:

1. 低功耗

由于CMOS電路在靜態(tài)狀態(tài)下幾乎不消耗功率,僅在狀態(tài)變化時(shí)才消耗能量,因此具有極低的功耗特性。這使得CMOS技術(shù)成為便攜式電子設(shè)備(如智能手機(jī)、平板電腦等)和可穿戴設(shè)備的理想選擇。

2. 高集成度

CMOS技術(shù)允許在小尺寸芯片上集成大量晶體管,從而實(shí)現(xiàn)復(fù)雜的電路功能。這種高集成度特性使得CMOS技術(shù)在計(jì)算機(jī)處理器、存儲(chǔ)器和其他集成電路制造中占據(jù)主導(dǎo)地位。

3. 高可靠性

CMOS電路具有較高的可靠性和穩(wěn)定性,能夠在惡劣的環(huán)境條件下正常工作。這使得CMOS技術(shù)在航空航天、汽車電子和醫(yī)療設(shè)備等對(duì)可靠性要求極高的領(lǐng)域中得到廣泛應(yīng)用。

4. 可擴(kuò)展性

隨著半導(dǎo)體工藝的不斷進(jìn)步和發(fā)展,CMOS技術(shù)能夠不斷縮小晶體管尺寸并提高性能。這種可擴(kuò)展性使得CMOS技術(shù)在未來(lái)仍然具有廣闊的發(fā)展前景和應(yīng)用空間。

四、總結(jié)

CMOS晶體管作為現(xiàn)代電子設(shè)備中的核心元件之一,其工作原理和結(jié)構(gòu)基于獨(dú)特的半導(dǎo)體技術(shù)和材料科學(xué)。通過(guò)NMOS和PMOS晶體管的互補(bǔ)性工作方式以及復(fù)雜的制造工藝流程,CMOS晶體管實(shí)現(xiàn)了低功耗、高集成度、高可靠性和可擴(kuò)展性等優(yōu)勢(shì)特性。這些特性使得CMOS技術(shù)在計(jì)算機(jī)處理器、存儲(chǔ)器、便攜式電子設(shè)備和可穿戴設(shè)備等領(lǐng)域中得到了廣泛應(yīng)用,并推動(dòng)了電子技術(shù)的不斷發(fā)展和進(jìn)步。未來(lái)隨著半導(dǎo)體工藝的不斷進(jìn)步和發(fā)展,CMOS技術(shù)將繼續(xù)保持其領(lǐng)先地位并推動(dòng)電子技術(shù)的進(jìn)一步革新和發(fā)展。

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27023瀏覽量

216350 -

晶體管

+關(guān)注

關(guān)注

77文章

9635瀏覽量

137854 -

CMOS晶體管

+關(guān)注

關(guān)注

0文章

11瀏覽量

10206

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

MOS場(chǎng)效應(yīng)晶體管的結(jié)構(gòu)_工作原理

MOS場(chǎng)效應(yīng)晶體管的結(jié)構(gòu)_工作原理

晶體管工作原理

PNP晶體管的工作原理,如何識(shí)別PNP晶體管

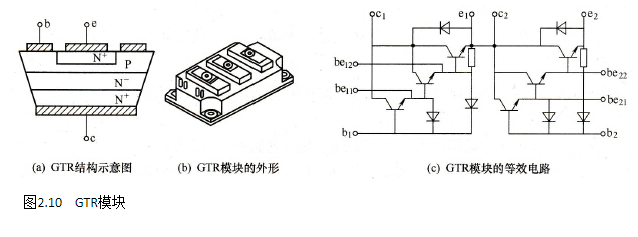

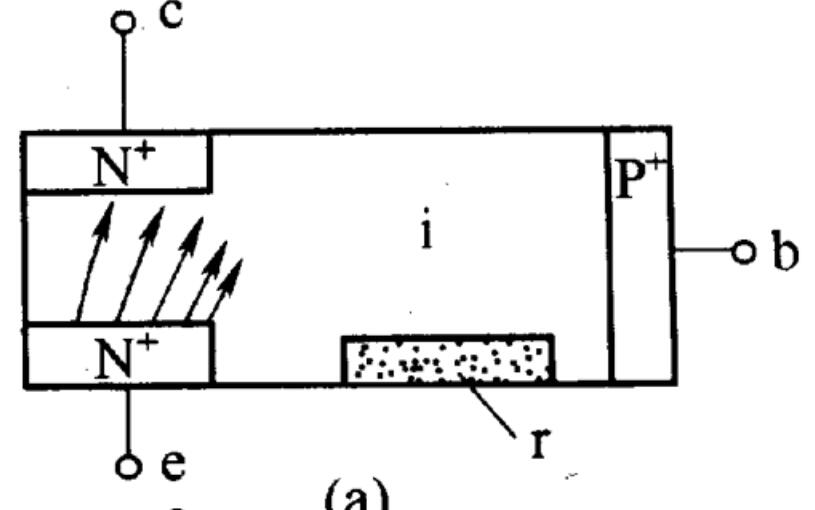

電力晶體管工作原理和結(jié)構(gòu)

CMOS晶體管,CMOS晶體管是什么意思

晶體管發(fā)明的重要性_晶體管的作用_晶體管工作原理介紹

晶體管的工作原理

電力晶體管結(jié)構(gòu)和工作原理

MOS晶體管結(jié)構(gòu)與CMOS單元電路與版圖闡述

晶體管的工作原理介紹

芯片內(nèi)部晶體管的工作原理

CMOS晶體管的工作原理和結(jié)構(gòu)

CMOS晶體管的工作原理和結(jié)構(gòu)

評(píng)論