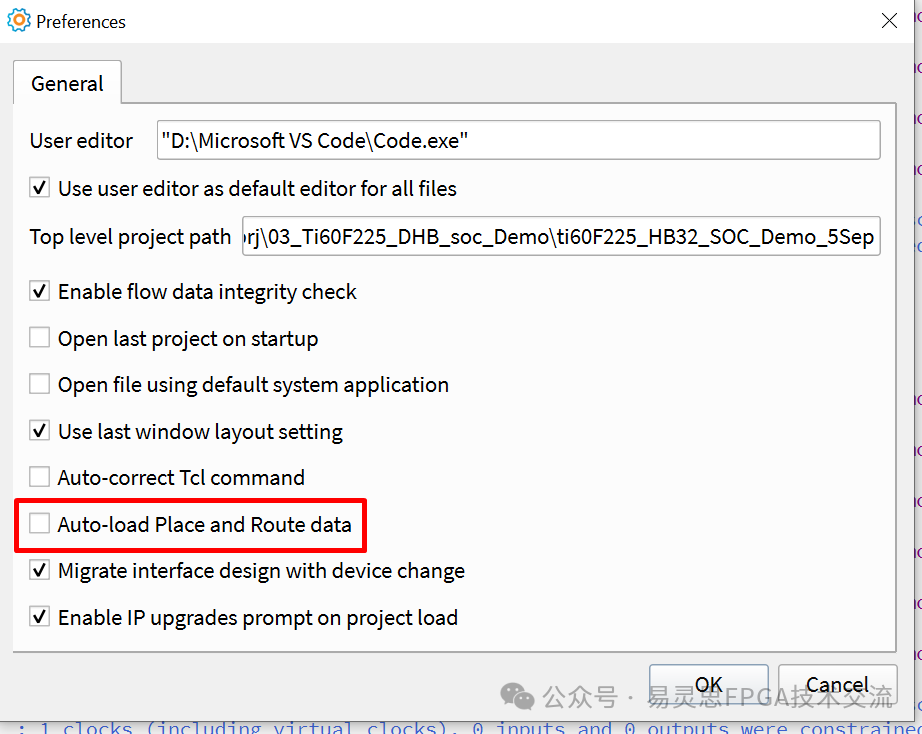

為了節省每層導入網表的時間,在設置中我們通常不會勾選Aoto Load place and route Data 前面的勾選框。這樣每次編譯完成之后Show/Hide Tcl Command Console菜單項是灰色的。

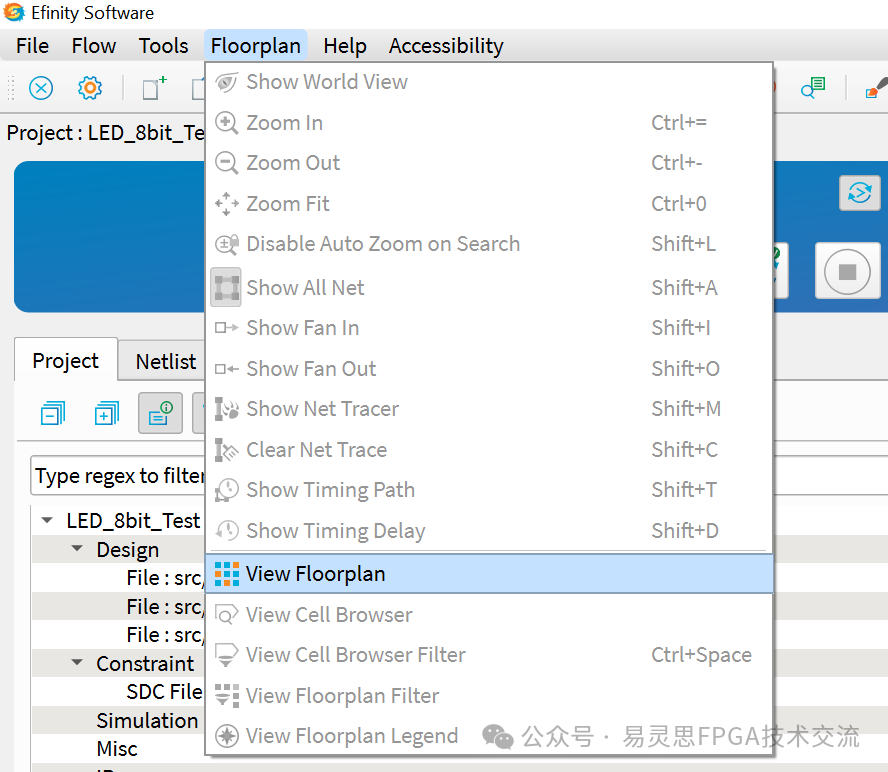

第一步要先加載見表數據。Floorplan-->View Floorplan。

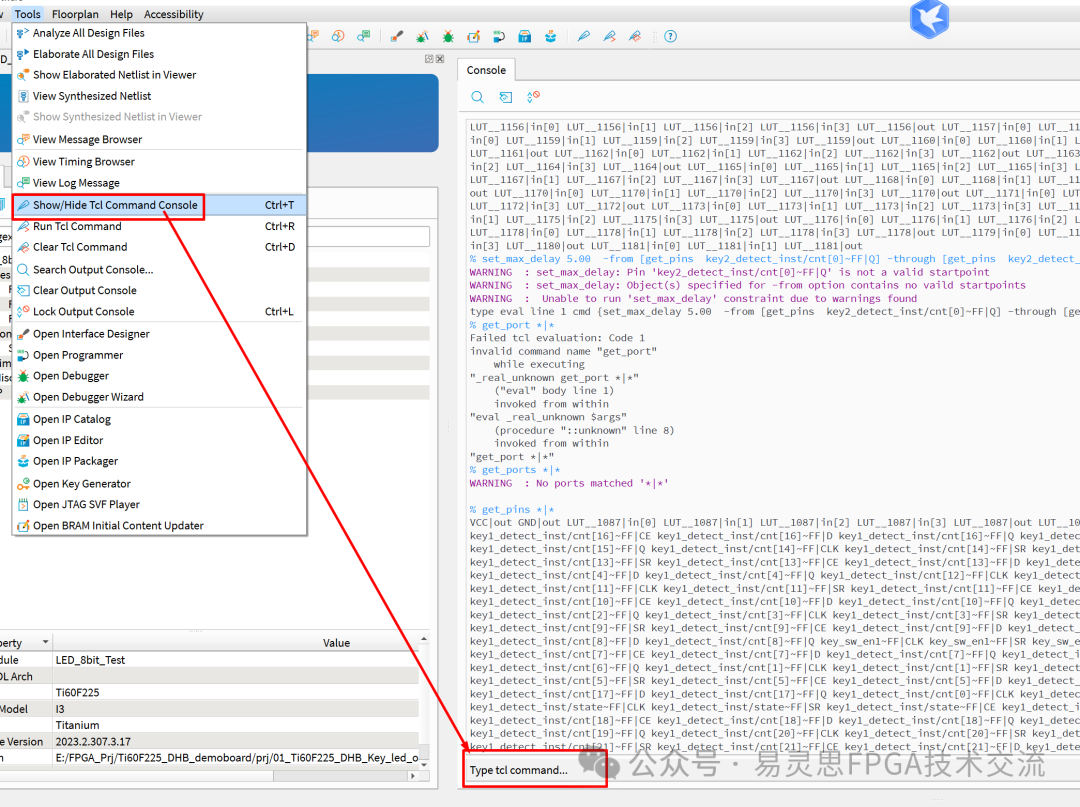

這時再次打開Tools--> Show/Hide Tcl Command Console,在Console最下面就會出現命令輸入框。

TCL操作命名

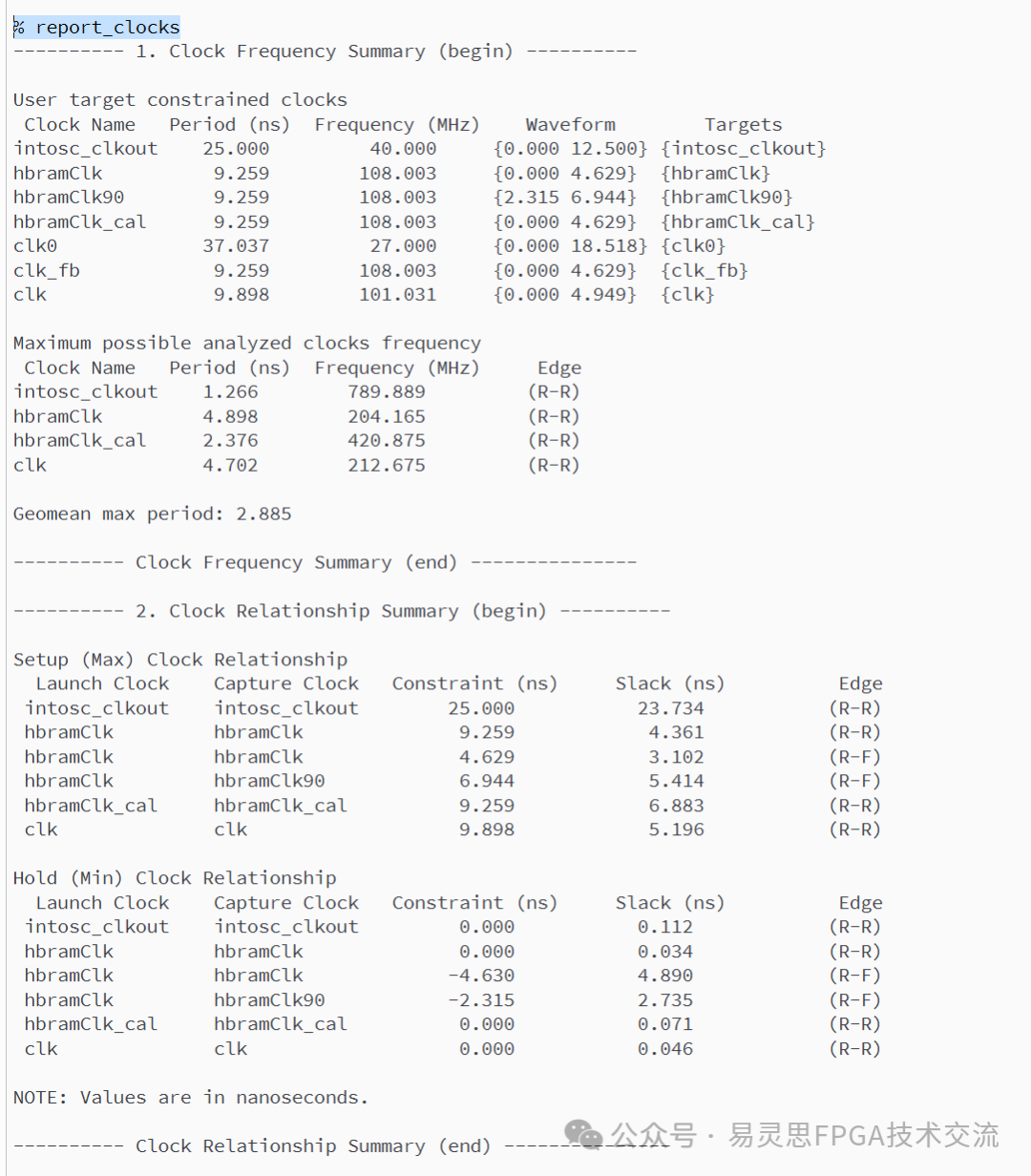

report_clocks會報告所有的時鐘關系

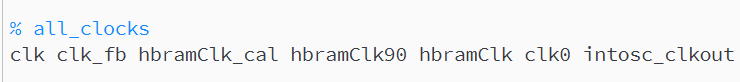

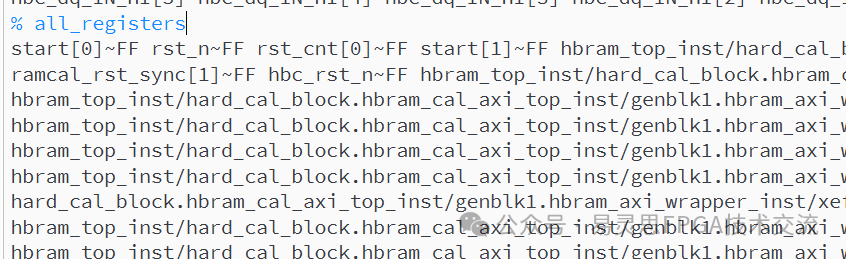

all_clocks 把系統使用的時鐘報告出來

all_inputs/all_outputs 可以查看輸入輸出端口

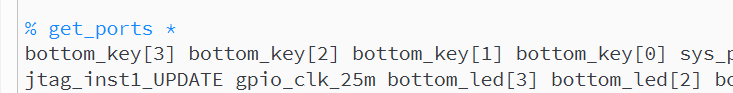

get_ports*

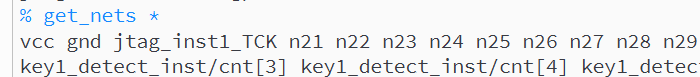

get_nets *

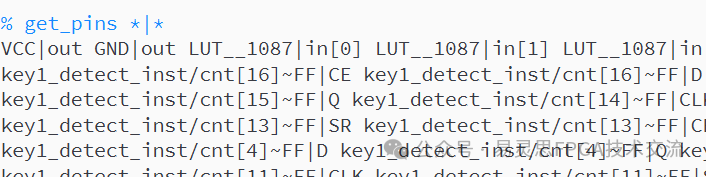

get_pins *|*

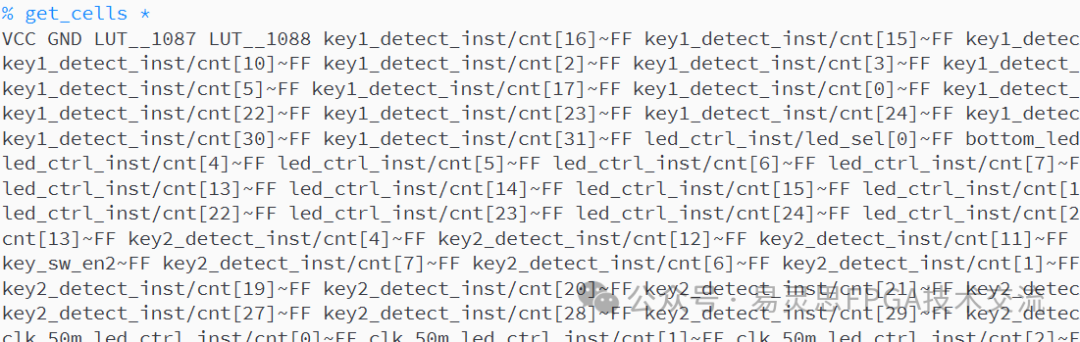

get cells *

===========================================

set_max_delay(set_min_delay)

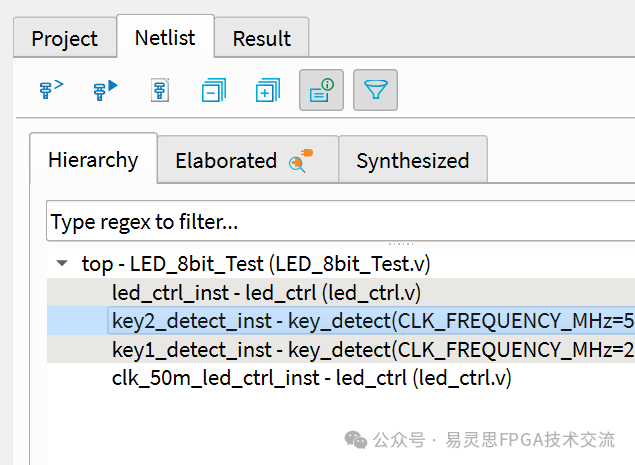

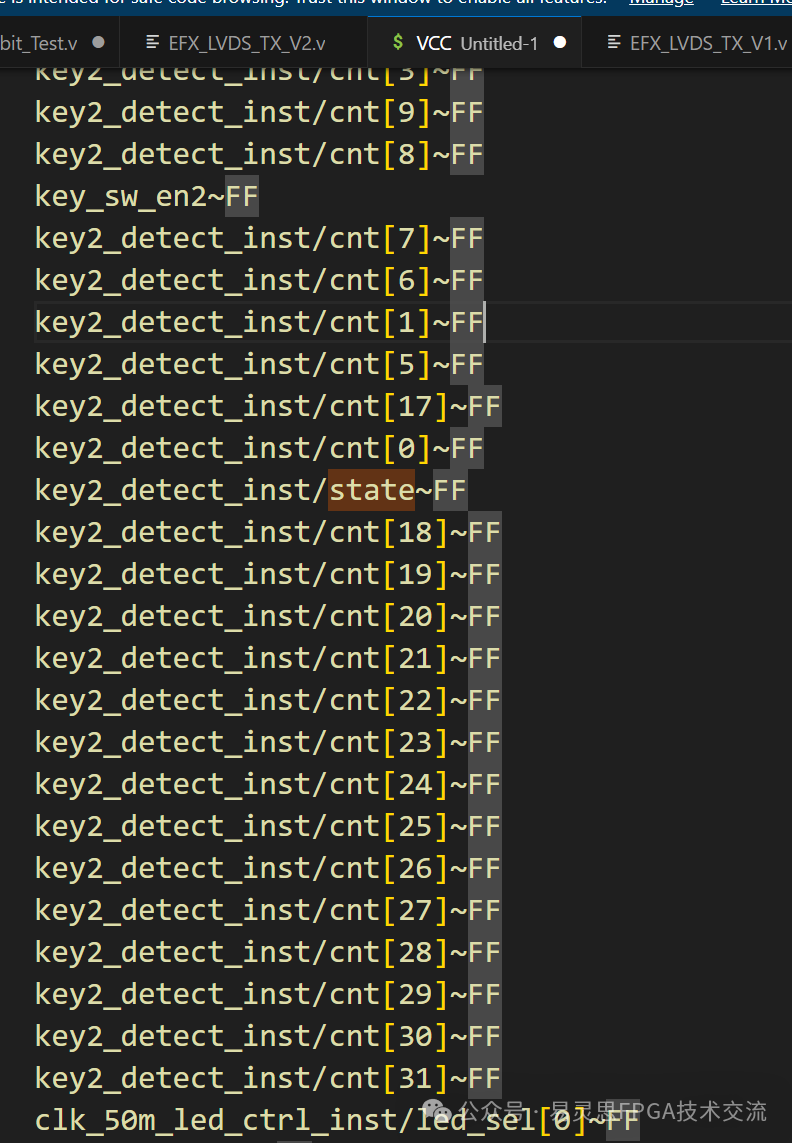

首先看到文件的層次結構是下面的

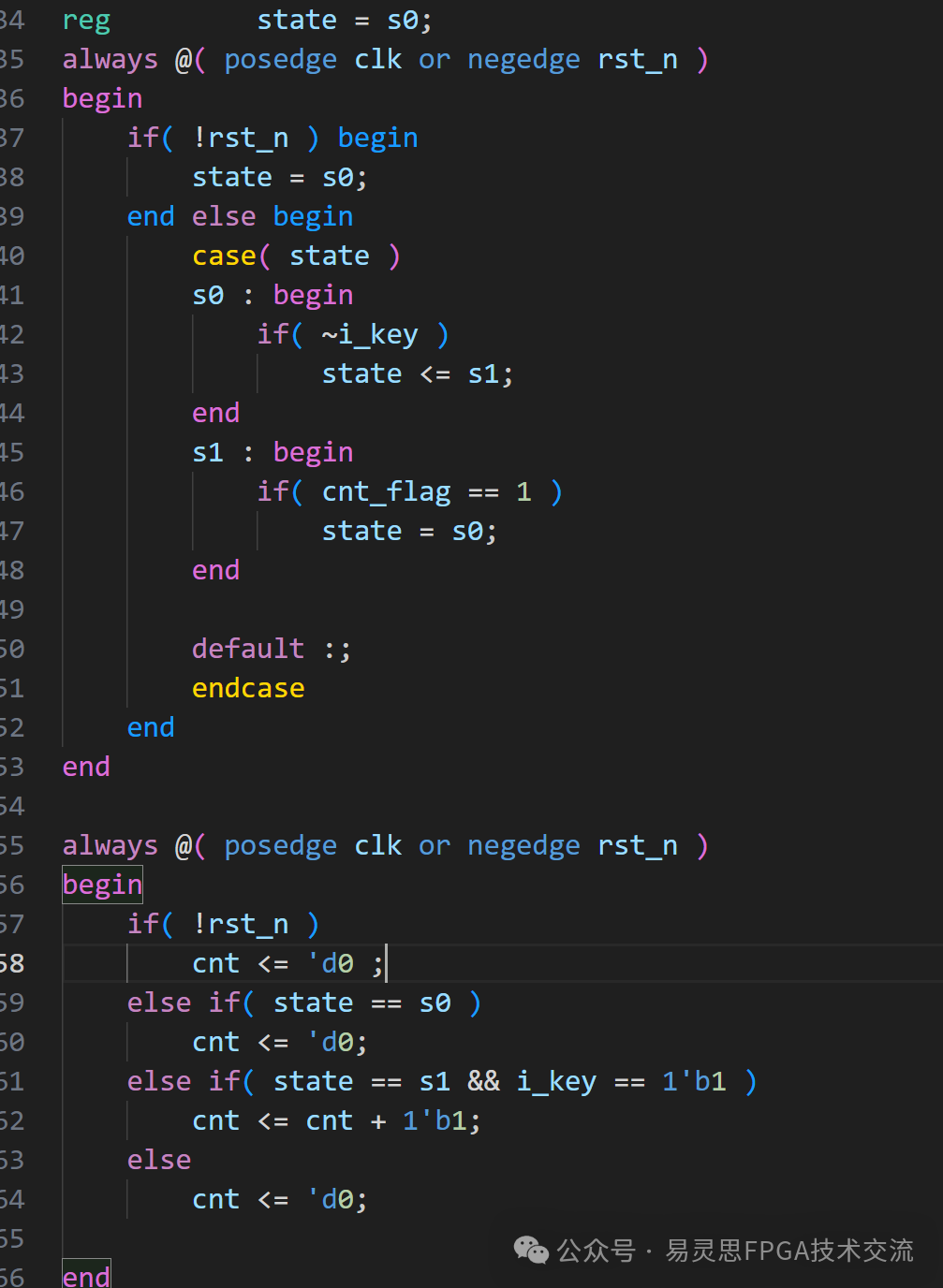

路徑在key2_detect_isnt中。代碼如下,如果我們想看state到cnt的路徑

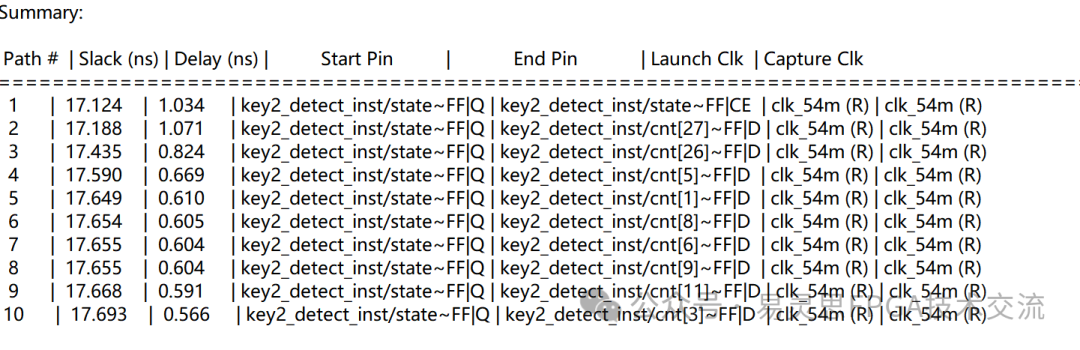

打印10條路徑,以第一條為例

report_timing -from key2_detect_inst/state* -file timing_test.txt -npaths 10

通過get_cells打印所有的cells,并通過空格轉回車清晰顯示。

% get_cellskey2_detect_inst/state~FF

key2_detect_inst/state~FF

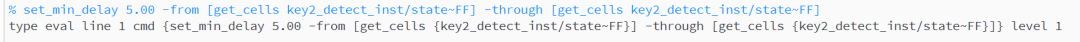

為了防止約束失敗,我們在Tcl輸入框中驗證,沒有告警或者錯誤說明約束的寫法是正確的

set_max_delay 5.00 -from [get_cells key2_detect_inst/state~FF] -through [get_cells key2_detect_inst/state~FF]

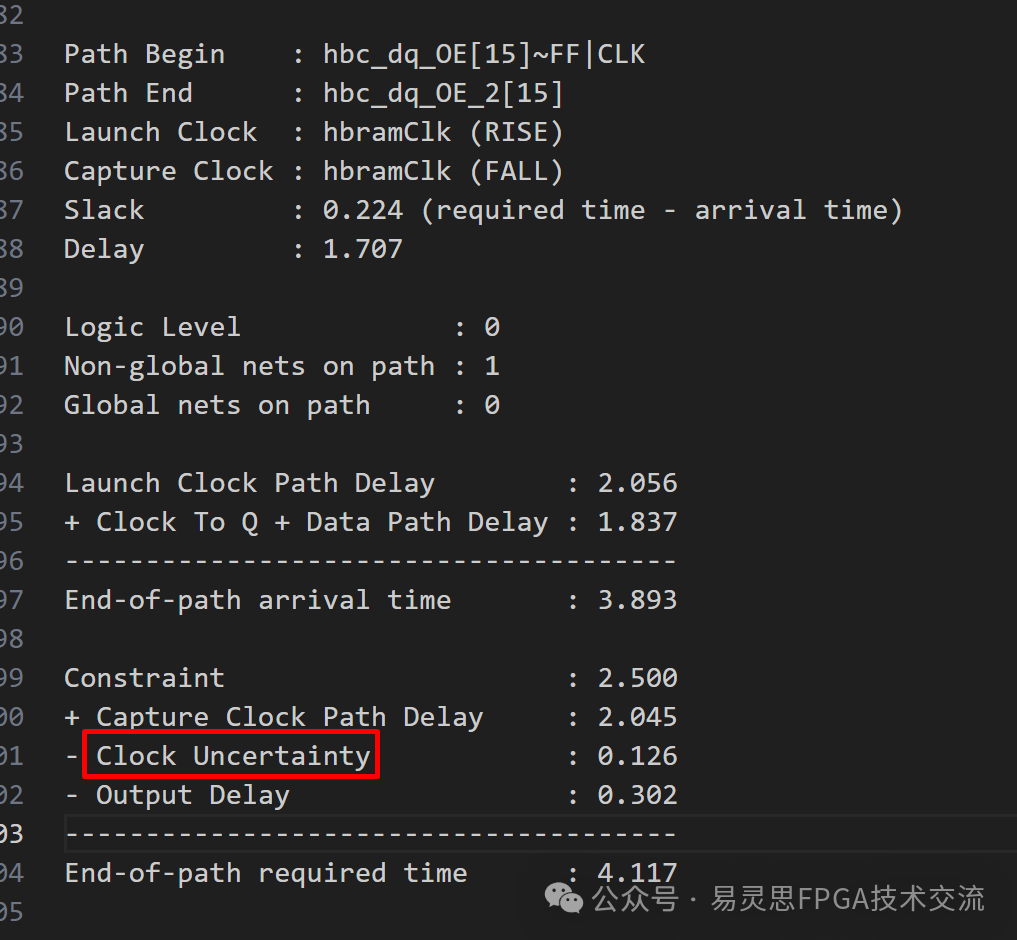

Set Clock Uncertainty

器件本身對Uncertainty是有默認的約束值的。打開timing.rpt文件就可以看到相應的約束值。

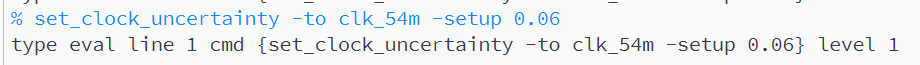

我們可以通過set_clock_uncertainty加大約束值,以上面為例,默認是120ps的uncertainty,通過下面的約束之后變成了180ps。

set_clock_uncertainty -to clk -setup 0.06

-

FPGA

+關注

關注

1626文章

21669瀏覽量

601866

發布評論請先 登錄

相關推薦

MHMF082L1V1-MINAS A6N系列通用型使用說明書 (綜合篇) 松下

MHMF082L1V1-MINAS A6系列通用型使用說明書 (安全注意指南) 松下

MHMF041L1V1-MINAS A6N系列通用型使用說明書 (綜合篇) 松下

MHMF041L1V1-MINAS A6系列通用型使用說明書 (綜合篇) 松下

MHMF022L1V1-MINAS A6N系列通用型使用說明書 (綜合篇) 松下

MHMF022L1V1-MINAS A6系列通用型使用說明書 (綜合篇) 松下

MHMF021L1V1-MINAS A6N系列通用型使用說明書 (綜合篇) 松下

MHMF021L1V1-MINAS A6系列通用型使用說明書 (綜合篇) 松下

MHMF011L1V1-MINAS A6系列通用型使用說明書 (安全注意指南) 松下

常用時序約束使用說明-v1

常用時序約束使用說明-v1

評論